# **RTQ2820A**

# 20A, 17V, ACOT<sup>®</sup> High-Efficiency Synchronous Step-Down Converter

### **1** General Description

The RTQ2820A is a high-performance, synchronous step-down converter that can deliver up to 20A output current with a wide input supply voltage range of 3.5V to 17V. The device integrates low RDS(ON) power MOSFETs, an accurate 0.6V  $\pm$  1% reference over the full operating junction temperature range, and an integrated diode for the bootstrap circuit, offering a very compact solution.

The RTQ2820A adopts Advanced Constant-On-Time (ACOT<sup>®</sup>) control architecture that provides excellent transient performance and reduces the count of external components. In steady states, the ACOT<sup>®</sup> can operate at nearly constant switching frequency over line, load and output voltage ranges, making the EMI filter design easier.

The device offers a variety of functions to provide more design flexibility. The selectable switching frequency, current limit level, PWM operation modes make the RTQ2820A easy-to-use over wide application range. An independent enable control input pin and power-good indicator are also provided for easy sequence control. The device provides a programmable soft-start-up by an external capacitor connected to the SS/TR pin to control the inrush current during start-up.

The RTQ2820A provides complete protection functions including input undervoltage lockout, output undervoltage protection, output overvoltage protection, overcurrent protection, and thermal shutdown. The RTQ2820A is available in a thermally enhanced WQFN-21TL 3x4 (FC) package.

The recommended junction temperature range is  $-40^{\circ}$ C to  $150^{\circ}$ C.

### 2 Features

- Wide Input Voltage Range

- 2.7V to 17V with External 3.3V VCC Bias

- 3.5V to 17V with Internal VCC Bias

- Output Voltage from 0.6V to 5.5V

- 0.6V ± 0.5% Voltage Reference from 0°C to 70°C Junction Temperature Range

- 0.6V ± 1% Voltage Reference from –40°C to 150°C Junction Temperature Range

- ACOT<sup>®</sup> Control for Excellent Transient Performance

- Stable with Ceramic Output Capacitors

- Selectable FCCM or PSM Operation at Light Load

- Selectable Operation Switching Frequency (600KHz/800KHz/1MHz)

- Non-Latch for OCP, UVP, UVLO, and OTP Faults, Latch Off for OVP

- Differential Remote Sense Voltage for High

Output Accuracy

- Power-Good Indicator

- Enable Control

- Programmable Soft-Start Time with a Default 1ms

- Programmable Valley Current Limit Level

- Monotonic Start-Up into Pre-Biased Outputs

- Output Voltage Tracking

- Small 21T-Lead WQFN (3x4) (FC) Package

### **3** Applications

• Servers, Storage, and Network Equipment

is a registered trademark of Richtek Technology Corporation.

• Telecom Infrastructure

RICHTEK

- Point of Load (POL) Power Modules

- High Density DC-DC Converters

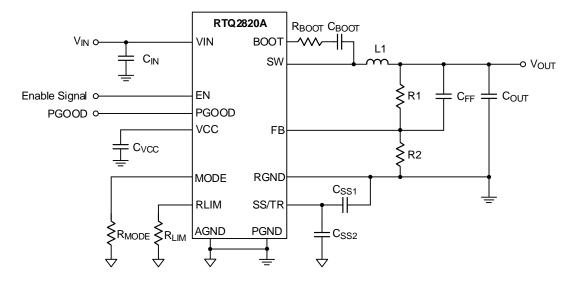

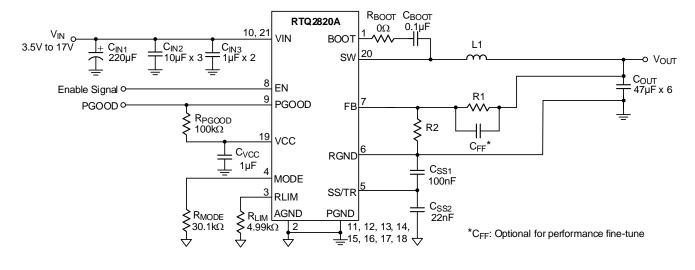

### **4 Simplified Application Circuit**

### **5** Ordering Information

RTQ2820A

Package Type QWF: WQFN-21TL 3x4 (FC) (W-Type) Lead Plating System G: Richtek Green Policy Compliant <sup>(1)</sup>

#### Note 1.

Marked with <sup>(1)</sup> indicated: Richtek products are Richtek Green Policy compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

### 6 Marking Information

0N=: Product Code YMDAN: Date Code

### **Table of Contents**

| 1  | Genera  | al Description                       | 1  |

|----|---------|--------------------------------------|----|

| 2  | Feature | es                                   | 1  |

| 3  |         | ations                               |    |

| 4  | Simplif | ied Application Circuit              | 2  |

| 5  | Orderii | ng Information                       | 2  |

| 6  |         | g Information                        |    |

| 7  | Pin Co  | nfiguration                          | 4  |

| 8  | Functio | onal Pin Description                 | 4  |

| 9  |         | onal Block Diagram                   |    |

| 10 |         | te Maximum Ratings                   |    |

| 11 |         | atings                               |    |

| 12 |         | mended Operating Conditions          |    |

| 13 |         | al Information                       | -  |

| 14 |         | cal Characteristics                  | -  |

| 15 |         | Application Circuit                  |    |

| 16 |         | Operating Characteristics            |    |

| 17 | -       | ion                                  |    |

|    | 17.1    | Power and Bias Supply                |    |

|    | 17.2    | Enable, Start-Up, Shutdown, and UVLO | 25 |

|    | 17.3    | Output Voltage Tracking and External |    |

|    |         | Reference                            |    |

|    | 17.4    | Pre-Bias                             |    |

|    | 17.5    | Minimum On-Time and Minimum Off-Tin  |    |

|    | 17.6    | Mode Selection, Switching Frequency  |    |

|    | 17.7    | Light Load Operation                 |    |

|    | 17.8    | BOOT UVLO                            |    |

|    | 17.9    | Power-Good Output                    |    |

|    | 17.10   | Overcurrent Limit                    | 29 |

|    | 17.11   | Output Undervoltage Protection     | 30      |

|----|---------|------------------------------------|---------|

|    | 17.12   | Negative Current Limit             | 31      |

|    | 17.13   | Output Overvoltage Protection      | 31      |

|    | 17.14   | Output Quick Discharge Mode        | 33      |

|    | 17.15   | Output Voltage Discharge           | 33      |

|    | 17.16   | Over-Temperature Protection (OTP)  | 33      |

| 18 | Applica | ation Information                  | 34      |

|    | 18.1    | Switching Frequency and MODE Selec | tion.34 |

|    | 18.2    | Inductor Selection                 | 34      |

|    | 18.3    | Input Capacitor Selection          | 35      |

|    | 18.4    | Output Capacitor Selection         |         |

|    | 18.5    | Internal VCC Regulator             |         |

|    | 18.6    | Bootstrap Driver Supply            |         |

|    | 18.7    | Output Voltage Programming         |         |

|    | 18.8    | Feedforward Capacitor (CFF)        | 38      |

|    | 18.9    | Enable and Adjustable UVLO         | 39      |

|    | 18.10   | Thermal Considerations             | 41      |

|    | 18.11   | PCB Layout Considerations          | 42      |

| 19 | Outline | e Dimension                        | 44      |

| 20 | Footpr  | int Information                    | 45      |

| 21 | Packin  | g Information                      |         |

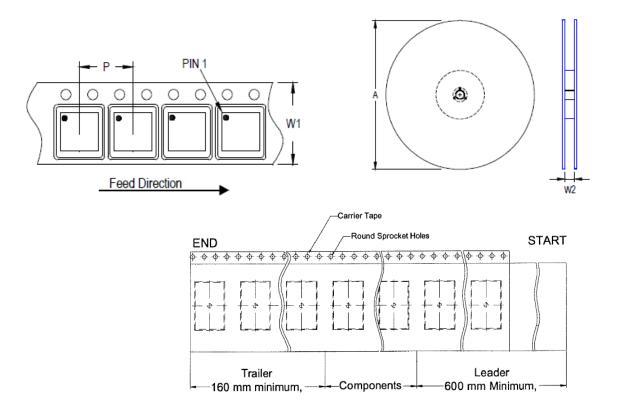

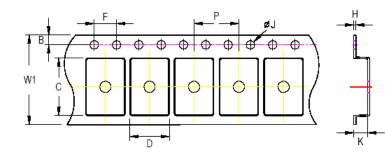

|    | 21.1    | Tape and Reel Data                 | 46      |

|    | 21.2    | Tape and Reel Packing              | 47      |

|    | 21.3    | Packing Material Anti-ESD Property | 48      |

| 22 | Datash  | eet Revision History               | 49      |

|    |         |                                    |         |

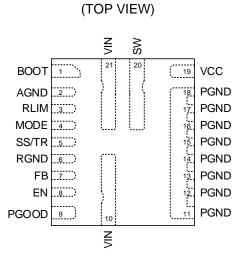

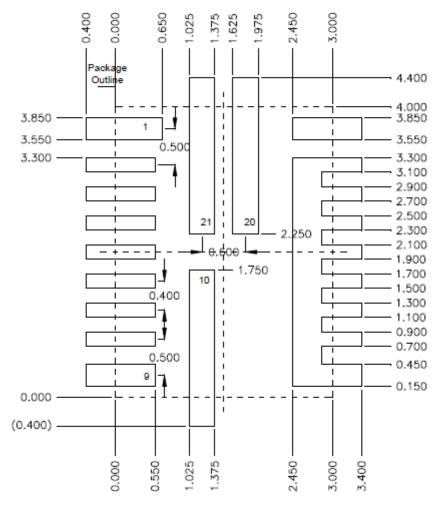

### 7 Pin Configuration

WQFN-21TL 3x4 (FC)

### 8 Functional Pin Description

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | BOOT     | Bootstrap capacitor connection node to supply the high-side gate driver. Connect a $0.1\mu$ F, X7R ceramic capacitor between this pin and SW pin.                                                                                                                                                                                                                                                                                          |

| 2       | AGND     | Analog ground. Reference point for the internal control circuit. Connect AGND and PGND with a short trace and at only one point to reduce circulating currents.                                                                                                                                                                                                                                                                            |

| 3       | RLIM     | Valley current limit setup pin. Connect a resistor from this pin to AGND to set the valley current limit value. At least $\pm$ 1% resistor is required.                                                                                                                                                                                                                                                                                    |

| 4       | MODE     | Mode selection setup pin. The mode pin can be set to force continuous-conduction mode (FCCM) or pulse skipping mode (PSM) for high light-load efficiency, and the operation switching frequency. At least $\pm 1\%$ resistor is required.                                                                                                                                                                                                  |

| 5       | SS/TR    | Soft-start and tracking control input. Connect a ceramic capacitor from this pin to RGND to program the soft-start time. The internal minimum start-up time is 1 ms (typ.). A minimum capacitor of 22nF on this pin is required for smooth charging. For the tracking function, the device can track the pin voltage as the reference for tracking applications because the SS/TR pin voltage can override the internal V <sub>REF</sub> . |

| 6       | RGND     | Differential remote voltage sense. Connect this pin to the negative side of the remote voltage sense point. Short to GND as internal reference if the remote voltage sense is not used.                                                                                                                                                                                                                                                    |

| 7       | FB       | Feedback voltage input. The pin is used to set the converter's output voltage via a resistor divider. It is suggested to place the feedback resistor divider as close to the FB pin as possible.                                                                                                                                                                                                                                           |

| 8       | EN       | Enable control input. A logic-high enables the converter; however, a logic-low forces the device into shutdown mode. Do not leave this pin floating.                                                                                                                                                                                                                                                                                       |

| 9       | PGOOD    | Open-drain, power-good indication output. It is pulled low if the feedback voltage is out of the PGOOD threshold, IC shuts down from fault state and EN goes low, and before the soft-start is finished. A pull-up resistor of $10k\Omega$ to $100k\Omega$ is recommended if this function is used.                                                                                                                                        |

| Pin No.                          | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10, 21                           | VIN      | Power input voltage. Support 3.5V to 17V input voltage. It is suggested to place decoupling input capacitors on each side of the IC and as close to the VIN and PGND pins as possible.                                                                                                                                                         |

| 11, 12, 13<br>14, 15, 16, 17, 18 | PGND     | The power GND of the controller circuit and the regulated output voltage. Use wide PCB traces to make the connections.                                                                                                                                                                                                                         |

| 19                               | VCC      | $3V$ internal LDO output. An external DC voltage source $3.3V\pm5\%$ can be connected to this pin for less power losses on the internal LDO and supply both the internal circuitry and gate driver. Connect a $1\mu F,$ X7R ceramic capacitor as close to the VCC pin as possible. It is not recommended to connect VCC to supply other rails. |

| 20                               | SW       | Switch node. Output switching state between high-side MOSFET switching<br>and low-side MOSFET switching of the power converter. Connect SW pin to<br>the external inductor and bootstrap capacitor.                                                                                                                                            |

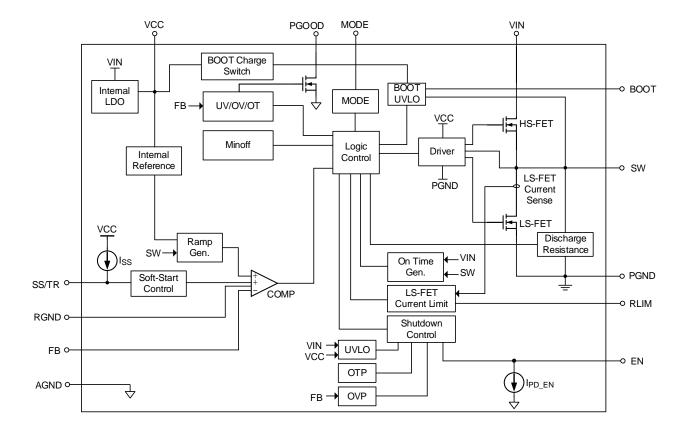

### 9 Functional Block Diagram

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

www.richtek.com

### **10 Absolute Maximum Ratings**

#### (<u>Note 2</u>)

| <ul> <li>VIN Voltage, VIN0.3V to 18V</li> </ul>                 |

|-----------------------------------------------------------------|

| Enable Pin Voltage, VEN0.3V to 18V                              |

| • VIN to SW0.3V to 18V                                          |

| VIN to Vsw (t $\leq 25 ns)$                                     |

| • SW Voltage, Vsw0.3V to 18V                                    |

| Vsw (t $\leq$ 25ns) –5V to 25V                                  |

| • BOOT Voltage, VBOOT0.3V to 24V                                |

| • BOOT to SW Voltage (VBOOT-VSW)                                |

| • VCC 6V                                                        |

| All Other Pins0.3V to 6V                                        |

| <ul> <li>Lead Temperature (Soldering, 10 sec.) 260°C</li> </ul> |

| <ul> <li>Junction Temperature 170°C</li> </ul>                  |

| • Storage Temperature Range65°C to 170°C                        |

**Note 2**. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### **11 ESD Ratings**

### (<u>Note 3</u>)

• ESD Susceptibility

| HBM ( | Human Body | Model) | ) | 2kV |

|-------|------------|--------|---|-----|

|-------|------------|--------|---|-----|

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

### **12 Recommended Operating Conditions**

#### (<u>Note 4</u>)

| <ul> <li>VIN with Internal VCC Bias, VIN</li> </ul> | 3.5V to 17V    |

|-----------------------------------------------------|----------------|

| • VIN with External 3.3V VCC Bias, V <sub>IN</sub>  | 2.7V to 17V    |

| Output Voltage                                      | 0.6V to 5.5V   |

| • External VCC bias, V <sub>CC_EXT</sub>            | 3.12V to 3.6V  |

| Enable voltage, Ven                                 | 3.6V           |

| Junction Temperature Range                          | –40°C to 150°C |

| • Junction Temperature Range                        | -40°C to 150°C |

Note 4. The device is not guaranteed to function outside its operating conditions.

RICHTEK

### **13 Thermal Information**

#### (Note 5 and Note 6)

|                     | WQFN 21TL 3x4                                               | Unit  |      |  |

|---------------------|-------------------------------------------------------------|-------|------|--|

| θja                 | θJA Junction-to-ambient thermal resistance (JEDEC standard) |       |      |  |

| hetaJC(Top)         | Junction-to-case (top) thermal resistance                   | 21.6  | °C/W |  |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance                | 1.2   | °C/W |  |

| θJA(EVB)            | Junction-to-ambient thermal resistance (specific EVB)       | 20.44 | °C/W |  |

| ΨJC(Top)            | Junction-to-top characterization parameter                  | 0.43  | °C/W |  |

| ΨЈВ                 | Junction-to-board characterization parameter                | 9.11  | °C/W |  |

Note 5. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

Note 6.  $\theta_{JA(EVB)}$ ,  $\Psi_{JC(TOP)}$  and  $\Psi_{JB}$  are measured on a high effective-thermal-conductivity four-layer test board which is in size of 80mm x 85mm; furthermore, all layers with 2 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

### **14 Electrical Characteristics**

(V<sub>IN</sub> = 12V,  $T_J$  = -40°C to 150°C, typical values are at  $T_J$  = 25°C, unless otherwise specified.)

| Parameter                             | Parameter Symbol Test Conditions |                                                                             | Min   | Тур  | Max   | Unit |  |

|---------------------------------------|----------------------------------|-----------------------------------------------------------------------------|-------|------|-------|------|--|

| Shutdown Current                      |                                  |                                                                             |       |      |       |      |  |

| Shutdown Current                      | ISHDN                            | VEN = 0V                                                                    |       | 5    | 15    | μA   |  |

| Supply Current<br>(Non-Switching)     | IQ_NSW                           | V <sub>EN</sub> = 2V, non-switching                                         |       | 1150 | 1300  | μA   |  |

| Logic Threshold                       |                                  |                                                                             |       |      |       |      |  |

| EN Input Voltage Rising<br>Threshold  | Ven_r                            |                                                                             | 1.17  | 1.22 | 1.27  | V    |  |

| EN Threshold Hysteresis               | VEN_HYS                          |                                                                             |       | 200  |       | mV   |  |

| EN Pull-Down Current                  | IPD_EN                           | VEN = 2V                                                                    |       | 0.5  | 5     | μA   |  |

| Reference Voltage                     |                                  |                                                                             |       |      |       |      |  |

| Internal Reference                    |                                  | $T_J = -40^{\circ}C$ to +150°C                                              | 0.594 | 0.6  | 0.606 | V    |  |

| Voltage                               | Vref                             | $T_J = 0^{\circ}C$ to +70°C                                                 | 0.597 | 0.6  | 0.603 |      |  |

| Soft-Start and Tracking               |                                  |                                                                             |       |      |       |      |  |

| Internal Soft-Start Time              | tss                              | TJ = 25°C, CSS1 = 1nF and CSS2 = 22nF, VOUT is 0% to 100% ( <u>Note 7</u> ) |       | 1    | 1.4   | ms   |  |

| SS/TR Charge Current                  | ISS/TR_CHG                       | $V_{SS/TR} = 0V$                                                            |       | 42   |       | μΑ   |  |

| SS/TR Discharge Current               | ISS/TR_DISCHG                    | VSS/TR = 1V                                                                 |       | 12   |       | μA   |  |

| MOSFET                                |                                  |                                                                             |       |      |       |      |  |

| On-Resistance of High-<br>side MOSFET | Rdson_H                          | $T_J = 25^{\circ}C, V_{CC} = 3V$                                            |       | 8.6  |       |      |  |

| On-Resistance of Low-<br>side MOSFET  | RDSON_L                          | $T_J = 25^{\circ}C$ , $V_{CC} = 3V$                                         |       | 2.5  |       | mΩ   |  |

| Current Limit                         |                                  |                                                                             |       |      |       |      |  |

| Current Limit Voltage<br>Threshold    | VLIM                             | TJ = 25°C, valley current                                                   |       | 1.2  |       | V    |  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                                              | Symbol             | Test Conditions                                       | Min  | Tur              | Max  | Unit  |

|--------------------------------------------------------|--------------------|-------------------------------------------------------|------|------------------|------|-------|

| Ics to IOUT Ratio                                      |                    | I est Conditions                                      |      | <b>Typ</b><br>10 |      |       |

| Low-Side Switch (Valley)                               | Gcs (Ics/Iout)     | $T_J = 25^{\circ}C$ , valley current,                 |      | 10               |      | μΑ/Α  |

| Current Limit                                          | ILIM_L             | RLIM = $5k\Omega$                                     |      | 24               |      | A     |

| Low-Side MOSFET<br>Negative Current-limit<br>threshold | ILIM_NEG           | TJ = 25°C, valley current                             |      | -10              |      | А     |

| Switching Frequency                                    |                    |                                                       |      |                  |      |       |

|                                                        |                    | $R_{MODE} = 0\Omega$ , IOUT = 0A, FCCM,<br>VOUT = 1V  | 480  | 600              | 720  |       |

| Switching Frequency                                    | fsw                | RMODE = $30.1$ kΩ, IOUT = 0A, FCCM,<br>VOUT = 1V      | 680  | 800              | 920  | kHz   |

|                                                        |                    | RMODE = $60.4$ kΩ, IOUT = 0A, FCCM,<br>VOUT = 1V      | 850  | 1000             | 1150 |       |

| On-Time Timer Control                                  |                    |                                                       |      |                  |      |       |

| Minimum On-Time                                        | ton_min            | TJ = 25°C ( <u>Note 7</u> )                           |      |                  | 50   | ns    |

| Minimum Off-Time                                       | toff_min           | T <sub>J</sub> = 25°C ( <u>Note 7</u> )               |      |                  | 210  | ns    |

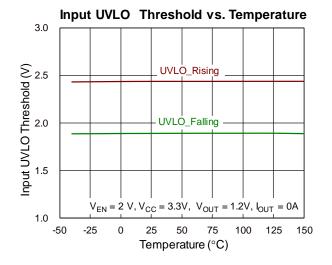

| UVLO                                                   |                    |                                                       |      |                  |      |       |

| Input Undervoltage<br>Lockout Rising Threshold         | VUVLO_R            | VIN rising, VCC_EXT = 3.3V                            | 2.1  | 2.4              | 2.7  | V     |

| Input Undervoltage<br>Lockout Hysteresis               | VUVLO_HYS          | VIN hysteresis                                        |      | 550              |      | mV    |

| LDO Output                                             |                    |                                                       |      |                  |      |       |

| LDO Output Voltage                                     | Vcc                | Ivcc = 1mA                                            | 2.88 | 3.00             | 3.18 | V     |

| VCC UVLO Rising<br>Threshold                           | Vcc_uvloh          | Vcc rising                                            | 2.65 | 2.8              | 2.95 | V     |

| VCC UVLO Hysteresis                                    | $\Delta V CC_UVLO$ | Vcc hysteresis                                        |      | 300              |      | mV    |

| VCC Load Regulation                                    |                    | Ivcc = 25mA                                           |      | 0.5              |      | %     |

| LDO Output Current Limit                               | ILIM_LDO           |                                                       |      | 105              |      | mA    |

| Output Overvoltage and                                 | Undervoltage P     | rotections                                            |      |                  |      |       |

| Output Undervoltage<br>Protection Threshold            | Vuvp               | UVP detect                                            | 77   | 80               | 83   | %Vref |

| Output Overvoltage<br>Protection Threshold             | Vovp               | OVP detect                                            | 113  | 116              | 119  | %Vref |

| Power-Good                                             |                    |                                                       |      |                  |      |       |

|                                                        | VTH_PGLH1          | VFB rising threshold, PGOOD from low to high (GOOD)   | 89.5 | 91.5             | 95.5 |       |

| Power-Good Voltage                                     | VTH_PGHL1          | VFB rising threshold, PGOOD from high to low (FAULT)  | 113  | 116              | 119  | 0/1/  |

| Threshold                                              | VTH_PGLH2          | VFB falling threshold, PGOOD from low to high (GOOD)  | 102  | 106              | 109  | %VREF |

|                                                        | VTH_PGHL2          | VFB falling threshold, PGOOD from high to low (FAULT) | 77   | 80               | 83   |       |

9

| Parameter                                                                                             | Symbol    | Test Conditions                                                                                              | Min | Тур | Max  | Unit |  |

|-------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|

| Power-Good Output Low-                                                                                | VPG_L_100 | $T_J = 25^{\circ}C$ , VIN & VCC & VEN = 0V,<br>PGOOD pull up to 3.3V bias with<br>100k resister              |     | 650 | 850  | mV   |  |

| Level Voltage                                                                                         | VPG_L_10  | $T_J = 25^{\circ}C$ , $V_{IN} \& V_{CC} \& V_{EN} = 0V$ ,<br>PGOOD pull up to 3.3V bias with<br>10k resister |     | 800 | 1000 | mV   |  |

| Power-Good Delay<br>tPGDLY<br>TJ = 25°C, VTH_PGLH1 and<br>VTH_PGLH2, PGOOD from low to<br>high (GOOD) |           | VTH_PGLH2, PGOOD from low to                                                                                 | 0.5 | 0.8 | 1.1  | ms   |  |

| Over-Temperature Prote                                                                                | ction     | ·                                                                                                            |     |     |      |      |  |

| Over-Temperature<br>Protection Threshold                                                              | Тотр      |                                                                                                              |     | 160 |      | °C   |  |

| Over-Temperature<br>Protection Hysteresis                                                             | TOTP_HYS  |                                                                                                              |     | 30  |      | °C   |  |

| Output Discharge Resistor                                                                             |           |                                                                                                              |     |     |      |      |  |

| Output Discharge<br>ResistorRDISCHGVEN = 0V or Protection                                             |           | V <sub>EN</sub> = 0V or Protection                                                                           |     | 80  | 150  | Ω    |  |

Note 7. Guaranteed by design.

### **15 Typical Application Circuit**

#### Table 1. Suggested Component Selection for the Application of 600kHz

| Vout(V) | R1 (kΩ) | R2 (kΩ) | L1 (μΗ) | Couτ_ΜΙΝ (μ <b>F)</b> | COUT_TYPICAL (µF) | CFF (pF)    |

|---------|---------|---------|---------|-----------------------|-------------------|-------------|

| 0.8     | 3.32    |         | 0.33    | 84                    | 282               | 560 to 1000 |

| 1.2     | 10      | 10      | 0.4     | 84                    | 282               | 470 to 820  |

| 3.3     | 45.3    | 10      | 1       | 84                    | 282               | 330 to 680  |

| 5       | 73.2    |         | 1.5     | 84                    | 282               | 220 to 470  |

### Table 2. Suggested Component Selection for the Application of 800kHz

| <b>Vout(V)</b> | R1 (kΩ) | R2 (kΩ) | L1 (μH) | Coυτ_ΜΙΝ (μF) | COUT_TYPICAL (µF) | Сғғ (рҒ)    |

|----------------|---------|---------|---------|---------------|-------------------|-------------|

| 0.8            | 3.32    |         | 0.22    | 84            | 282               | 560 to 1000 |

| 1.2            | 10      | 10      | 0.33    | 84            | 282               | 470 to 820  |

| 3.3            | 45.3    |         | 0.68    | 84            | 282               | 330 to 680  |

| 5              | 73.2    |         | 1       | 84            | 282               | 220 to 470  |

### Table 3. Suggested Component Selection for the Application of 1000kHz

| Vout(V) | R1 (kΩ) | R2 (kΩ) | L1 (μH) | Coυτ_ΜΙΝ (μF) | COUT_TYPICAL (µF) | CFF (pF)    |

|---------|---------|---------|---------|---------------|-------------------|-------------|

| 0.8     | 3.32    |         | 0.15    | 84            | 282               | 560 to 1000 |

| 1.2     | 10      | 10      | 0.22    | 84            | 282               | 470 to 820  |

| 3.3     | 45.3    | 10      | 0.47    | 84            | 282               | 330 to 680  |

| 5       | 73.2    |         | 0.68    | 84            | 282               | 220 to 470  |

#### Table 4. Suggested Inductors for Typical Application Circuit

| Inductance (µH) | Part No.          | ISAT (A) | DCR (mΩ) | Dimensions (mm) | Component Supplier |

|-----------------|-------------------|----------|----------|-----------------|--------------------|

| 0.15            | VLBU1007090T-R15L | 90       | 0.18     | 10 x 7 x 9      | TDK                |

| 0.22            | VLBU1007090T-R22L | 57       | 0.18     | 10 x 7 x 9      | TDK                |

| 0.33            | VLBU1007090T-R33L | 39       | 0.18     | 10 x 7 x 9      | TDK                |

| 0.4             | VLBU1007090T-R40L | 30       | 0.18     | 10 x 7 x 9      | TDK                |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

## RICHTEK

| Inductance (µH) | Part No.   | ISAT (A) | DCR (mΩ) | Dimensions (mm)   | Component Supplier |

|-----------------|------------|----------|----------|-------------------|--------------------|

| 0.47            | 7443310047 | 116.2    | 1.35     | 12.1 x 11.4 x 9.5 | WE                 |

| 0.68            | 7443310068 | 59.2     | 1.35     | 12.1 x 11.4 x 9.5 | WE                 |

| 1               | 7443310100 | 55.1     | 1.95     | 12.1 x 11.4 x 9.5 | WE                 |

| 1.5             | 7443310150 | 54.5     | 2.8      | 12.1 x 11.4 x 9.5 | WE                 |

#### Table 5. Suggested Capacitors for Typical Application Circuit

| Capacitance (µF) | Part No.           | Case Size    | Component Supplier |

|------------------|--------------------|--------------|--------------------|

| 220              | 250ARHA221M08A2    | 8mm x 11.5mm | APAQ               |

| 10               | GRM31CR71E106KA12L | 1206         | Murata             |

| 47               | GRM31CR60J476ME19  | 1206         | Murata             |

| 1                | GRM155C81E105KE11D | 0402         | Murata             |

Note 8. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC Bias.

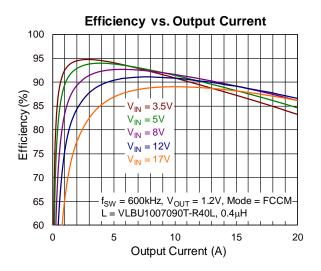

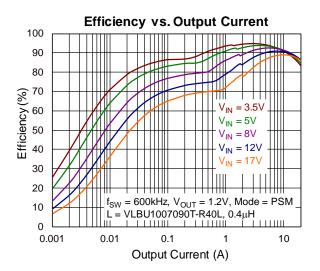

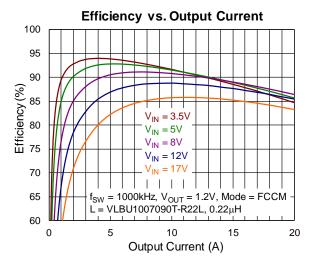

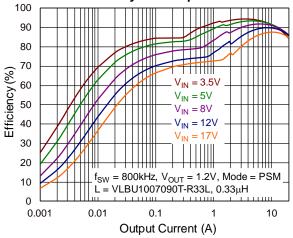

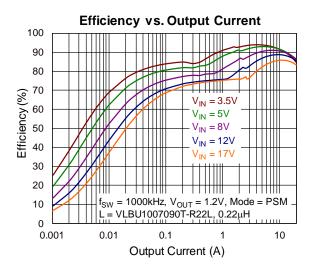

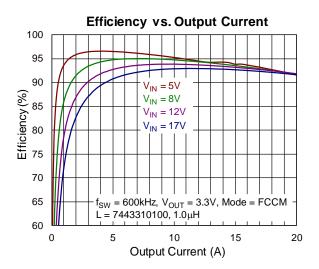

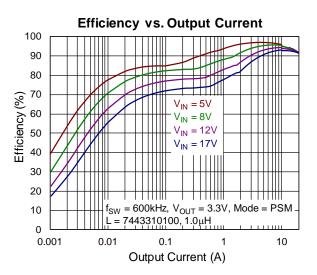

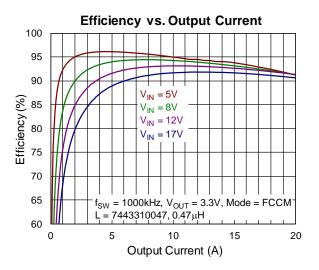

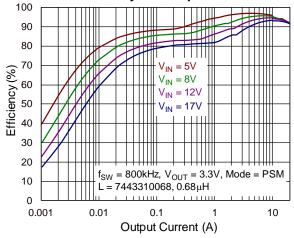

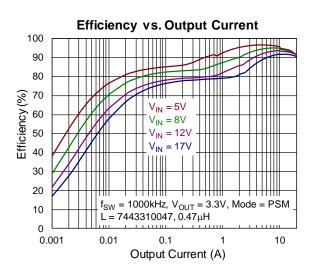

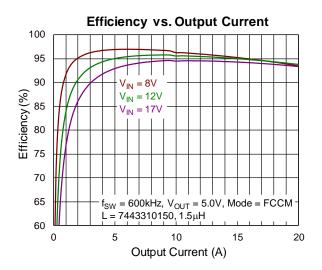

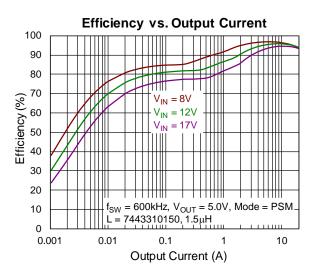

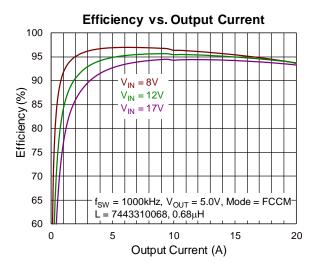

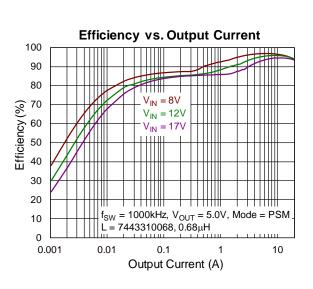

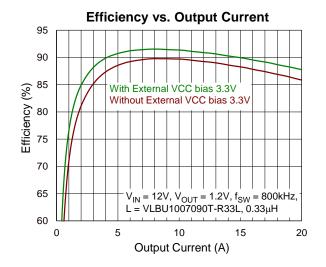

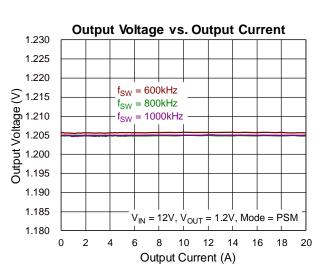

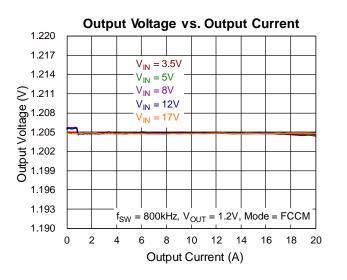

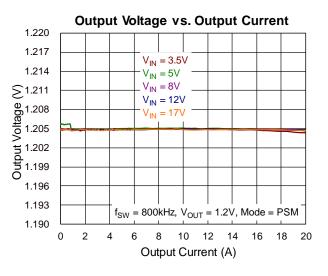

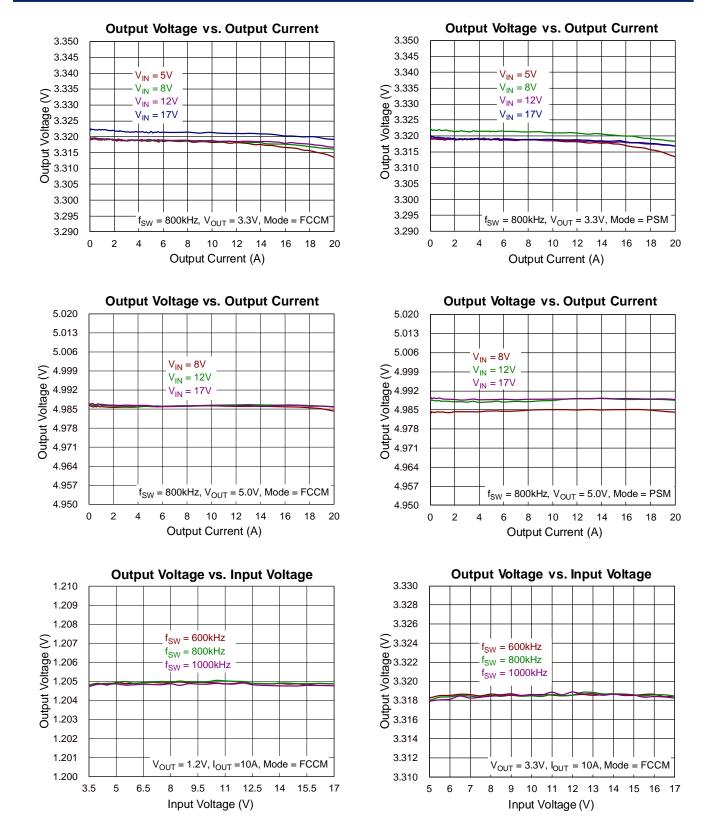

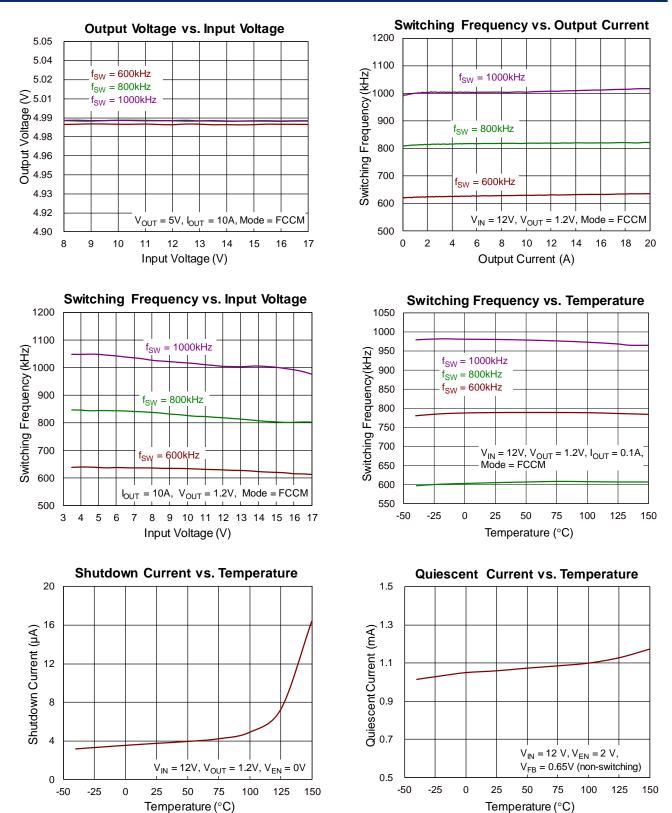

### 16 Typical Operating Characteristics

RICHTEK

Efficiency vs. Output Current 100 95 90 Efficiency (%) 85 V<sub>IN</sub> = 3.5V  $V_{IN} = 5V$ 80 V<sub>IN</sub> = 8V V<sub>IN</sub> = 12V 75 = 17V70 65 = FCCM 60 0 5 10 20 15 Output Current (A)

Efficiency vs. Output Current

### \_\_\_\_\_\_Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK

Efficiency vs. Output Current 100 95 90  $V_{IN} = 5V$ Efficiency (%)  $V_{IN} = 8V$ 85  $V_{IN} = 12V$ V<sub>IN</sub> = 17V 80 75 70 65  $f_{SW} = 800 kHz$ ,  $V_{OUT} = 3.3V$ , Mode = FCCM L = 7443310068, 0.68µH 60 0 5 20 10 15 Output Current (A)

Efficiency vs. Output Current

Copyright © 2024 Richtek Technology Corporation. All rights reserved. www.richtek.com

Efficiency vs. Output Current 100 95 90  $V_{IN} = 8V$  $V_{IN} = 12V$ Efficiency (%) 85 = 17V VIN 80 75 70 65  $f_{SW} = 800$ kHz,  $V_{OUT} = 5.0$ V, Mode = FCCM  $L = 7443310100, 1.0 \mu H$ 60 0 5 10 15 20 **Output Current (A)**

Efficiency vs. Output Current 100 90 80  $V_{IN} = 8V$ 70 Efficiency (%)  $V_{IN} = 12V$ 60 V<sub>IN</sub> = 17V 50 40 30 20  $f_{SW} = 800$ kHz,  $V_{OUT} = 5.0$ V, Mode = PSM 10 L = 7443310100, 1.0µH 0 0.001 0.01 10

0.1

Output Current (A)

1

**Output Voltage vs. Output Current** 3.350 3.345 3.340  $f_{SW} = 600 \text{kHz}$ 3.335 3.330 3.325 3.320 3.320 3.315 3.310 O 3.305 3.335  $f_{SW} = 800 \text{kHz}$  $f_{SW} = 1000 \text{kHz}$ 3.300 3.295  $V_{IN} = 12V, V_{OUT} = 3.3V, Mode = PSM$ 3.290 0 2 4 8 10 12 14 16 18 6 20 Output Current (A)

**Output Voltage vs. Output Current** 5.020 5.015 5.010 5.005  $f_{SW} = 600 \text{kHz}$ € 5.000  $f_{SW} = 800 \text{kHz}$ Output Voltage ( 4.995  $f_{SW} = 1000 kHz$ 4.990 4.985 4.980 4.975 4.970 4.965  $V_{IN} = 12V, V_{OUT} = 5.0V, Mode = PSM$ 4.960 0 2 4 6 8 10 12 14 16 18 20 Output Current (A)

RICHTEK Copyright © 2024 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

# **RTQ2820A**

Copyright © 2024 Richtek Technology Corporation. All rights reserved. DSQ2820A-00 April 2024

RICHTEK

is a registered trademark of Richtek Technology Corporation.

RICHTEK

Copyright © 2024 Richtek Technology Corporation. All rights reserved. www.richtek.com

served. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

**Reference Voltage vs. Temperature** 0.620 0.615 Reference Voltage (V) 0.610 0.605 0.600 0.595 0.590 0.585 0.580 -50 -25 0 25 50 75 100 125 150 Temperature (°C)

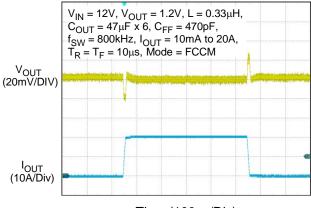

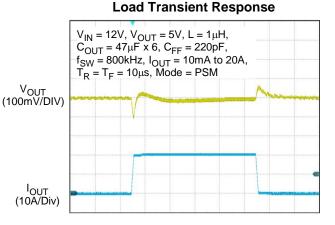

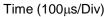

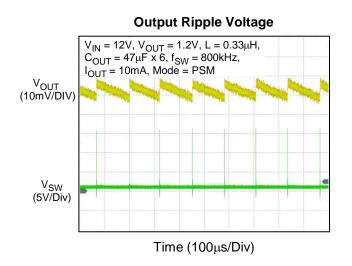

Load Transient Response

Time (100µs/Div)

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

Time (100µs/Div)

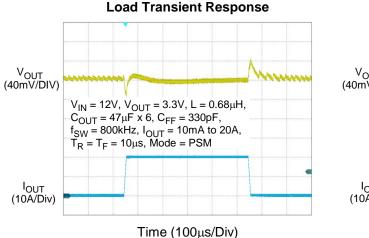

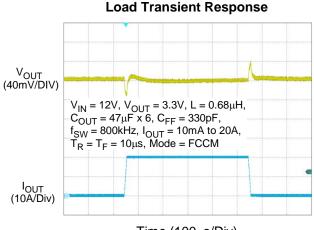

#### Load Transient Response

Time (100µs/Div)

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

Time (100µs/Div)

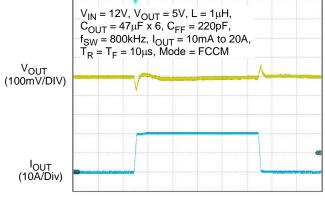

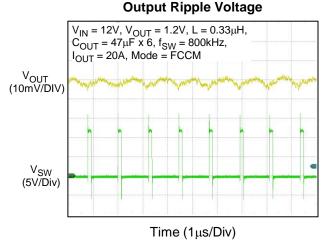

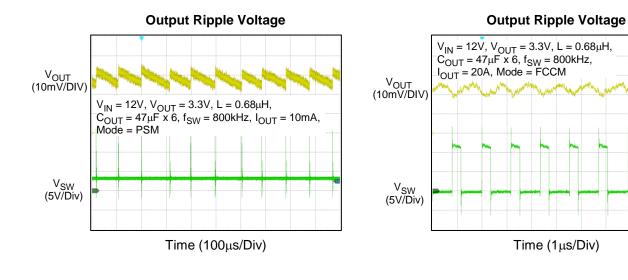

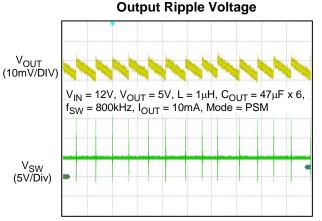

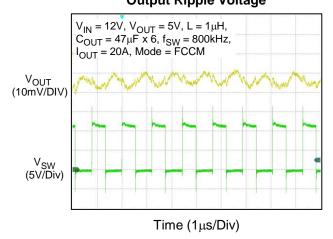

Output Ripple Voltage

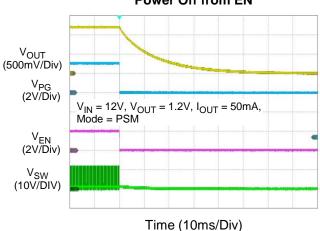

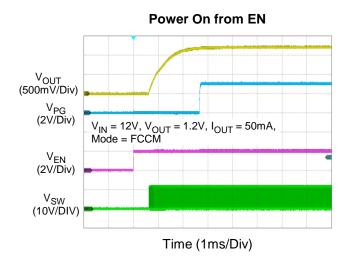

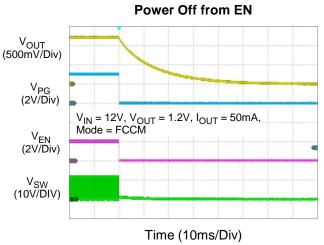

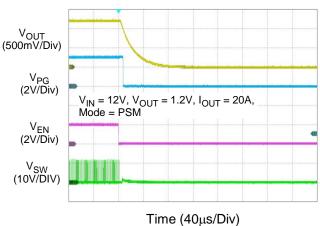

Power Off from EN

Power Off from EN

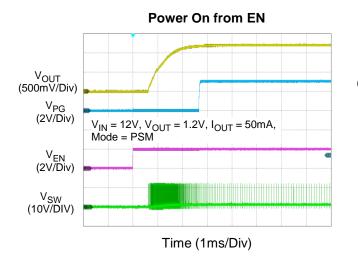

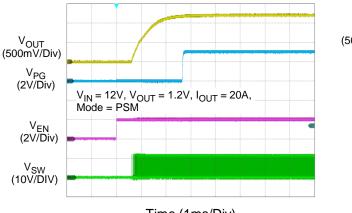

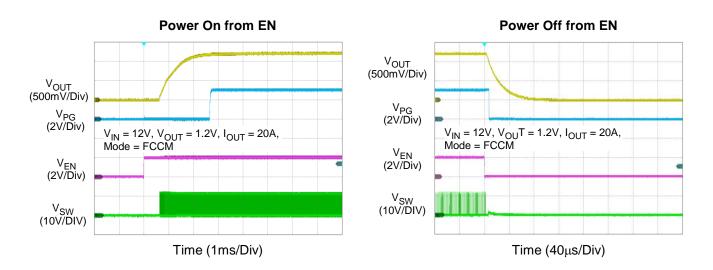

Power On from EN

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

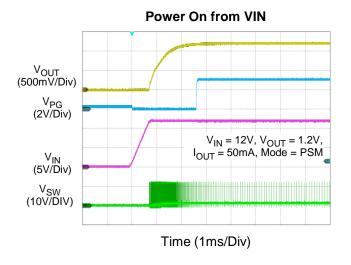

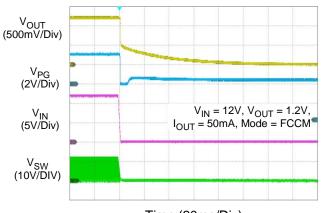

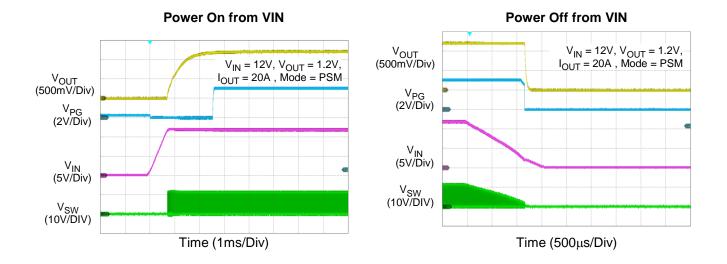

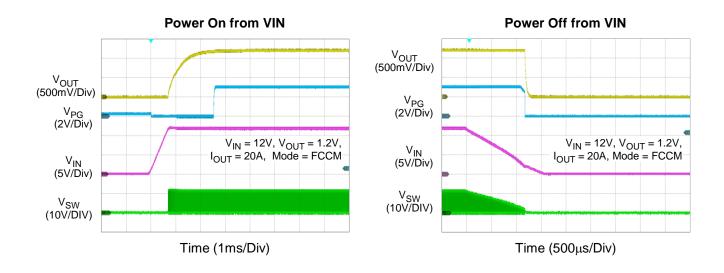

Power On from VIN  $V_{OUT}$  (500mV/Div)  $V_{PG}$  (2V/Div)  $V_{IN}$  (5V/Div)  $V_{SW}$  (10V/DIV)  $V_{SW}$  (10V/DIV)  $V_{IN}$  $V_{IN} = 12V, V_{OUT} = 1.2V, V_{OUT} = 1.2$

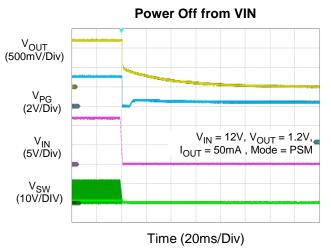

Time (20ms/Div)

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

### 17 Operation

The RTQ2820A is a high-efficiency synchronous step-down converter that utilizes the proprietary Advanced Constant-On-Time (ACOT<sup>®</sup>) control architecture. The ultrafast ACOT<sup>®</sup> control enables the use of small capacitance to reduce PCB size.

During normal operation, the internal high-side MOSFET (HS-FET) turns on for a fixed interval determined by a oneshot timer at the beginning of each clock cycle. When the high-side MOSFET turns off, the low-side MOSFET (LS-FET) turns on. Due to the output capacitor ESR, the voltage ripple on the output has a similar shape to the inductor current. Via the feedback resistor network, this voltage ripple is compared with the internal reference. When the minimum off-time one-shot (180ns, max.) has timed out and the inductor current is below the current-limit threshold, the one-shot is triggered again if the feedback voltage falls below the internal VREF (0.6V, typ.). The RTQ2820A supports stable operation with all low-ESR output capacitors (such as ceramic capacitor and low ESR polymer capacitor). The ACOT<sup>®</sup> control architecture also features excellent transient response, further improving the output variation during high-frequency load transients, especially when a load suddenly increases.

The conventional COT controller implements the on-time to be inversely proportional to input voltage and directly proportional to the output voltage to achieve pseudo-fixed frequency over the input voltage range. However, even with defined input and output voltages, a fixed ON time means that the frequency has to increase at higher load levels to compensate for the power losses in the MOSFETs and the inductor. The ACOT<sup>®</sup> control further adds a frequency locked loop system, which slowly adjusts the ON time to compensate for the power losses without influencing the fast transient behavior of the COT topology.

### 17.1 Power and Bias Supply

The VIN pins on the RTQ2820A supply voltage to the drain terminal of the internal high-side MOSFET. These pins also supply bias voltage for an internal regulator that generates 3V at the VCC pin. The voltage on the VCC pin is used for internal chip bias and gate drive for the low-side MOSFET. The gate drive for the high-side MOSFET is supplied by a floating supply (CBOOT) between the BOOT and SW pins. CBOOT is charged by an internal synchronous diode from VCC. In addition, an internal charge pump maintains that the CBOOT voltage is sufficient to turn on the high-side MOSFET.

To improve efficiency and limit power dissipation in the VIN, an external voltage that is higher than the LDO's internal output voltage can override the internal LDO. When using an external bias on the VCC rail, any power-up and power-down sequencing can be applied. However, it is important to understand that if there is a discharge path on the VCC rail that can draw a current higher than the internal LDO's current limit from the VCC, then the VCC drops below the UVLO falling threshold and cause the output of the RTQ2820A to shut down.

### 17.2 Enable, Start-Up, Shutdown, and UVLO

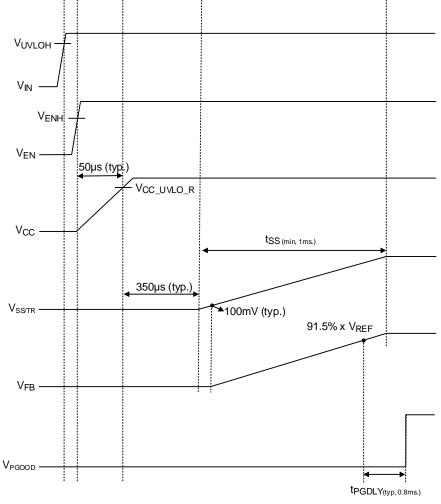

The RTQ2820A implements undervoltage lockout protection (UVLO) to prevent operation without fully turning on the internal power MOSFETs. The UVLO monitors the internal LDO regulator voltage. When the VCC voltage is lower than the UVLO threshold voltage, the device is shutdown.

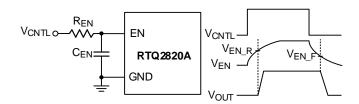

The EN pin is provided to control the device turn-on and turn-off. When the EN pin voltage is above the turn-on threshold ( $V_{EN_R}$ ), the device is enabled. When the EN pin voltage falls below the turn-off threshold ( $V_{EN_F}$ ), RTQ2820A is disabled. If the EN pin is floating, the RTQ2820A internally pulls down the EN pin continuously.

When the EN pin voltage rises above the enable threshold voltage, and V<sub>CC</sub> rises above the V<sub>CC\_UVLOH</sub>, the device enters its start-up sequence and initiates a soft-start ramp of the output voltage. An internal soft-start ramp of 1ms (typ.) will limit the ramp rate of the output voltage to prevent excessive input current during start-up. If a longer ramp time is desired, the capacitors can be placed between the SS/TR pin and both the AGND and RGND pins. Use a

22nF capacitor for Css<sub>2</sub>, and a larger value ranging from 22nF to 220nF for Css<sub>1</sub>. If this external ramp rate is slower than the internal 1ms soft-start, the output voltage will be limited by the ramp rate on the SS/TR pin instead. The typical external soft-start time from 0% to 91.5% of VREF can be calculated by the equation below.

$C_{SS1}(nF) + C_{SS2} (nF) = \frac{t_{SS}(ms) \times 42(\mu A)}{0.55V}$

where Css2 is required to be a minimum of 22nF; Css1 is recommended 22nF to 220nF

When the VEN is lower than VEN\_F, the voltage of the SS/TR pin discharges to RGND.

<u>Figure 1</u> below shows the typical power-up sequence of the device. When the voltage on the VIN and EN pins crosses the input undervoltage lockout rising threshold and EN input rising threshold. After the voltage on the VCC pin reaches the VCC undervoltage lockout rising threshold, the device will start switching if the voltage difference between the SS/TR pin and FB pin is equal to 100mV (i.e. VSS/TR – VFB = 100mV, typ.) after setting detection is completed. The SS/TR pin should never be left unconnected for soft-start control. After the VFB rises above the VTH\_PGLH1 (91.5% of the VREF, typ.), the PGOOD pin will enter a high impedance state after delay time tPGDLY (0.8ms, typ.).

Figure 1. Power-Up Sequence

### 17.3 Output Voltage Tracking and External Reference

The RTQ2820A can replace the internal voltage reference (VREF) or track an external power rail by adding an external voltage signal to the SS/TR pin. The VFB will track this signal, which ranges from 0.3 V to 1.4 V. During startup, it is essential to ensure that the SS/TR pin voltage reaches 600mV or higher for proper operation. The Power-Good Output function is activated if VREF or an external voltage signal exceeds 550mV, and it is disabled if the external voltage signal at the SS/TR pin is lower than 500mV.

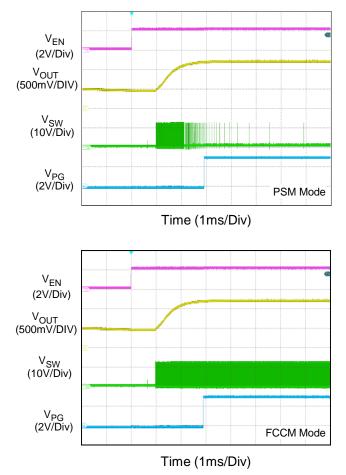

#### 17.4 Pre-Bias

If there is a residual voltage on the output voltage before startup, both the high-side and low-side MOSFETs are prohibited from switching until the internal soft-start ramp is higher than the feedback voltage. Switching will begin when the soft-start ramp crosses above the feedback voltage, and the output voltage will smoothly rise from the pre-biased level to its regulated target. Figure 2 shows an example of pre-bias start-up.

### 17.5 Minimum On-Time and Minimum Off-Time

The constraint on the operating duty cycle is determined by the minimum controllable on-time and off-time. The minimum on-time is the smallest duration of time in which the high-side MOSFET can be in its "ON" state. In continuous mode operation, the effective switching frequency will be decreased to regulate the output voltage target when the minimum on-time limits of a converter are reached. However, reducing the operating frequency will alleviate the constraint on the minimum duty cycle. The equation can be ideally estimated without resistive drop as follows.

$V_{IN}(max) \leq \frac{V_{OUT}}{f_{SW}(max) \times t_{ON\_MIN}(max)}$

Where ton\_MIN, the minimum on-time is 50ns (max).

The minimum off-time,  $t_{OFF_MIN}$ , is the smallest duration during which the RTQ2820A can turn on the low-side MOSFET, trip the current comparator, and then turn the power switch back off. The limit on minimum off-time imposes a maximum duty cycle of  $t_{ON} / (t_{ON} + t_{OFF_MIN})$ . The calculation for the minimum off-time and the minimum input voltage considering the loss terms is provided below.

$V_{IN}\left(min\right) \geq \left[\frac{V_{OUT} + I_{OUT\_MAX} \times \left(R_{DSON\_L} + DCR\right)}{1 - t_{OFF\_MIN} \left(max\right) \times f_{SW} \left(max\right)}\right] + I_{OUT\_MAX} \times \left(R_{DSON\_H} - R_{DSON\_L}\right)$

where the minimum off-time of the RTQ2820A is 210ns (max); RDSON\_H is the high-side MOSFET on resistance; RDSON\_L is the low-side MOSFET on resistance; DCR is the DC resistance of inductor.

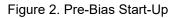

### 17.6 Mode Selection, Switching Frequency

The RTQ2820A offers three different switching frequencies of 600kHz, 800kHz and 1000kHz by setting the MODE pin voltage. The selection of the operating frequency is a tradeoff between efficiency and component size. The high-frequency operation allows the use of smaller inductors and capacitor values, while operation at lower frequencies improves efficiency by reducing internal gate charge and transition losses but requires larger inductance values and/or capacitance to maintain low output ripple voltage.

Furthermore, the RTQ2820A can also offer two modes which are force continuous-conduction mode (FCCM) and pulse skipping mode (PSM) for light load conditions to improve efficiency.

When the MODE pin is left floating, the default status will be set to 600kHz for PSM operation. Users can configure the mode and operating frequency by connecting a resistor to the AGND pin or VCC pin, as specified in <u>Table 6</u>.

| Mode Pin Connections        | Light Load Mode | Switching frequency (kHz) |  |

|-----------------------------|-----------------|---------------------------|--|

| Short to VCC                | PSM             | 600                       |  |

| 243K $\Omega$ ±10% to AGND  | PSM             | 800                       |  |

| 121K $\Omega$ ±10% to AGND  | PSM             | 1000                      |  |

| Short to AGND               | FCCM            | 600                       |  |

| 30.1K $\Omega$ ±10% to AGND | FCCM            | 800                       |  |

| 60.4K $\Omega$ ±10% to AGND | FCCM            | 1000                      |  |

Table 6. Mode Pin Selection

Figure 3. MODE Connection

### 17.7 Light Load Operation

At low load current, the inductor current can drop to zero and become negative. This condition is detected by internal zero current-detect circuitry that utilizes the low-side MOSFET RDSON\_L to sense the inductor current. The low-side MOSFET is turned off when the inductor current drops to zero, resulting in pulse skipping mode (PSM). Both power MOSFETs will remain off with the output capacitor supplying the load current until the feedback voltage falls below the internal VREF. PSM operation maintains high efficiency at light load, while setting MODE to FCCM operation helps meet tight voltage regulation accuracy requirements.

### 17.8 BOOT UVLO

The BOOT UVLO circuit is implemented to ensure a sufficient voltage of BOOT capacitor for turning on the high-side MOSFET at any conditions. The BOOT UVLO usually actives at extremely high conversion ratio or the higher VOUT application operates at very light load. With such conditions when the BOOT to SW voltage falls below VBOOT\_UVLO\_F (2.3V, typ.), the device turns on the BOOT recharge path (200ns, typ.) to charge the BOOT capacitor.

#### 17.9 Power-Good Output

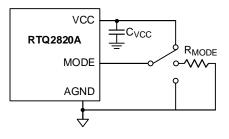

The RTQ2820A features an open-drain power-good indication which is connected to an external voltage source through a pull-up resistor. The power-good function is activated after soft-start is finished and is controlled by the feedback signal VFB. During soft-start, VPGOOD is actively held low and only allowed to become high after soft-start is finished. If VFB rises above the VTH\_PGLH1 (91.5% of the VREF, typ.), the PGOOD pin will be in high impedance and VPGOOD will be held high after a certain delay elapsed. When VFB falls below the PGOOD low threshold VTH\_PGHL2 (80% of the VREF, typ.) or exceeds VTH\_PGHL1 (116% of the VREF, typ.), the PGOOD pin will be pulled low. For VFB higher than VTH\_PGHL1, VPGOOD can be pulled high again if VFB drops back to the PGOOD high threshold VTH\_PGLH2 (106% of the VREF, typ.). Once being started-up, if any internal protection is triggered, PGOOD pin will be pulled low to GND. The internal open-drain pull-down device will pull the VPGOOD low. This is to prevent false flag operation for short excursions in output voltage, such as during line and load transients. The power-good indication profile is shown in Figure 4.

Figure 4. The Logic of PGOOD

### 17.10 Overcurrent Limit

The RTQ2820A features cycle-by-cycle current-limit protection on the low-side MOSFETs and the protection prevents the device from catastrophic damage due to in output short circuit, overcurrent, or inductor saturation.

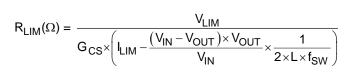

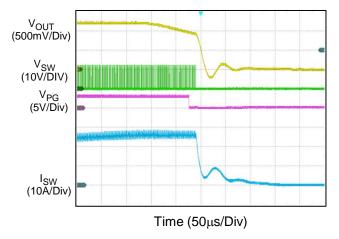

The low-side MOSFET valley current-limit protection is achieved by measuring the inductor current through the lowside MOSFET and mirroring the RLIM pin with the ratio of Gcs using a resistor during the low-side on-time. Once the inductor current through the low-side MOSFET is above the low-side MOSFET valley current-limit threshold ( $I_{LIM}_L$ ), the on-time one-shot will be inhibited until the inductor current ramps down to the  $I_{LIM}_L$ ; that is, another on-time can only be triggered when the inductor current goes below the  $I_{LIM}_L$ . Figure 5. shows an example of overcurrent protection, and the output current-limit threshold can be calculated as below:

Where VLIM =1.2V, GCs =  $10\mu$ A/A, and ILIM is the desired output current limit (A).

Figure 5. Overcurrent Protection

### 17.11 Output Undervoltage Protection

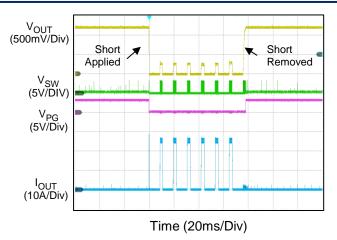

The RTQ2820A includes output undervoltage protection (UVP) against over-load or short-circuited condition by constantly monitoring the feedback voltage VFB. If VFB drops below the undervoltage protection threshold VUVP (80% of the VREF, typ.), the UV comparator will go high to turn off both the internal high-side and low-side MOSFETs. The RTQ2820A will enter output undervoltage protection with hiccup mode. During hiccup mode, the device will shut down for tHICCUP\_OFF (8.5ms, typ.), and then attempt to recover automatically for tHICCUP\_ON (2.4ms, typ.).

If the fault condition is removed, the converter will resume normal operation; otherwise, such cycle for auto-recovery will be repeated until the fault condition is cleared. Hiccup mode allows the circuit to operate safely with low input current and power dissipation, and then resumes normal operation as soon as the overload or short-circuit condition is removed. The behavior of UVP and Hiccup mode is shown in Figure 6.

Figure 6. Short-Circuit Protection and Recovery

#### 17.12 Negative Current Limit

The RTQ2820A also monitors inductor current during the "ON" state of the low-side MOSFET to prevent too large negative current flowing through the low-side MOSFET. Once the negative current exceeds the low-side switch negative current-limit threshold ILIM\_NEG (-10A, typ.), the device turns off the low-side MOSFET and turns on the high-side MOSFET for the on-time determined by VIN, VOUT and fsw. After the high-side MOSFET on-time expires, the low-side MOSFET turns on again. This behavior can keep the valley of negative current at ILIM\_NEG to protect low-side MOSFET. A designer should choose appropriate inductance to avoid triggering ILIM\_NEG during normal operation.

#### 17.13 Output Overvoltage Protection

The RTQ2820A includes an output overvoltage protection (OVP) circuit to limit output voltage and minimize output voltage overshoot. If the V<sub>FB</sub> goes above 116% of the V<sub>REF</sub>, the high-side MOSFET will be latched off and the PGOOD pin remains low until the VCC or EN is recycled. In the meantime, if the overvoltage condition still exists, the low-side MOSFET remains on to discharge output voltage until the low-side switch valley current reaches the negative current limit (I<sub>LIM\_NEG</sub>). Once reaching the I<sub>LIM\_NEG</sub> the low-side MOSFET is turned off temporarily around 700ns before it is turned on again. The RTQ2820A repeats in this cycle until the output voltage is brought down when the V<sub>FB</sub> goes below 50% of the V<sub>REF</sub>, the low-side MOSFET continues to turn on. The device needs EN or VIN to recycle to clear the OVP fault. The overvoltage protection is shown in Figure 7.

Figure 7. Overvoltage Protection

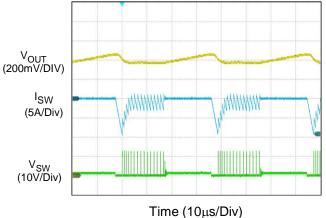

### 17.14 Output Quick Discharge Mode

The RTQ2820A features Output Quick Discharge Mode (OQDM) to mitigate overshoot before triggering the output overvoltage protection (OVP). When the VFB voltage exceeds 104% of the VREF but remains below the OVP threshold (116%, typ.), OQDM is activated. During OQDM. the high-side MOSFET is off, while the low-side MOSFET remains on until it reaches the negative current-limit threshold (ILIM\_NEG) the -10A or the VFB voltage falls below 102%. Once the ILIM NEG is reached, the low-side MOSFET is briefly turned off for 700ns before being turned on again. This sequence is repeated until the VFB voltage falls below 102% of the VREF. After completing 15 consecutive FCCM cycles, the RTQ2820A exits the OQDM. This mode effectively reduces overshoot and ensures stable operation.

ΠΠΕ (ΤΟμδ/ΔΙν)

Figure 8. Output Quick Discharge Mode

### 17.15 Output Voltage Discharge

When the RTQ2820A is disabled by EN pin, UVLO or OTP, the device discharges the output capacitors (via SW pins) through an internal discharge resistor ( $80\Omega$ , typ.) connected to ground. This function prevents the reverse current from flowing the output capacitors to the input capacitors once the input voltage collapses. It does not need to rely on another active discharge circuit for discharging output capacitors. This function will be turned off when the fault condition is removed.

### 17.16 Over-Temperature Protection (OTP)

The RTQ2820A includes an over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. The OTP will shut down switching operation when junction temperature exceeds the over-temperature protection threshold ToTP (160°C, typ.). Once the junction temperature cools down by the over-temperature protection hysteresis ToTP\_HYS (30°C, typ.), the RTQ2820A will resume normal operation with a complete soft-start. Note that the over-temperature protection is intended to protect the device during momentary overload conditions. The protection is activated outside of the absolute maximum range of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

### **18 Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and reserve suitable design margin to ensure the functional suitability of their components and systems.

A general RTQ2820A application circuit is shown in a typical application circuit section. External component selection is largely driven by the load requirement. Next, the inductor L is chosen and then the input capacitor  $C_{IN}$ , the output capacitor  $C_{OUT}$ , the internal regulator capacitor  $C_{VCC}$ , and the bootstrap capacitor  $C_{BOOT}$ , can be selected. Next, feedback resistors are selected to set the desired output voltage. Finally, the remaining optional external components can be selected for functions such as the EN and UVLO threshold, external soft-start time, and Power-Good function.

### 18.1 Switching Frequency and MODE Selection

The switching frequency, current limit, and switching mode (PSM or FCCM) are set by a voltage divider connected solely from VCC to AGND to the MODE pin.

The selection of the switching frequency is a trade-off between efficiency and system component size. Highfrequency operation allows the use of smaller inductor and capacitor values. Operating at lower frequencies improves efficiency by reducing internal gate charge and transition losses but requires larger inductance values and/or capacitance to maintain low output ripple voltage.

#### 18.2 Inductor Selection

The inductor selection makes trade-offs among size, cost, efficiency, and transient response requirements. Generally, three key inductor parameters are specified for operation with the device: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (DCR).

A good compromise between size and loss is a 30% peak-to-peak ripple current  $\Delta I_L$  to the IC rated current. The switching frequency, input voltage, output voltage, and selected inductor ripple current determines the inductor value as follows:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_L}$$

Larger inductance values result in lower output ripple voltage and higher efficiency, but a slightly degrade transient response. Lower inductance values allow for smaller case size, but the increased ripple lowers the effective currentlimit threshold and increases the AC losses in the inductor. To enhance efficiency, choose a low-loss inductor with the lowest possible DC resistance that fits in the allotted dimensions. The inductor value determines the ripple current and the load-current value at which the DCM/FCCM switchover occurs.

The selected inductor must require an enough saturate current rating above the peak inductor current before saturation. The peak inductor current (IL\_PEAK) is estimated as below.

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

$I_{L}PEAK = I_{OUT}MAX + \frac{1}{2}\Delta I_{L}$

The current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults, or transient load conditions, the inductor current can increase above the peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit rather than the peak inductor current.

The reverse inductor current should be considered. In FCCM operation, the design of inductor valley current should be higher than ILIM\_NEG to prevent triggering the negative current limit at no load operation.

### 18.3 Input Capacitor Selection

Input capacitance, CIN, is needed to filter the pulsating current at the drain of the high-side power MOSFET. The CIN should be sized to do this without causing a large variation in input voltage. The peak-to-peak voltage ripple on input capacitor can be estimated as the equation below:

$$\Delta V_{CIN} = D \times I_{OUT} \times \frac{1 - D}{C_{IN} \times f_{SW}} + I_{OUT} \times ESR$$

where

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}} \times \eta}$$

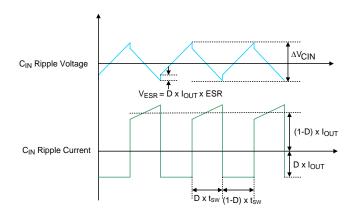

Figure 9 shows the CIN ripple current flowing through the input capacitors and the resulting voltage ripple across the capacitors.

The equivalent series resistance (ESR) is very low for ceramic capacitors. The ripple caused by ESR can be ignored, and the minimum input capacitance can be estimated as the equation below:

$C_{\text{IN}\_\text{MIN}} = I_{\text{OUT}\_\text{MAX}} \times \frac{D(1{-}D)}{\Delta V_{\text{CIN}\_\text{MAX}} \times f_{\text{SW}}}$

where  $\Delta VCIN_MAX = 200 mV$  for typical application (VIN > 7V)

Figure 9. CIN Ripple Voltage and Ripple Current

In addition, the input capacitor needs to have a very low ESR and must be rated to handle the worst-case RMS input current. The RMS ripple current (IRMS) of the converter can be determined by the input voltage (VIN), output voltage (VOUT), and rated output current (IOUT) as the following equation:

$$I_{RMS} \cong I_{OUT\_MAX} \times \frac{V_{OUT}}{V_{IN}} \times \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

From the above, the maximum RMS input ripple current occurs at maximum output load, which should be considered when evaluating the current capabilities of the input capacitors. The maximum ripple voltage usually occurs at 50% duty cycle, that is,  $VIN = 2 \times VOUT$ . It is common to use the worse  $IRMS \cong 0.5 \times IOUT\_MAX$  at  $VIN = 2 \times VOUT$  for design. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life which makes it advisable to further de-rate the capacitor, or choose a capacitor rated at a higher temperature than required.

Several capacitors may also be paralleled to meet size, height and thermal requirements in the design. For low input voltage applications, sufficient bulk input capacitance is needed to minimize transient effects during output load changes.

Ceramic capacitors are ideal for switching regulator applications because its small size, robustness and very low ESR. However, care must be taken when these capacitors are used at the input. A ceramic input capacitor combined with trace or cable inductance forms a high quality (under damped) tank circuit. If the RTQ2820A circuit is plugged into a live supply, the input voltage can ring to twice its nominal value, possibly exceeding the device's rating. This situation is easily avoided by placing the low ESR ceramic input capacitor in parallel with a bulk capacitor with higher ESR to damp the voltage ringing.

The input capacitor should be placed as close as possible to the VIN pins, with a low inductance connection to the PGND of the IC. In addition to a larger bulk capacitor, one small decoupling ceramic capacitor of  $1\mu$ F should be placed close to the part. The capacitors should be 0402 or 0603 in size. X7R capacitors are recommended for best performance across temperature and input voltage variations.

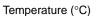

### 18.4 Output Capacitor Selection

The selection of C<sub>OUT</sub> is determined by considering to satisfy the voltage ripple, the transient loads and to ensure that control loop is stable. Loop stability can be checked by viewing the load transient response. The peak-to-peak output ripple,  $\Delta V_{OUT}$ , is characterized by two components, which are ESR ripple  $\Delta V_{P-P}_{ESR}$  and capacitive ripple  $\Delta V_{P-P}_{C}$ , and can be expressed as below:

$\Delta V_{OUT} = \Delta V_{P-P}_{ESR} + \Delta V_{P-P}_{C}$

$\Delta V_{P-P\_ESR} = \Delta I_L \times R_{ESR}$  $\Delta V_{P-P\_C} = \frac{\Delta I_L}{8 \times C_{OUT} \times f_{SW}}$

Where the  $\Delta I_L$  is the peak-to-peak inductor ripple current and RESR is the equivalent series resistance of COUT. The highest output ripple is at maximum input voltage since  $\Delta I_L$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements.

Regarding to the transient loads, the VSAG and VSOAR requirement should be taken into consideration for choosing the output capacitance value. The amount of output sag is a function of the maximum duty factor, which can be calculated from the on-time and minimum off-time.

$$t_{ON} = \frac{V_{OUT}}{V_{IN} \times f_{SW}}$$

$$D_{MAX} = \frac{t_{ON}}{t_{ON} + t_{OFF}MIN}$$

The worst-case output sag voltage can be determined by:

$$\Delta V_{OUT\_SAG} = \frac{L \times (I_{L\_PEAK})^{2}}{2 \times C_{OUT} \times (V_{IN} \times D_{MAX} - V_{OUT})}$$

The amount of overshoot due to stored inductor energy when the load is removed can be calculated as:

$\Delta V_{OUT\_SOAR} = \frac{L \times (I_{L\_PEAK})^2}{2 \times C_{OUT} \times V_{OUT}}$

Ceramic capacitors have very low equivalent series resistance (ESR) and provide the best ripple performance. Be careful to consider the voltage coefficient of ceramic capacitors when choosing the value and case size. Most ceramic capacitors lose 50% or more of their rated value when used near their rated voltage.

### 18.5 Internal VCC Regulator

Good bypassing at VCC pin is necessary to supply the high transient currents required by the power MOSFET gate drivers. Place a low ESR MLCC capacitor with capacitance  $\geq 1\mu$ F (or effective capacitance  $\geq 0.88\mu$ F) as close as possible to VCC pin, and the rated voltage of Cvcc is at least 6.3V or higher to minimize DC bias derating, using 0603 or 0805 in size is recommended.

Applications with high input voltage and high switching frequency will increase die temperature because of the higher power dissipation across the LDO. Do not connect VCC to provide power to other devices or loads.

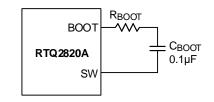

### 18.6 Bootstrap Driver Supply

The bootstrap capacitor ( $C_{BOOT}$ ) between the BOOT pin and the SW pin is used to create a voltage rail above the applied input voltage, VIN. Specifically, the bootstrap capacitor is charged through an internal MOSFET switch to a voltage equal to approximately V<sub>VCC</sub> each time the LS-FET is turned on. The charge on this capacitor is then used to supply the required current during the remainder of the switching cycle.

The selection of C<sub>BOOT</sub> considers the voltage variation allowed on the high-side MOSFET driver after turn-on. Choose  $\Delta V_{BOOT}$  such that the available gate-drive voltage is not significantly degraded when determining C<sub>BOOT</sub>. A typical range of  $\Delta V_{BOOT}$  is from 100mV to 300mV. The bootstrap capacitor should be a low-ESR ceramic capacitor. For most applications, a 0.1µF ceramic capacitor with X5R or better grade dielectric is recommended. The capacitor should have a 10V or higher voltage rating.

EMI issue is worse when the switch is turned on rapidly due to high di/dt noises. In some cases, it is desirable to reduce EMI further, even at the expense of some additional power dissipation. The turn-on rate of the high-side switch can be slowed by placing a small (<  $10\Omega$ ) resistor between the BOOT pin and the external bootstrap capacitor. This will slow down the rates of the high-side switch turn-on and the rise of Vsw. The recommended application circuit is shown in Figure 10, which includes an external bootstrap diode for charging the bootstrap capacitor and a bootstrap resistor RBOOT placed between the BOOT pin and the capacitor connection.

Figure 10 External Bootstrap Resistor at the BOOT Pin

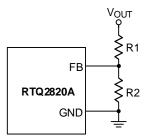

### 18.7 Output Voltage Programming

The output voltage can be programmed by a resistive divider from the output to ground with the midpoint connected to the FB pin. The resistive divider allows the FB pin to sense a fraction of the output voltage as shown in <u>Figure 11</u> and the output voltage is set according to the following equation:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

where the reference voltage  $\mathsf{V}_{\mathsf{REF}}$ , is typically  $0.6\mathsf{V}$

Figure 11. Output Voltage Setting

The recommended resistance of R2 is  $10k\Omega$ , ranging from  $1k\Omega$  to  $10k\Omega$  for good noise immunity consideration. The resistance of R1 can then be obtained as below:

$R1 = \frac{R2 \times (V_{OUT} - V_{REF})}{V_{REF}}$

For better output voltage accuracy, the divider resistors (R1 and R2) with  $\pm$ 1% tolerance or better should be used. The placement of the resistive divider should be very close to the FB pin to minimize PCB trace length and noise immunity consideration. Furthermore, great care should be taken to route the feedback trace away from noise sources, such as the inductor or the SW trace.

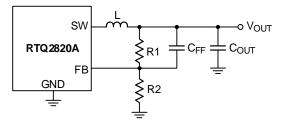

### 18.8 Feedforward Capacitor (CFF)

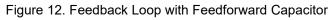

The RTQ2820A is optimized for low duty-cycle applications and the control loop is stable with low ESR ceramic output capacitors. In higher duty-cycle applications (higher output voltages or lower input voltage), the internal ripple signal will increase in amplitude. Before the ACOT<sup>®</sup> control loop can react to an output voltage fluctuation, the voltage change on the feedback signal must exceed the internal ripple amplitude. Because of the large internal ripple in this condition, the response may become too slow, and may show an under-damped response. This can cause some ringing in the output, and is especially visible at higher output voltage applications like 12V to 5V where duty-cycle is high and the feedback network attenuation is large, adding to the delay. As shown in Figure 12, adding a feedforward capacitor (CFF) across the upper feedback resistor is recommended. This increases the damping of the control system.

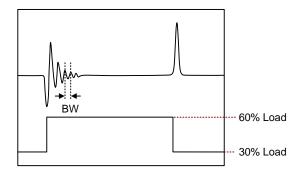

Loop stability can be checked by viewing the load transient response. A load step with a speed that exceeds the converter bandwidth must be applied. For ACOT<sup>®</sup>, loop bandwidth can be in the order of 100 to 200kHz, so a load step with 500ns maximum rise time (di/dt  $\approx$  2A/µs) ensures the excitation frequency is sufficient. It is important that the converter operates in PWM mode, outside the light load efficiency range, and below any current-limit threshold. A load transient from 30% to 60% of maximum load is reasonable which is shown Figure 13.

Figure 13. Example of Measuring the Converter BW by Fast Load Transient

CFF can be calculated basing on below equation:

$$C_{FF} = \frac{1}{2\pi \times BW} \times \sqrt{\frac{1}{R1}} \times \left(\frac{1}{R1} + \frac{1}{R2}\right)$$

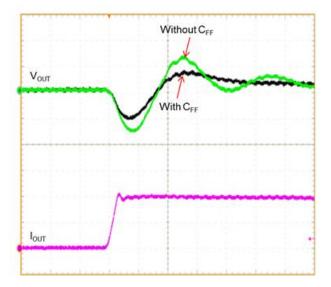

Figure 14. shows the transient performance with and without feedforward capacitor.

Note that, after defining the CFF, please also check the load regulation because feedforward capacitor might inject an offset voltage into VOUT to cause VOUT inaccuracy. If the output voltage is over specification caused by calculated CFF, please decrease the value of feedforward capacitor CFF.

### 18.9 Enable and Adjustable UVLO

The EN pin controls the turn-on and turn-off of the device. When EN pin voltage is above the turn-on threshold (V<sub>EN\_R</sub>), the device starts switching. It stops switching when the EN pin voltage falls below the turn-off threshold (V<sub>EN\_F</sub>). The RTQ2820A internally weekly pull-down the EN pin. For automatic start-up, the EN pin can be connected to the input supply VIN directly through a pull-up resistor R<sub>EN</sub>. The large built-in hysteresis band makes the EN pin useful for simple delay and timing circuits. The EN pin can be externally connected to VIN by adding a resistor R<sub>EN</sub> and a capacitor C<sub>EN</sub>, as shown in Figure 15, to have an additional delay.

Figure 15. Enable Timing Control

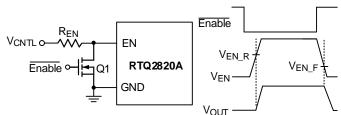

An external MOSFET can be added for the EN pin to be logic-controlled, as shown in Figure 16. In this case, a pullup resistor, REN, is connected between VIN and the EN pin. The MOSFET Q1 will be under logic control to pull down the EN pin.

Figure 16. Logic Control for the EN Pin

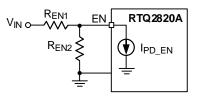

If the device is desired to enable under specific V<sub>IN</sub> or be shut down, a resistive divider (R<sub>EN1</sub> and R<sub>EN2</sub>) can be used to externally set the input VULO threshold as shown in Figure 17. o set the start voltage, first select the divider resistor REN2, the recommended value is between  $10k\Omega$  and  $100k\Omega$ . A resistor divider between VIN and EN can establish different turn-on (V<sub>START</sub>) or turn-off thresholds (V<sub>STOP</sub>). This is recommended for customer design when without additional EN logic signal, to avoid bouncing occurring at the EN pin.

Figure 17. Resistor Divider for Lockout Threshold Setting

To set the start voltage, first select the bottom resistor REN2, the recommended value is between  $10k\Omega$  and  $100k\Omega$ . A resistor divider between VIN and EN can set a different turn-on (VSTART) and turn-off thresholds (VSTOP) respectively.

$$R_{EN1} = \frac{\left(V_{START} - V_{EN_R}\right)}{I_{PD_EN} + \frac{V_{EN_R}}{R_{EN2}}}$$

$$V_{START} = V_{EN_R} \times \frac{R_{EN1} + R_{EN2}}{R_{EN2}}$$

$V_{\text{STOP}} = V_{\text{EN}_{\text{F}}} \times \frac{N_{\text{EN}_{1}} + N_{\text{EN}_{2}}}{R_{\text{EN}_{2}}}$

### 18.10 Thermal Considerations

Thermal Considerations In many applications, the RTQ2820A does not generate much heat due to its high efficiency and low thermal resistance of its thermally enhanced WQFN-21L 3x4 (FC) package. However, in applications where the RTQ2820A is running at a high ambient temperature, high input voltage, and high switching frequency, the generated heat may exceed the maximum junction temperature of the part. To avoid permanent damage to the device, the junction temperature should never exceed the maximum junction temperature listed under Absolute Maximum Ratings. If the junction temperature reaches approximately 160°C, the RTQ2820A will stop switching the power MOSFETs until the temperature drops by about 30°C cooler. The maximum power dissipation can be calculated by the following formula:

$PD(MAX) = (TJ(MAX) - TA) / \theta JA(EFFECTIVE)$

Where

- T<sub>J(MAX)</sub> is the maximum allowed junction temperature of the die. For recommended operating condition specifications, the maximum junction temperature is 150°C.

- TA is the ambient operating temperature,

- θJA(EFFECTIVE) is the system-level junction to ambient thermal resistance. It can be estimated from thermal modeling or measurements in the system.

The thermal resistance of the device strongly depends on the surrounding PCB layout and can be enhanced by incorporating a copper ground heat sink. Additionally, including backside copper with thermal vias, stiffeners, and other enhancements can help reduce thermal resistance.

Experiments in the Richtek thermal lab show that simply set  $\theta_{JA(EFFECTIVE)}$  as 110% to 120% of the  $\theta_{JA}$  is reasonable to obtain the allowed PD(MAX).

As an example, consider the case when the RTQ2820A is used in switching frequency 800kHz applications where VIN = 12V, VOUT = 1V. The efficiency at output current 20A is 84.59% by using VLBU1007090T-R33L (0.33 $\mu$ H, 0.18m $\Omega$  DCR) as the inductor and measured at room temperature. The core loss 1.74W can be obtained from its website. In this case, the power dissipation of RTQ2820A is:

$$P_{D,RT} = \frac{1 - \eta}{\eta} \times P_{OUT} - (I_{OUT}^2 \times DCR + P_{CORE}) = 0.2 \times 20 - (20^2 \times 0.00018 + 0.106) = 3.53W$$

Considering the  $\theta_{JA(EFFECTIVE)}$  is 25.87°C/W by using the RTQ2812A evaluation board with 4 layers PCB and 2oz copper thickness, the junction temperature of the regulator operating in a 25°C ambient temperature is approximately:

$T_J = P_{D,RT} \times \theta_{JA(EFEECTIVE)} + T_A = 3.53W \times 1.1 \times 20.44^{\circ}C/W + 25^{\circ}C = 104.5^{\circ}C$

# **RTQ2820A**

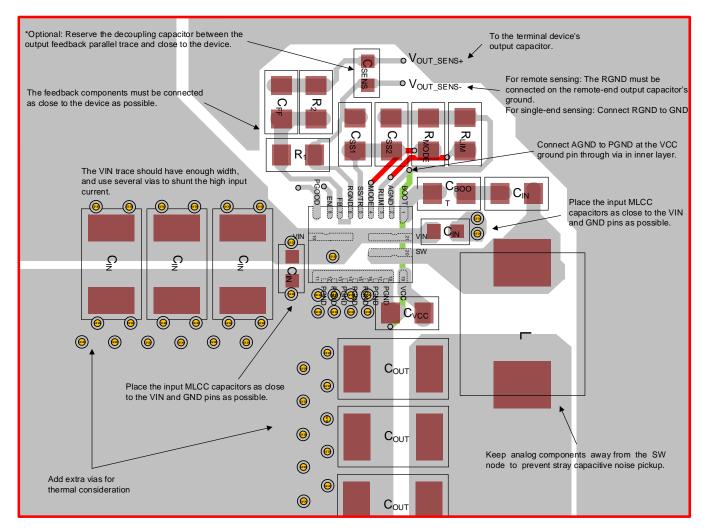

### 18.11 PCB Layout Considerations

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the RTQ2820A:

- Use a four-layer or six-layer PCB with a maximum ground plane for optimal thermal performance.

- Place input MLCC capacitors as close to the VIN and PGND pins as possible. It is highly recommended to use a  $1\mu$ F/25V/X6S/0402 ceramic capacitor between the VIN pin 10 and PGND pin 11.

- Maximize the width and shorten the main current path, such as the VIN, SW, VOUT, and PGND copper plane, to minimize parasitic impedance.

- Place the decoupling capacitor, Cvcc, as close to VCC pin as possible.

- Connect AGND and PGND at the point of the VCC capacitor's ground connection. Css, RMODE, and RLIM should be connected to AGND using short, direct copper traces.

- Place bootstrap capacitor, CBOOT, as close to IC as possible. Rout the trace with a width of 20mil or wider. A 0.1μF to 1μF with 10V or higher rating is recommended for the bootstrap capacitor.

- Place multiple vias under the device near VIN and PGND, and place near input capacitors to reduce parasitic inductance and improve thermal performance. To keep thermal resistance low, extend the ground plane as much as possible, and add thermal vias under and near the RTQ2820A to additional ground planes within the circuit board and on the bottom side.

- The high frequency switching nodes, SW, and BOOT, should be as small as possible. Keep analog components away from the SW and BOOT nodes.