# **RTQ2532E**

# 2A, 6.5V, Low-Noise, Low-Dropout Linear Regulator

# 1 General Description

The RTQ2532E is a high-current (2A), low-noise (6.8 $\mu$ VRMS), high accuracy (1% over line, load, and temperature), low-dropout linear regulator (LDO) capable of sourcing 2A with an extremely low dropout (maximum 125mV). The device supports a single input supply voltage as low to 1.1V, which makes it easy to use.

The low-noise, high PSRR, and high output current capability make the RTQ2532E ideal to power noise-sensitive devices such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and RF components. With very high accuracy, remote sensing, and soft-start capabilities to reduce inrush current, the RTQ2532E is ideal for powering digital loads such as FPGAs, DSPs, and ASICs.

The external enable control and power good indicator function make the control sequence easier. The output noise immunity is enhanced by adding an external bypass capacitor on the NR/SS pin. The device is fully specified over the temperature range of  $TJ = -40^{\circ}C$  to 125°C and is offered in the VQFN-20L 3.5x3.5 and VQFN-20L 5x5 packages.

### 2 Features

- Input Voltage Range: 1.1V to 6.5V

- Two Output Voltage Modes

- ▶ 0.5 V to 5.5V (Set by a Resistive Divider)

- ► 0.5V to 2.075V (Set via PCB Layout, No External Resistor Required)

- Accurate Output Voltage Accuracy (1%) Over Line, Load, and Temperature

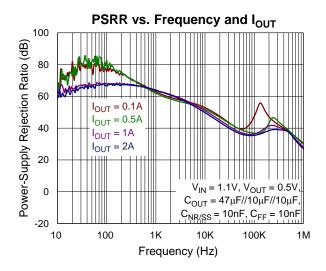

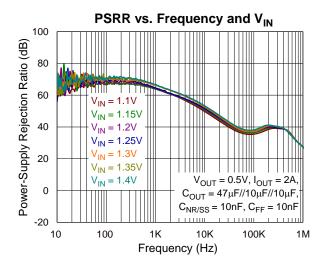

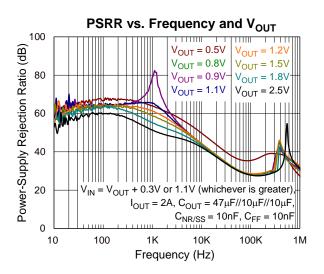

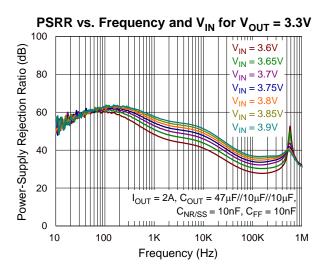

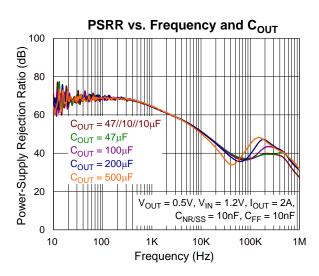

- PSRR: 44dB at 500kHz

- Noise Immunity

- ► 6.8µVRMS at 0.5V Output

- ▶ 16µVRMS at 5V Output

- Dropout Voltage: 125mV Maximum at 2A

- Enable Control

- Programmable Soft-Start Output

- Stable with a 47μF or Larger Ceramic Output Capacitor

- Support Power-Good Indicator Function

- Junction Temperature Range: -40°C to 125°C

# 3 Applications

- Portable Electronic Devices

- Wireless Infrastructures: SerDes, FPGA, DSP

- RD, IF, Components: VCO, ADC, DAC, LVDS

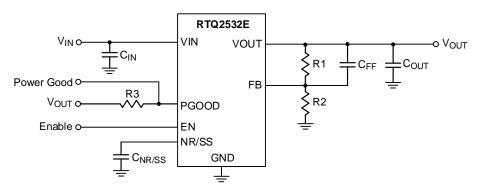

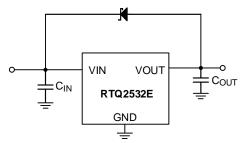

# 4 Simplified Application Circuit

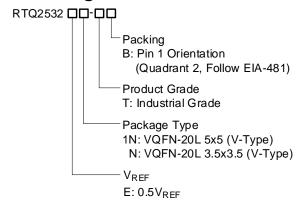

# **5 Ordering Information**

### Note:

Richtek products are Richtek Green Policy compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

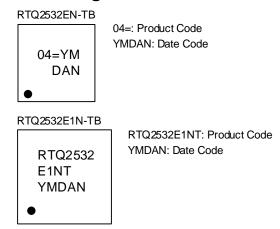

# **6 Marking Information**

# **Table of Contents**

| 1  | Gener     | al Description1                |    | 18.3    | CIN and COUT Selection       | 19 |

|----|-----------|--------------------------------|----|---------|------------------------------|----|

| 2  | Features1 |                                |    | 18.4    | Feed-Forward Capacitor (CFF) | 20 |

| 3  | Applic    | cations1                       |    | 18.5    | Soft-Start and Noise         |    |

| 4  | Simpl     | ified Application Circuit1     |    |         | Reduction (CNR/SS)           | 20 |

| 5  | Order     | ing Information2               |    | 18.6    | Input Inrush Current         | 20 |

| 6  | Markiı    | ng Information2                |    | 18.7    | Undervoltage Lockout (UVLO)  | 20 |

| 7  | Pin Co    | onfiguration4                  |    | 18.8    | Power-Good (PGOOD) Function  | 21 |

| 8  | Functi    | ional Pin Description4         |    | 18.9    | Reverse Current Protection   | 22 |

| 9  | Functi    | ional Block Diagram6           |    | 18.10   | Thermal Considerations       | 22 |

| 10 | Absol     | ute Maximum Ratings7           |    | 18.11   | Layout Considerations        | 23 |

| 11 | ESD F     | Ratings7                       | 19 | Outline | e Dimension                  | 25 |

| 12 | Recor     | nmended Operating Conditions7  |    | 19.1    | VQFN-20L 3.5x3.5             | 25 |

| 13 | Therm     | nal Information7               |    | 19.2    | VQFN-20L 5x5                 | 26 |

| 14 | Electr    | ical Characteristics8          | 20 | Footpr  | int Information              | 27 |

| 15 | Typica    | al Application Circuit10       |    | 20.1    | VQFN-20L 3.5x3.5             | 27 |

| 16 | Typica    | al Operating Characteristics13 |    | 20.2    | VQFN-20L 5x5                 | 27 |

| 17 | Opera     | ition16                        | 21 | Packin  | ng Information               | 28 |

|    | 17.1      | Enable and Shutdown16          |    | 21.1    | QFN/DFN 3.5x3.5 Tape         |    |

|    | 17.2      | VOUT Programming Pins 16       |    |         | and Reel Data                | 28 |

|    | 17.3      | Programmable Soft-Start16      |    | 21.2    | QFN/DFN 3.5x3.5 Tape         |    |

|    | 17.4      | Power Good 16                  |    |         | and Reel Packing             | 29 |

|    | 17.5      | Undervoltage Lockout (UVLO) 16 |    | 21.3    | QFN/DFN 5x5 Tape             |    |

|    | 17.6      | Internal Current Limit (Іым)17 |    |         | and Reel Data                | 30 |

|    | 17.7      | Over-Temperature               |    | 21.4    | QFN/DFN 5x5 Tape             |    |

|    |           | Protection (OTP)17             |    |         | and Reel Packing             | 31 |

|    | 17.8      | Output Active Discharge 17     |    | 21.5    | Packing Material Anti-ESD    |    |

| 18 | Applic    | cation Information18           |    |         | Property                     | 32 |

|    | 18.1      | Output Voltage Setting 18      | 22 | Datash  | neet Revision History        | 33 |

|    | 18.2      | Dropout Voltage19              |    |         |                              |    |

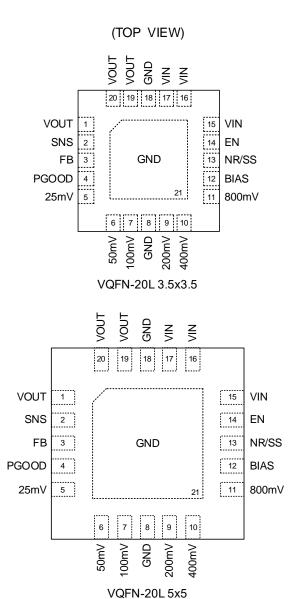

# 7 Pin Configuration

# **8 Functional Pin Description**

| Pin No.                           |          | Pin Function                                                                                                                                                                                                                                                  |  |  |  |

|-----------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VQFN-20L 3.5x3.5/<br>VQFN-20L 5x5 | Pin Name |                                                                                                                                                                                                                                                               |  |  |  |

| 1, 19, 20                         | VOUT     | LDO output pins. A $47\mu F$ or larger ceramic capacitor ( $22\mu F$ or greater effective capacitance) is required for stability. Place the output capacitor as close to the device as possible and minimize the impedance between the VOUT pin and the load. |  |  |  |

| 2                                 | SNS      | Output voltage sense input pin. Connect this pin only if using the configuration without external resistors. Keep the SNS pin floating if the VOUT voltage is set by an external resistor.                                                                    |  |  |  |

| 3                                 | FB       | Feedback voltage input. This pin is used to set the desired output voltage via an external resistive divider. The feedback reference voltage is 0.5V typically.                                                                                               |  |  |  |

| Pin No.                           |                                           |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VQFN-20L 3.5x3.5/<br>VQFN-20L 5x5 | Pin Name                                  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

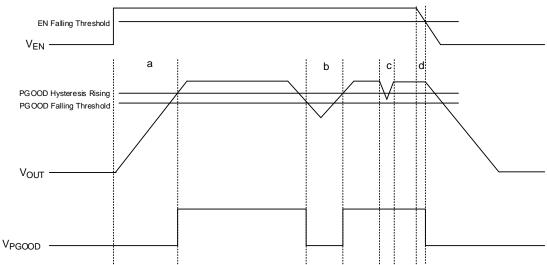

| 4                                 | PGOOD                                     | Power good indicator output. This is an open-drain output that is active high when the output voltage reaches 88% of the target. The pin is pulled low when the output voltage is lower than its specified thresholds, including EN shutdown, OCP, and OTP.                                                                                                                                       |  |  |

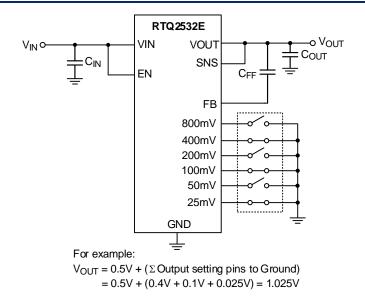

| 5, 6, 7, 9, 10, 11                | 25mV, 50mV, 100mV,<br>200mV, 400mV, 800mV | Output voltage setting pins. Connect these pins to the ground or leave floating. Connecting these pins to the ground increases the output voltage by the value of the pin name; multiple pins can be simultaneously connected to GND to select the desired output voltage. Leave these pins floating (open) if the VOUT voltage is set by an external resistor.                                   |  |  |

| 8, 18,<br>21 (Exposed Pad)        | GND                                       | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                                                                                                       |  |  |

| 12                                | BIAS                                      | This pin has no internal IC connection. A BIAS input voltage below 6.5V can be applied to this pin (for compatibility with other vendors), or this pin can be left open (floating). Either option is safe and will not affect IC's operation.                                                                                                                                                     |  |  |

| 13                                | NR/SS                                     | Noise-reduction and soft-start pin. Decoupling this pin to GND with an external capacitor CNR/SS can reduce output noise to very low levels and also slow down the rising of VOUT, providing a soft-start behavior. For low-noise applications, a 10nF to $1\mu F$ CNR/SS is suggested.                                                                                                           |  |  |

| 14                                | EN                                        | Enable control input. Connecting this pin to a logic high enables the regulator, and driving this pin low puts it into shutdown mode. The device can have VIN and VEN sequenced in any order without causing damage to the device. However, to ensure the soft-start function works as intended, certain sequencing rules must be applied. Enabling the device after VIN is present is preferred. |  |  |

| 15, 16, 17                        | VIN                                       | Supply input. A general $47\mu F$ ceramic capacitor should be placed as close as possible to this pin for better noise rejection.                                                                                                                                                                                                                                                                 |  |  |

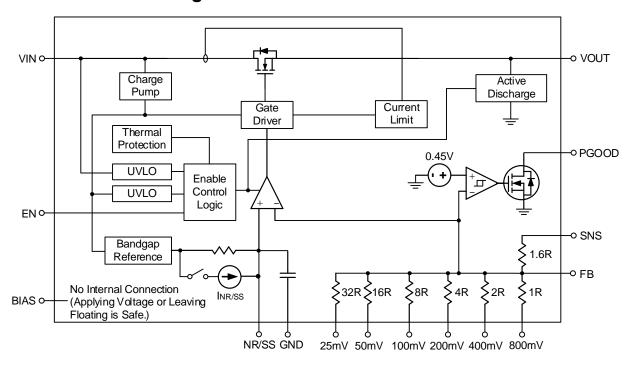

# 9 Functional Block Diagram

# 10 Absolute Maximum Ratings

### (Note 1)

| • | VIN, PGOOD, EN                        | -0.3V to 7  | V    |

|---|---------------------------------------|-------------|------|

| • | VOUT                                  | -0.3V to 7  | V    |

| • | NR/SS, FB                             | -0.3V to 3. | .6V  |

| • | Lead Temperature (Soldering, 10 sec.) | 260°C       |      |

| • | Junction Temperature                  | 150°C       |      |

| • | Storage Temperature Range             | -65°C to 1  | 50°C |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

# 11 ESD Ratings

### (Note 2)

ESD Susceptibility

HBM (Human Body Model)------2kV

Note 2. Devices are ESD sensitive. Handling precautions are recommended.

# 12 Recommended Operating Conditions

### (Note 3)

- Supply Input Voltage, VIN------ 1.1V to 6.5V

Note 3. The device is not guaranteed to function outside its operating conditions.

### 13 Thermal Information

(Note 4 and Note 5)

|                  | Thermal Parameter                                       | VQFN-20L<br>3.5x3.5 | VQFN-20L<br>5x5 | Unit |

|------------------|---------------------------------------------------------|---------------------|-----------------|------|

| θJA              | Junction-to-ambient thermal resistance (JEDEC standard) | 38.5                | 32.51           | °C/W |

| $\theta$ JC(Top) | Junction-to-case (top) thermal resistance               | 50.57               | 30.82           | °C/W |

| θJC(Bottom)      | Junction-to-case (bottom) thermal resistance            | 2.47                | 1.73            | °C/W |

| θJA(EVB)         | Junction-to-ambient thermal resistance (specific EVB)   | 39.33               | 34.82           | °C/W |

| ΨJC(Top)         | Junction-to-top characterization parameter              | 5.79                | 3.69            | °C/W |

| ΨЈВ              | Junction-to-board characterization parameter            | 24.06               | 18.89           | °C/W |

**Note 4.** For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

Note 5. θJA(EVB), ΨJC(TOP), and ΨJB are measured on a high effective-thermal-conductivity four-layer test board which is in size of 70mm x 50mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

# 14 Electrical Characteristics

Over operating temperature range (TJ =  $-40^{\circ}$ C to  $125^{\circ}$ C), (1.1V  $\leq$  VIN  $\leq$  6.5V and VIN  $\geq$  VOUT(TARGET) + 0.3 V, VOUT(TARGET) = 0.5V, VOUT connected to  $50\Omega$  to GND, VEN = 1.1 V, CIN =  $10\mu\text{F}$ , COUT =  $47\mu\text{F}$ , CNR/SS = 0nF, CFF = 0nF, and PGOOD pin pulled up to VIN with  $100k\Omega$ , unless otherwise noted.) (Note 6)

| Parameter Symbol                            |            | Test Conditions                                                                                                                                                                         | Min            | Тур             | Max            | Unit |  |

|---------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|----------------|------|--|

| VIN Supply Input<br>Voltage                 | VIN        |                                                                                                                                                                                         | 1.1            |                 | 6.5            | V    |  |

| Reference Voltage                           | VREF       |                                                                                                                                                                                         |                | 0.5             |                | V    |  |

| NR/SS Pin<br>Voltage                        | VNR/SS     |                                                                                                                                                                                         |                | 0.5             |                | V    |  |

| Undervoltage<br>Lockout Rising<br>Threshold | Vuvlo_r    | VIN increasing                                                                                                                                                                          |                | 1.02            | 1.085          | V    |  |

| Undervoltage<br>Lockout<br>Hysteresis       | Vuvlo_HYS  | Hysteresis                                                                                                                                                                              |                | 100             |                | mV   |  |

|                                             |            | Using external resistors                                                                                                                                                                | 0.5            |                 | 5.5            | V    |  |

| Output Voltage                              | Vout       | Using voltage setting pins (25mV, 50mV, 100mV, 200mV, 400mV, 800mV)                                                                                                                     | 0.5            |                 | 2.075          | V    |  |

| Output Voltage<br>Accuracy<br>(Note 7)      | VOUT_ACC   | $\label{eq:VIN} \begin{split} &\text{VIN} = \text{VOUT} + 0.3 \text{V}, \ 0.5 \text{V} \leq \text{VOUT} \leq 5.5 \text{V}, \\ &\text{1mA} \leq \text{IOUT} \leq 2 \text{A} \end{split}$ | -1             |                 | 1              | %    |  |

| Line Regulation                             | VLINE_REG  | IOUT = 1mA, 1.1V ≤ VIN ≤ 6.5V                                                                                                                                                           |                | 0.05            |                | %/V  |  |

| Load Regulation                             | VLOAD_REG  | $1mA \le IOUT \le 2A$                                                                                                                                                                   |                | 0.08            |                | %/A  |  |

| Dropout Voltage                             | VDROP      | VIN = 1.1V to 6.5V, IOUT = 2A,<br>VFB = 0.5V - 3%                                                                                                                                       |                |                 | 125            | mV   |  |

| Current Limit                               | ILIM       | VOUT = 90%VOUT(TARGET),<br>VIN = VOUT(TARGET) + 400mV                                                                                                                                   | 2.2            | 3.3             | 3.8            | Α    |  |

| Short-Circuit<br>Current Limit              | Isc        | RLOAD = $20$ m $Ω$ , under foldback operation                                                                                                                                           |                | 1               |                | Α    |  |

| Ground Pin                                  | loup       | Minimum load, VIN = 6.5V, IOUT = 5mA                                                                                                                                                    |                | 2.8             | 4              | mA   |  |

| Current                                     | IGND       | Maximum load, VIN = 1.4V, IOUT = 2A                                                                                                                                                     |                | 3.7             | 5.5            | mA   |  |

| Shutdown Current                            | ISHDN      | PGOOD = Open, Vin = 6.5V, VEN = 0.5V                                                                                                                                                    |                |                 | 25             | μΑ   |  |

| EN Pin Current                              | IEN        | VIN = 6.5V, VEN = 0V and 6.5V                                                                                                                                                           | -0.1           |                 | 0.1            | μΑ   |  |

| EN Input Voltage<br>Rising Threshold        | VEN_R      | Enable device                                                                                                                                                                           | 1.1            |                 | 6.5            | V    |  |

| EN Input Voltage<br>Falling Threshold       | VEN_F      | Disable device                                                                                                                                                                          | 0              |                 | 0.5            | V    |  |

| Power-Good<br>Voltage Threshold             | VPGOOD     | For the direction PGOOD signal falling with decreasing VOUT                                                                                                                             | 0.82 x<br>VOUT | 0.883 x<br>VOUT | 0.93 x<br>VOUT | V    |  |

| Power-Good<br>Voltage Hysteresis            | VPGOOD_HYS | For PGOOD signal rising                                                                                                                                                                 |                | 2% x<br>Vout    |                | V    |  |

| PGOOD Pin Low-<br>Level Output<br>Voltage   | VPGOOD_L   | VOUT < VPGOOD, IPGOOD = -1mA (current into device)                                                                                                                                      |                |                 | 0.4            | V    |  |

| Parameter                                    | Symbol              | Test Conditions                                                                               |                            | Min  | Тур | Max | Unit  |

|----------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|----------------------------|------|-----|-----|-------|

| PGOOD Pin<br>Leakage Current                 | IPGOOD_LK           | VOUT > VPGOOD,<br>VPGOOD = 6.5V                                                               |                            |      |     | 1   | μА    |

| NR/SS Pin<br>Charging Current                | INR/SS              | VNR/SS = GND, VIN = 6.5V                                                                      |                            | 4    |     | 9   | μА    |

| FB Pin Current                               | IFB                 | VIN = 6.5V                                                                                    |                            | -100 |     | 100 | nA    |

|                                              |                     | VIN = 1.2V,<br>IOUT = 2A,                                                                     | f = 10kHz,<br>VOUT = 0.5V  | 1    | 49  |     |       |

| Power Supply                                 |                     | CNR/SS = 100nF,<br>CFF = 10nF,<br>COUT = 47μF//10μF//10μF                                     | f = 500kHz,<br>VOUT = 0.5V |      | 44  |     | ID.   |

| Rejection Ratio                              |                     | VIN – VOUT = 0.4V,<br>IOUT = 2A,<br>CNR/SS = 100nF,<br>CFF = 10nF,<br>COUT = 47μF//10μF//10μF | f = 10kHz,<br>Vout = 5V    |      | 43  |     | dB    |

|                                              |                     |                                                                                               | f = 500kHz,<br>Vout = 5V   | -    | 38  |     |       |

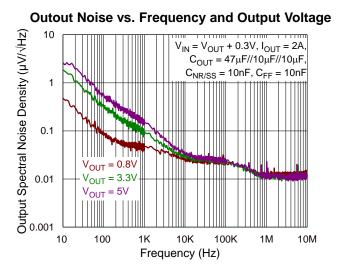

|                                              |                     | BW = 10Hz to 100kHz                                                                           | VIN = 1.1V<br>VOUT = 0.5V  |      | 6.8 |     |       |

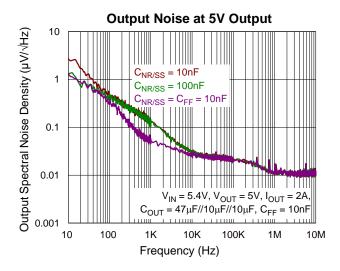

| Output Noise                                 | VN                  | CNR/SS = 100nF,<br>CFF = 10nF,                                                                | VIN = 3.6V<br>VOUT = 3.3V  | -    | 10  |     | μVRMS |

|                                              |                     | COUT = $47\mu F//10\mu F//10\mu F$                                                            | VOUT = 5V                  |      | 16  |     |       |

| Over-Temperature<br>Protection<br>Threshold  | ТОТР                |                                                                                               |                            |      | 160 |     | 00    |

| Over-Temperature<br>Protection<br>Hysteresis | Protection TOTP_HYS |                                                                                               |                            |      | 20  |     | °C    |

Note 6. Vout(target) is the expected Vout value set by the external feedback resistors. The  $50\Omega$  load is disconnected when the test conditions specify an lout value.

Note 7. External resistor tolerance is not taken into account.

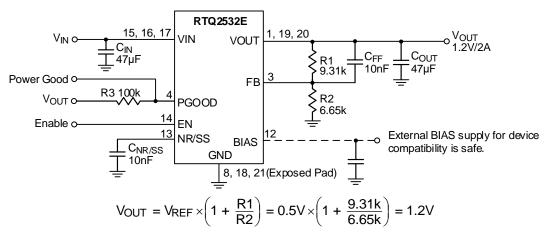

# 15 Typical Application Circuit

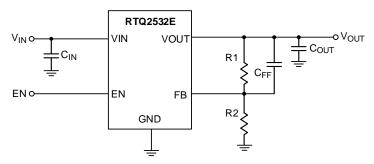

Figure 1. Configuration Circuit for VOUT Adjusted by a Resistor Divider.

Table 1. Recommended Feedback-Resistor Values

| Outroot Valtage AA | External Resistor Divider Combination |        |  |  |  |

|--------------------|---------------------------------------|--------|--|--|--|

| Output Voltage (V) | R1(kΩ)                                | R2(kΩ) |  |  |  |

| 0.8                | 12                                    | 20     |  |  |  |

| 0.9                | 12                                    | 15     |  |  |  |

| 1                  | 12.4                                  | 12.4   |  |  |  |

| 1.2                | 9.31                                  | 6.65   |  |  |  |

| 1.5                | 12.4                                  | 6.2    |  |  |  |

| 1.8                | 10.2                                  | 3.92   |  |  |  |

| 2.5                | 10.2                                  | 2.55   |  |  |  |

| 3.3                | 10.7                                  | 1.91   |  |  |  |

| 4.5                | 12                                    | 1.5    |  |  |  |

| 5                  | 10.2                                  | 1.13   |  |  |  |

| 5.5                | 10.2                                  | 1.02   |  |  |  |

Table 2. Recommended External Components

| Component                | Description          | Vendor P/N                  |

|--------------------------|----------------------|-----------------------------|

| CFF, CNR/SS              | 10nF, 50V, X7R, 0603 | GRM033R71E103KE14 (Murata)  |

| CIN, COUT <sup>(1)</sup> | 47μF, 16V, X6S, 1210 | GRT32EC81C476KE13L (Murata) |

Note 8. Marked with (1) indicates: Considering the effective capacitance derated with the biased voltage level, the Court component needs to satisfy the effective capacitance at least 22 µF or above at targeted output level for stable and normal operation.

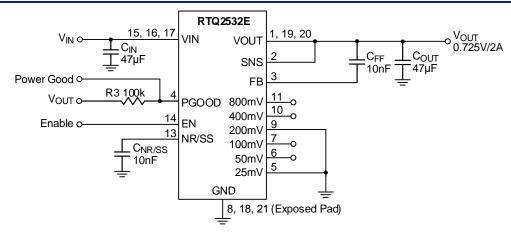

VOUT = VREF + 25mv + 200mV = 0.5V + 25mV + 200mV = 0.725V

(Table 3 provides a full list for different VOUT targets and the corresponding pin settings.)

Figure 2. Configuration Circuit for Adjusted Vout via PCB Layout

Table 3. Vout Select Pin Settings for Different Targets

| 1/                      |      |      |       |       |       |       |                         |      |      |       |       |       |       |

|-------------------------|------|------|-------|-------|-------|-------|-------------------------|------|------|-------|-------|-------|-------|

| V <sub>OUT</sub><br>(V) | 25mV | 50mV | 100mV | 200mV | 400mV | 800mV | V <sub>OUT</sub><br>(V) | 25mV | 50mV | 100mV | 200mV | 400mV | 800mV |

| 0.5                     | Open | Open | Open  | Open  | Open  | Open  | 1.3                     | Open | Open | Open  | Open  | Open  | GND   |

| 0.525                   | GND  | Open | Open  | Open  | Open  | Open  | 1.325                   | GND  | Open | Open  | Open  | Open  | GND   |

| 0.55                    | Open | GND  | Open  | Open  | Open  | Open  | 1.35                    | Open | GND  | Open  | Open  | Open  | GND   |

| 0.575                   | GND  | GND  | Open  | Open  | Open  | Open  | 1.375                   | GND  | GND  | Open  | Open  | Open  | GND   |

| 0.6                     | Open | Open | GND   | Open  | Open  | Open  | 1.4                     | Open | Open | GND   | Open  | Open  | GND   |

| 0.625                   | GND  | Open | GND   | Open  | Open  | Open  | 1.425                   | GND  | Open | GND   | Open  | Open  | GND   |

| 0.65                    | Open | GND  | GND   | Open  | Open  | Open  | 1.45                    | Open | GND  | GND   | Open  | Open  | GND   |

| 0.675                   | GND  | GND  | GND   | Open  | Open  | Open  | 1.475                   | GND  | GND  | GND   | Open  | Open  | GND   |

| 0.7                     | Open | Open | Open  | GND   | Open  | Open  | 1.5                     | Open | Open | Open  | GND   | Open  | GND   |

| 0.725                   | GND  | Open | Open  | GND   | Open  | Open  | 1.525                   | GND  | Open | Open  | GND   | Open  | GND   |

| 0.75                    | Open | GND  | Open  | GND   | Open  | Open  | 1.55                    | Open | GND  | Open  | GND   | Open  | GND   |

| 0.775                   | GND  | GND  | Open  | GND   | Open  | Open  | 1.575                   | GND  | GND  | Open  | GND   | Open  | GND   |

| 0.8                     | Open | Open | GND   | GND   | Open  | Open  | 1.6                     | Open | Open | GND   | GND   | Open  | GND   |

| 0.825                   | GND  | Open | GND   | GND   | Open  | Open  | 1.625                   | GND  | Open | GND   | GND   | Open  | GND   |

| 0.85                    | Open | GND  | GND   | GND   | Open  | Open  | 1.65                    | Open | GND  | GND   | GND   | Open  | GND   |

| 0.875                   | GND  | GND  | GND   | GND   | Open  | Open  | 1.675                   | GND  | GND  | GND   | GND   | Open  | GND   |

| 0.9                     | Open | Open | Open  | Open  | GND   | Open  | 1.7                     | Open | Open | Open  | Open  | GND   | GND   |

| 0.925                   | GND  | Open | Open  | Open  | GND   | Open  | 1.725                   | GND  | Open | Open  | Open  | GND   | GND   |

| 0.95                    | Open | GND  | Open  | Open  | GND   | Open  | 1.75                    | Open | GND  | Open  | Open  | GND   | GND   |

| 0.975                   | GND  | GND  | Open  | Open  | GND   | Open  | 1.775                   | GND  | GND  | Open  | Open  | GND   | GND   |

| 1                       | Open | Open | GND   | Open  | GND   | Open  | 1.8                     | Open | Open | GND   | Open  | GND   | GND   |

| 1.025                   | GND  | Open | GND   | Open  | GND   | Open  | 1.825                   | GND  | Open | GND   | Open  | GND   | GND   |

| 1.05                    | Open | GND  | GND   | Open  | GND   | Open  | 1.85                    | Open | GND  | GND   | Open  | GND   | GND   |

| 1.075                   | GND  | GND  | GND   | Open  | GND   | Open  | 1.875                   | GND  | GND  | GND   | Open  | GND   | GND   |

| 1.1                     | Open | Open | Open  | GND   | GND   | Open  | 1.9                     | Open | Open | Open  | GND   | GND   | GND   |

| 1.125                   | GND  | Open | Open  | GND   | GND   | Open  | 1.925                   | GND  | Open | Open  | GND   | GND   | GND   |

| 1.15                    | Open | GND  | Open  | GND   | GND   | Open  | 1.95                    | Open | GND  | Open  | GND   | GND   | GND   |

| 1.175                   | GND  | GND  | Open  | GND   | GND   | Open  | 1.975                   | GND  | GND  | Open  | GND   | GND   | GND   |

| 1.2                     | Open | Open | GND   | GND   | GND   | Open  | 2                       | Open | Open | GND   | GND   | GND   | GND   |

| 1.225                   | GND  | Open | GND   | GND   | GND   | Open  | 2.025                   | GND  | Open | GND   | GND   | GND   | GND   |

| 1.25                    | Open | GND  | GND   | GND   | GND   | Open  | 2.05                    | Open | GND  | GND   | GND   | GND   | GND   |

| 1.275                   | GND  | GND  | GND   | GND   | GND   | Open  | 2.075                   | GND  | GND  | GND   | GND   | GND   | GND   |

# 16 Typical Operating Characteristics

# Power-on Response $V_{IN} = V_{OUT} + 0.3V, \ V_{OUT} = 3.3V, \ I_{OUT} = 2A, \\ C_{OUT} = 47\mu F / 10\mu F / 10\mu F, \ C_{FF} = 10nF$ $V_{OUT}, \ C_{NR/SS} = 1nF$ $V_{OUT}, \ C_{NR/SS} = 10nF$ $V_{OUT}, \ C_{NR/SS} = 47nF$ $V_{OUT}, \ C_{NR/SS} = 100nF$ $Time \ (4ms/Div)$

# Load Transient Response $\begin{array}{c} V_{OUT} \\ (20mV/Div) \\ offset \ 0.5V \\ \\ V_{IN} = 1.1V, \ V_{OUT} = 0.5V, \\ I_{OUT} = 10mA \ to \ 2A \ (1A/\mu s), \\ C_{OUT} = 47\mu F//10\mu F//10\mu F, \\ C_{NR/SS} = 10nF, \ C_{FF} = 10nF \\ \\ \\ I_{OUT} \\ (1A/Div) \\ \\ \end{array}$

Time (100µs/Div)

# 17 Operation

The RTQ2532E operates with a single supply input ranging from 1.1V to 6.5V and it can deliver a maximum current of 2A. The device features a high PSRR and low noise characteristics to provide a clean power supply to the application.

For further reduce device noise, a low-noise reference and an error amplifier are included. The NR/SS capacitor is employed to filter noise originating from the reference, while the feed-forward capacitor is used to mitigate noise from the error amplifier. With its high power-supply rejection ratio (PSRR), the RTQ2532E effectively minimizes the coupling of input supply noise to the output.

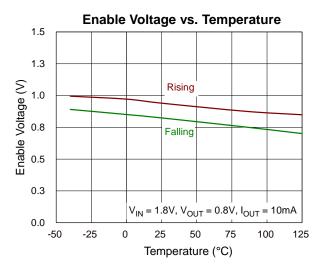

### 17.1 Enable and Shutdown

The RTQ2532E features an EN pin for external enable control, allowing the user to enable or disable the device. A VEN below 0.5V disables the regulator and enters shutdown mode, while a VEN above 1.1V enables the regulator. When the regulator is disabled, the ground current is reduced to a maximum of  $25\,\mu$ A. The enable circuitry includes hysteresis (typically 120mV) to accommodate relatively slowly-ramping analog signals.

If the EN pin is not utilized, it should be connected as close as possible to the largest capacitance on the input to prevent voltage drops on the VIN line from triggering the enable circuit.

### 17.2 VOUT Programming Pins

The RTQ2532E features a built-in matched feedback resistor network that allows for setting the output voltage. The output voltage can be programmed from 0.8V to 2.075V in increments of 25mV. This is achieved by connecting these programming pins 5, 6, 7, 9, 10, and 11 to ground. Additionally, connecting any of the VOUT programming pins to SNS will reduce the resistance of the upper portion of the resistor divider. As a result, the resolution of the VOUT programming is enhanced.

### 17.3 Programmable Soft-Start

The noise-reduction capacitor (CNR/SS) serves to reduce noise and to program the soft-start ramp-up duration upon activation. When both EN and UVLO exceed their respective threshold voltages, the RTQ2532E initiates a quick-start sequence that charges the noise reduction capacitor (CNR/SS); subsequently, the output voltage ramps up.

### 17.4 Power Good

The power-good circuit monitors the feedback pin voltage to indicate the status of the output voltage. The open-drain PGOOD pin requires an external pull-up resistor to an external supply, and any downstream device can receive the power-good signal as a logic input that can be used for sequencing. A pull-up resistor from  $10k\Omega$  to  $100k\Omega$  is recommended. Make sure that the external pull-up supply voltage results in a valid logic signal for the receiving device or devices.

After start-up, the PGOOD pin becomes high impedance when the feedback voltage exceeds VPGOOD\_HYS (typically 90% of the 0.5V reference voltage level). The PGOOD pin is pulled to GND when the feedback pin voltage falls below VPGOOD. Additionally, this pin is pulled low under protection conditions, during an enable (EN) shutdown, or throughout the soft-start process.

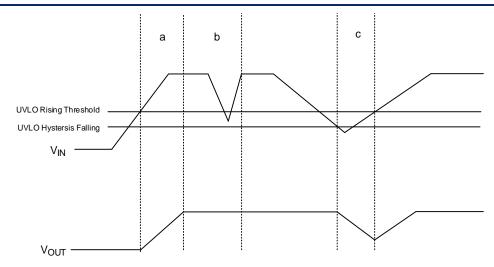

### 17.5 Undervoltage Lockout (UVLO)

The UVLO circuit monitors the input voltage to prevent the device from activating before VIN rises above the VUVLO threshold. The UVLO circuit also deactivates the output of the device when VIN falls below the lockout voltage (VUVLO\_R – VUVLO\_HYS). The UVLO circuit is designed to respond quickly to glitches on VIN and attempts to disable the output of the device if VIN collapses.

### 17.6 Internal Current Limit (ILIM)

The RTQ2532E continuously monitors the output current to protect the device against high load current faults or short-circuit events. The current limiting feature is not designed to allow operation above the rated current of the device. Operating the RTQ2532E continuously above its rated current can degrade the reliability of the device.

During a current limit event, the output voltage drops as the load impedance decreases. If the output voltage becomes too low, excessive power dissipation may cause the thermal shutdown.

To further protect the RTQ2532E, a foldback feature reduces the short-circuit current. This ensures the regulator is safeguarded from damage under all load conditions. If the load current demand surpasses the foldback current threshold before EN goes high, the device will remain disabled.

### 17.7 Over-Temperature Protection (OTP)

The RTQ2532E implements over-temperature protection. The device is disabled when the junction temperature (T<sub>J</sub>) exceeds 160°C (typical). The LDO automatically reactivates when the temperature falls below 140°C (typical). Note that the over-temperature protection feature is designed to protect the device under temporary overload conditions. The protection is activated outside of the absolute maximum ratings of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

### 17.8 Output Active Discharge

When the RTQ2532E is disabled, it discharges the LDO output (via VOUT pins) to ground through an internal current sink. The active discharge circuit is not designed for discharging a significant amount of output capacitance after the input supply has failed. Under such conditions, reverse current may flow from the output back to the input. It is recommended to implement external current protection when the device operates in a reverse voltage condition.

# 18 Application Information

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and reserve suitable design margin to ensure the functional suitability of their components and systems.

The RTQ2532E is a high-current, low-noise, high-accuracy, low-dropout linear regulator capable of sourcing up to 2A with a maximum dropout of 125mV. The input voltage operating range is from 1.1V to 6.5V. Additionally, the output voltage can be adjusted from 0.5V to 5.5V using external resistors. For output voltages between 0.5V and 2.075V, specific pins can be shorted via PCB layout to achieve the desired output voltage.

### 18.1 Output Voltage Setting

The output voltage of the RTQ2532E can be set using external resistors to achieve different output targets.

The output voltage is determined by the resistance values of R1 and R2, as shown in Figure 3, when external resistors are utilized. The values of R1 and R2 can be calculated for any voltage value using the following formula:

$$V_{OUT} = 0.5 \times \frac{R1 + R2}{R2}$$

Figure 3. Output Voltage Set by External Resistors

Alternatively, the RTQ2532E allows for the programming of the regulated output voltage level without external resistors by shorting pins 5, 6, 7, 9, 10, and 11 to ground. This method requires the SNS pin to be connected to VOUT. Pins 5, 6, 7, 9, 10, and 11 interface with internal resistor pairs, where each pin can be either grounded (active) or left unconnected (floating) to influence the output voltage.

Voltage programming is achieved by adding the internal reference voltage (VREF = 0.5V) to the cumulative voltages corresponding to each activated pin, as illustrated in Figure 4.

Figure 4. Output Setting without External Resistors

<u>Table 3</u> provides a summary of the voltage values corresponding to each active pin configuration for reference. By leaving all programming pins open, or floating, the output is programmed to the minimum possible output voltage, equal to VREF (0.5V). The maximum achievable output voltage is 2.075V when pins 5, 6, 7, 9, 10, and 11 are simultaneously shorted to ground.

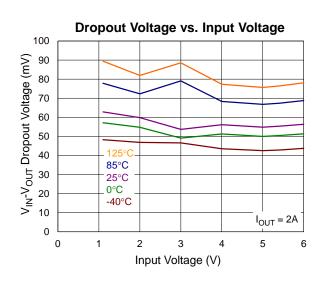

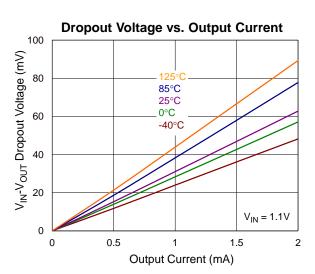

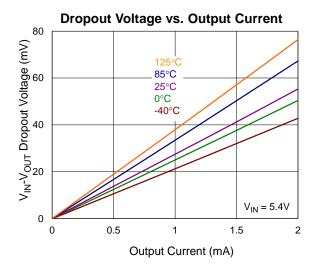

### 18.2 Dropout Voltage

The dropout voltage, denoted as VDROP, is the voltage difference between the VIN and VOUT pins while operating at a specific output current (IRATED). The dropout voltage, VDROP, can also be described as the voltage drop across the pass-FET at a specific output current (IRATED) while the pass-FET is fully operating in the ohmic region and can be characterized by a resistance RDS(ON). Thus, the dropout voltage can be defined as VDROP = VIN - VOUT = RDS(ON) x IRATED. For normal operation, it is recommended that the LDO operates within the range VIN > (VOUT + VDROP) to ensure optimal transient response and PSRR performance. However, operation in the ohmic region will degrade the performance severely.

### 18.3 CIN and COUT Selection

The RTQ2532E is designed to support low series resistance (ESR) ceramic capacitors. X7R, X5R, and COG rated ceramic capacitors are recommended for their stable capacitance across different temperatures. In contrast, Y5V-rated capacitors are not recommended due to their significant capacitance variations with temperature.

However, the capacitance of ceramic capacitors varies with operating voltage and temperature. Design engineers must be aware of these characteristics. It is usually recommended to derate ceramic capacitors by 50% to account for their capacitance variance under different conditions. A  $47\mu F$  or greater output ceramic capacitor (or  $22\mu F$  effective capacitance) is suggested to ensure stability. Input capacitance is selected to minimize transient input drop during load current steps. For general applications, an input capacitor of at least  $47\mu F$  is highly recommended for minimal input impedance. If the trace inductance between the RTQ2532E input pin and power supply is high, a fast load transient can cause VIN voltage level ringing above the absolute maximum voltage rating which damages the device. Adding more input capacitors—can restrict the ringing and keep it below the device's absolute maximum ratings.

Generally, using a  $47\mu F$  1210-sized ceramic capacitor in parallel with two  $10\mu F$  0805-sized ceramic capacitors ensures the required minimum effective capacitance for high input voltage and high output voltage conditions. Place these capacitors as close to the pins as possible for optimum performance and to ensure stability.

### 18.4 Feed-Forward Capacitor (CFF)

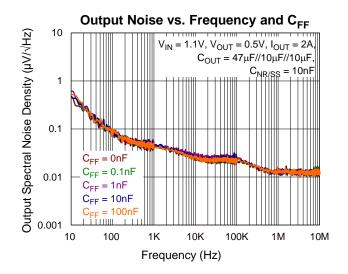

The RTQ2532E is designed to be stable without the external feed-forward capacitor (CFF). However, adding a 10nF external feed-forward capacitor optimizes the transient response, noise suppression, and PSRR performance. Utilizing a higher capacitance value for CFF is possible, but it will result in a prolonged start-up time, and the power-good signal may mistakenly indicate that the output voltage has stabilized.

### 18.5 Soft-Start and Noise Reduction (CNR/SS)

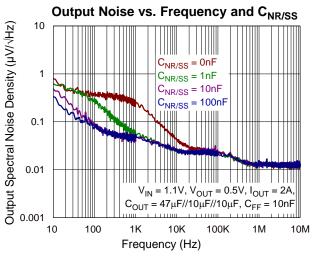

The RTQ2532E is designed for a programmable, monotonic soft-start time during the output voltage rise, achieved by connecting an external capacitor (CNR/SS) to the NR/SS pin. For general applications, using an external CNR/SS is recommended to minimize in-rush current and reduce noise from the internal reference.

During the monotonic start-up procedure, the error amplifier of the RTQ2532E regulates the output by tracking the voltage ramp of the external soft-start capacitor (CNR/SS), until it reaches the internal reference of 0.5V. The soft-start ramp time can be calculated using Equation a1, which is a function of the soft-start charging current (INR/SS), the soft-start capacitance (CNR/SS), and the internal reference (VREF).

$$t_{SS} = \frac{\left(V_{REF} \times C_{NR/SS}\right)}{I_{NR/SS}} \tag{a1}$$

For noise-reduction, CNR/SS works with an internal noise-reduction resistor to form a low-pass filter (LPF), filtering out noise from the internal bandgap reference before it is amplified by the error amplifier, thus reducing the total device noise floor.

### 18.6 Input Inrush Current

During start-up, the input Inrush current into the VIN pin consists of the sum of load current and the charging current of the output capacitor. Measuring the inrush current is challenging as it requires removal of the input capacitor, which is not recommended. Generally, the soft-start inrush current can be estimated using Equation b1, where VOUT(t) represents the instantaneous output voltage of the power-on ramp, dVOUT(t)/dt is the slope of the VOUT ramp, and RLOAD is the resistive load impedance.

$$I_{OUT}\left(t\right) = \frac{\left(C_{OUT} \times dV_{OUT}\left(t\right)\right)}{dt} + \left(\frac{V_{OUT}\left(t\right)}{R_{LOAD}}\right) \quad \text{(b1)}$$

### 18.7 Undervoltage Lockout (UVLO)

The Undervoltage Lockout (UVLO) threshold is the minimum input operational voltage range that ensures the device stays disabled. Figure 5 illustrates that the UVLO circuits are triggered during three different input voltage events (durations a, b, and c), assuming VEN ≥ VEN\_R all the time. During duration "a", the input voltage starts rising. When VIN is over the UVLO rising threshold, VOUT starts the power-on process. Then when VOUT reaches the target level, it is under regulation. During duration "b", although the power line has a voltage drop, it does not drop below the UVLO low threshold (falling threshold). As a result, the device maintains normal operation, and VOUT is still regulated. During duration "c", VIN drops below the UVLO falling threshold, so the control loop is disabled and there is no regulation. Meanwhile, VOUT drops. For general applications, an instant power line transient with a long power trace at the VIN pin may have VIN level unstable and force a trap, as shown in the duration "c", which makes VOUT collapse. In this case, adding additional input capacitance or optimizing the input trace layout on the PCB can effectively to enhance the stabilization of the input power.

Figure 5. Under Voltage Lockout Trigging Conditions and Output Variation

### 18.8 Power-Good (PGOOD) Function

The power-good function monitors the voltage level at the feedback pin to determine if the output voltage status is within normal parameters. This function allows other devices to utilize the RTQ2532E's power-good signal as a logic signal that can be used for sequencing system applications. The PGOOD pin has an open-drain configuration, requiring an external pull-up resistor connected to an external supply for proper functionality. A pull-up resistor with a value ranging from  $10k\Omega$  to  $100k\Omega$  is recommended. The minimum value of  $10k\Omega$  is based on the maximum pull-down capability of the power-good transistor, while the maximum value of  $100k\Omega$  takes into account the highest leakage current that can occur at the power-good node.

Figure 6 demonstrates some PGOOD scenarios in the relation to VIN, EN, and the protection status. During duration a, VEN exceeds the VEN\_H threshold, indicating that the device is under operation. In this phase, VOUT starts to increase (the rise time is related to the soft-start capacitor CNR/SS). When VOUT surpasses the PGOOD hysteresis threshold, the reflected feedback voltage VFB exceeds the VPGOOD\_HYS threshold causing the PGOOD pin to enter a high-impedance state. The duration b indicates fault conditions such as OTP, OCP, or a significant output voltage drop due to rapid load changes. If VFBfalls below the VPGOOD threshold, VPGOOD is pulled to GND, which indicates that the output voltage is not within the acceptable range. During duration c, VOUT has a minor drop, which is not lower than the PGOOD falling threshold; the PGOOD pin remains in a high-impedance. Finally, in duration d, when VEN transitions to a low logic level, VPGOOD is pulled to GND.

Figure 6. PGOOD Trigger Scenario with Different Operating Status

RTQ2532E DS-00

### 18.9 Reverse Current Protection

Reverse current flows from VOUT to VIN through the body diode of the pass element, instead of the normal conduction channel, if the maximum VOUT exceeds VIN + 0.3V; in this case, the pass element may be damaged.

For example, if the output is biased above the input supply voltage level or the input supply has an instant drop at light load operation that makes VIN < VOUT. As shown in <u>Figure 7</u>, an external Schottky diode can be added to prevent the pass element from being damaged by the reverse current.

Figure 7. Application Circuit for Reverse Current Protection

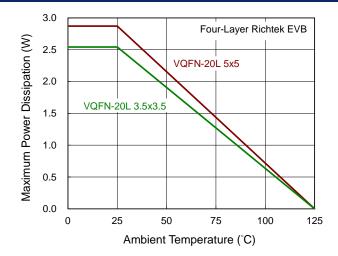

### 18.10 Thermal Considerations

The junction temperature should never exceed the absolute maximum junction temperature TJ(MAX), listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$PD(MAX) = (TJ(MAX) - TA)/\theta JA$

where TJ(MAX) is the maximum junction temperature, TA is the ambient temperature, and  $\theta JA$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta$ JA(EVB), is highly package dependent. For a VQFN-20L 5x5 package, the thermal resistance,  $\theta$ JA (EVB), is 34.82°C/W on a standard high effective-thermal-conductivity four-layer test board.

For a VQFN-20L 3.5x3.5 package, the thermal resistance,  $\theta$ JA (EVB), is 39.33°C/W on a standard high effective-thermal- conductivity four-layer test board. The maximum power dissipation at TA = 25°C can be calculated as below:

$PD(MAX) = (125^{\circ}C - 25^{\circ}C) / (34.82^{\circ}C/W) = 2.87W \text{ for a VQFN-20L 5x5 package}$

$PD(MAX) = (125^{\circ}C - 25^{\circ}C) / (39.33^{\circ}C/W) = 2.54W \text{ for a VQFN-20L } 3.5x3.5 \text{ package.}$

The maximum power dissipation depends on the operating ambient temperature for the fixed TJ(MAX) and the thermal resistance,  $\theta$ JA EVB). The derating curves in <u>Figure 8</u> allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

22

Figure 8. Derating Curve of Maximum Power Dissipation

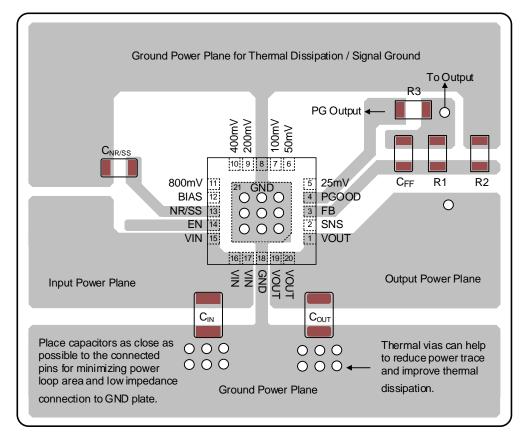

### 18.11 Layout Considerations

For optimal of the RTQ2532E, the PCB layout suggestions below are recommended.

- 1. All circuit components should be placed on the same side and as close to the respective LDO pins as possible.

- 2. Place the ground return path in close proximity to the input and output capacitors.

- 3. Ensure the ground plane is connected with a wide copper surface to enhance thermal dissipation.

- 4. Avoid using vias and long power traces for the input and output capacitors connections, as they can negatively affect performance.

- 5. <u>Figure 9</u> show a layout example that reduces conduction trace loops, helping to minimize inductive parasitic and load transient effects, while improving circuit stability.

Figure 9. PCB Layout Guide for VQFN-20L 3.5x3.5 package and VQFN-20L 5x5 package

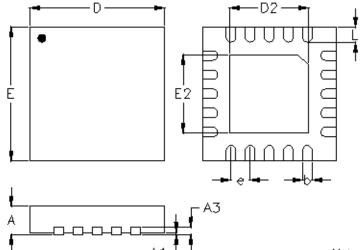

# 19 Outline Dimension

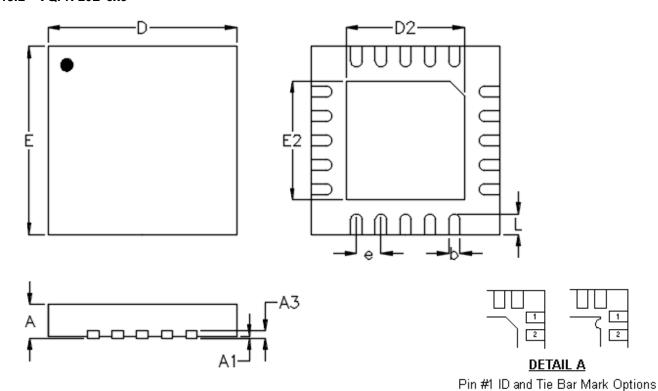

### 19.1 VQFN-20L 3.5x3.5

Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol  | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|---------|------------|----------------|----------------------|-------|--|

| Symbol  | Min        | Max            | Min                  | Max   |  |

| Α       | 0.800      | 1.000          | 0.031                | 0.039 |  |

| A1      | 0.000      | 0.050          | 0.000                | 0.002 |  |

| А3      | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b       | 0.200      | 0.300          | 0.008                | 0.012 |  |

| D       | 3.400      | 3.600          | 0.134                | 0.142 |  |

| D2      | 2.000      | 2.100          | 0.079                | 0.083 |  |

| E       | 3.400      | 3.600          | 0.134                | 0.142 |  |

| E2      | 2.000      | 2.100          | 0.079                | 0.083 |  |

| е       | 0.500      |                | 0.0                  | )20   |  |

| L 0.350 |            | 0.450          | .450 0.014           |       |  |

V-Type 20L QFN 3.5x3.5 Package

## 19.2 VQFN-20L 5x5

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | In Millimeters | Dimensions In Inches |       |  |

|--------|--------------|----------------|----------------------|-------|--|

| Symbol | Min. Max.    |                | Min.                 | Max.  |  |

| Α      | 0.800        | 1.000          | 0.031                | 0.039 |  |

| A1     | 0.000        | 0.050          | 0.000                | 0.002 |  |

| А3     | 0.175        | 0.250          | 0.007                | 0.010 |  |

| b      | 0.250        | 0.350          | 0.010                | 0.014 |  |

| D      | 4.950        | 5.050          | 0.195                | 0.199 |  |

| D2     | 3.100        | 3.200          | 0.122                | 0.126 |  |

| E      | 4.950        | 5.050          | 0.195                | 0.199 |  |

| E2     | 3.100        | 3.200          | 0.122                | 0.126 |  |

| е      | 0.650        |                | 0.026                |       |  |

| L      | 0.500        | 0.600          | 0.020                | 0.024 |  |

V-Type 20L QFN 5x5 Package

# 20 Footprint Information

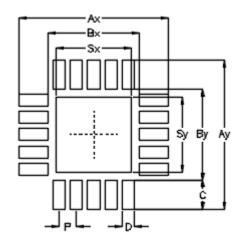

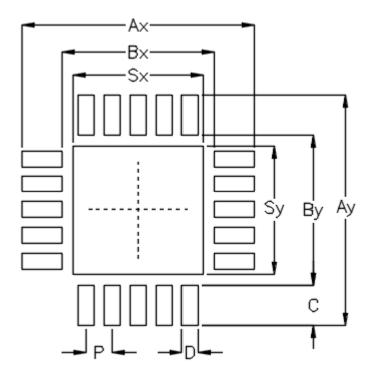

### 20.1 VQFN-20L 3.5x3.5

| Dookogo              | Number of |      | Footprint Dimension (mm) |      |      |      |      |      |      |      |           |

|----------------------|-----------|------|--------------------------|------|------|------|------|------|------|------|-----------|

| Package              | Pin       | Р    | Ax                       | Ау   | Вх   | Ву   | С    | D    | Sx   | Sy   | Tolerance |

| V/W/U/XQFN3.5*3.5-20 | 20        | 0.50 | 4.30                     | 4.30 | 2.60 | 2.60 | 0.85 | 0.35 | 2.15 | 2.15 | ±0.05     |

### 20.2 VQFN-20L 5x5

| Dooleage         | Number of |      | Footprint Dimension (mm) |      |      |      |      |      |      |      |           |

|------------------|-----------|------|--------------------------|------|------|------|------|------|------|------|-----------|

| Package          | Pin       | Р    | Ax                       | Ау   | Вх   | Ву   | С    | D    | Sx   | Sy   | Tolerance |

| V/W/U/XQFN5*5-20 | 20        | 0.65 | 5.80                     | 5.80 | 3.80 | 3.80 | 1.00 | 0.40 | 3.25 | 3.25 | ±0.05     |

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# 21 Packing Information

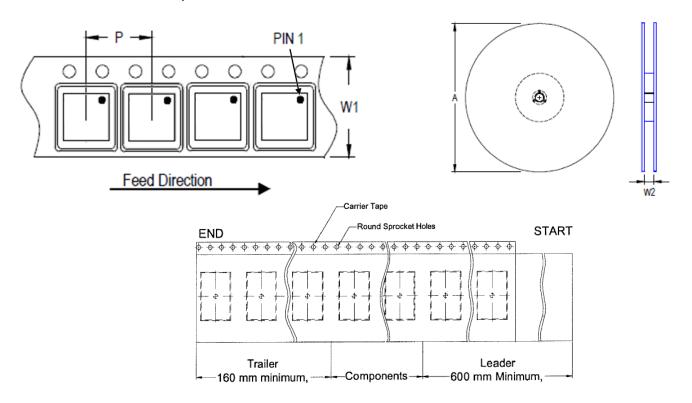

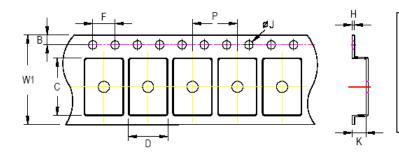

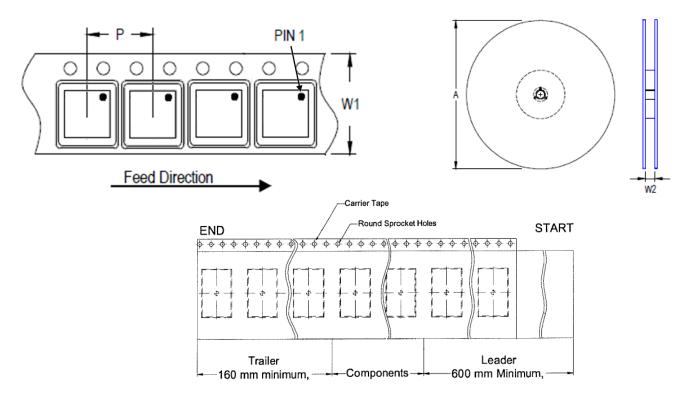

### 21.1 QFN/DFN 3.5x3.5 Tape and Reel Data

|                    | Tape Size | Pocket Pitch |      |      | Units       | Trailer | Leade | Reel Width (W2) |  |

|--------------------|-----------|--------------|------|------|-------------|---------|-------|-----------------|--|

| Package Type       | (W1) (mm) | (P) (mm)     | (mm) | (in) | per<br>Reel | (mm)    | r(mm) | Min./Max. (mm)  |  |

| QFN/DFN<br>3.5x3.5 | 12        | 8            | 180  | 7    | 1,500       | 160     | 600   | 12.4/14.4       |  |

C, D, and K are determined by component size.

The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tono Cizo | W1     | Р     |       | В      |        | F     |       | ØJ    |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|

| Tape Size | Max.   | Min.  | Max.  | Min.   | Max.   | Min.  | Max.  | Min.  | Max.  | Max.  |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.6mm |

### 21.2 QFN/DFN 3.5x3.5 Tape and Reel Packing

| Step | Photo/Description                      | Step | Photo/Description                                     |

|------|----------------------------------------|------|-------------------------------------------------------|

| 1    | Reel 7"                                | 4    | RICHTEK TOWNS TOWN TOWN TOWN TOWN TOWN TOWN TOWN TOWN |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box                          |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                                    |

| Container | R    | eel   | Вох   |       |       | Carton   |                   |         |  |

|-----------|------|-------|-------|-------|-------|----------|-------------------|---------|--|

| Package   | Size | Units | Item  | Reels | Units | Item     | Boxes             | Unit    |  |

| QFN/DFN   | 7"   | 4.500 | Box A | 3     | 4,500 | Carton A | 12                | 54,000  |  |

| 3.5x3.5   | 7    | 1,500 | Box E | 1     | 1,500 | For C    | ombined or Partia | l Reel. |  |

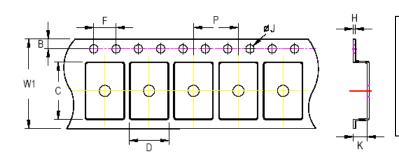

### 21.3 QFN/DFN 5x5 Tape and Reel Data

| Deeleses Tons  | Tape Size | Pocket Pitch | Reel S | ize (A) | Units per | Trailer | Leade | Reel Width (W2) |

|----------------|-----------|--------------|--------|---------|-----------|---------|-------|-----------------|

| Package Type   | (W1) (mm) | (P) (mm)     | (mm)   | (in)    | Reel      | (mm)    | r(mm) | Min./Max. (mm)  |

| QFN/DFN<br>5x5 | 12        | 8            | 180    | 7       | 1,500     | 160     | 600   | 12.4/14.4       |

C, D, and K are determined by component size.

The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | Р     |       | В      |        | F     |       | ØJ    |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|

| Tape Size | Max.   | Min.  | Max.  | Min.   | Max.   | Min.  | Max.  | Min.  | Max.  | Max.  |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.6mm |

### 21.4 QFN/DFN 5x5 Tape and Reel Packing

| Step | Photo/Description                      | Step | Photo/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Reel 7"                                | 4    | RICHTEK / NOW 1 TO STORY OF THE PROPERTY OF TH |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Container   | R    | eel   | Вох   |       |       | Carton   |                    |        |  |

|-------------|------|-------|-------|-------|-------|----------|--------------------|--------|--|

| Package     | Size | Units | Item  | Reels | Units | Item     | Boxes              | Unit   |  |

| OEN/DEN 5 5 | 7"   | 4.500 | Box A | 3     | 4,500 | Carton A | 12                 | 54,000 |  |

| QFN/DFN 5x5 | 7"   | 1,500 | Box E | 1     | 1,500 | For C    | ombined or Partial | Reel.  |  |

### 21.5 Packing Material Anti-ESD Property

| Surface<br>Resistance | Aluminum<br>Bag                     | Reel                                | Cover<br>tape                       | Carrier<br>tape                     | Tube                                | Protection<br>Band                  |

|-----------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega/{\rm cm}^2$   | 10 <sup>4</sup> to 10 <sup>11</sup> |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

RICHTEK

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

is a registered trademark of Richtek Technology Corporation.

22 Datasheet Revision History

| Version | Date     | Description | Item                                       |

|---------|----------|-------------|--------------------------------------------|

| 00      | 2024/4/2 | Final       | Title on P1 Packing Information on P29, 31 |