# **RTQ2078-QF**

# Functional Safety PMIC for Automotive Camera Sensor/ Module

# 1 General Description

The RTQ2078-QF is a highly integrated PMIC designed for automotive camera applications. It includes three step-down converters, and one high PSRR low-dropout (LDO) regulator

The high-voltage step-down converter operates with an input voltage range of up to 24V and is capable of sustaining a 36V load dump. It is suitable for a direct connection to a 12V battery or Power Over Coax (PoC) connection.

The RTQ2078-QF offers overvoltage and undervoltage monitors, and fault status reported by I<sup>2</sup>C for system fault reporting purpose.

The device offers system design flexibility with I<sup>2</sup>C or factory-trimmed configurable functions, including adjustable output voltage for each channel, customizable power-on sequencing, and overvoltage (OV) or undervoltage (UV) monitor threshold voltage. The RTQ2078-QF is available in a WET-UQFN-16L 3x3 (FC) package with wettable flanks.

The recommended junction temperature range is  $-40^{\circ}$ C to 125°C, and the ambient temperature range is  $-40^{\circ}$ C to 125°C.

# 2 Applications

- Functional Safety Related Automotive Camera Modules

- Surround View Camera

- Front View Camera

- Rear View Camera

- Dash Cam DVR

- Driver Monitoring System

- · Cabin Monitor

DSQ2078-QF-00

### 3 Features

- AEC-Q100 Grade 1 Qualified

- Compliance with ISO 26262 ASIL B

- Power-On Built-In Self Test (BIST) for OV/UV Monitors, I<sup>2</sup>C Cyclic Redundancy Check (CRC), and OTP Register CRC Protection

- Three Step-Down Converters (HVBuck1, LVBuck2, and LVBuck3) with Peak-Current Mode PWM Operation and PSM Mode for Sentry Mode via I<sup>2</sup>C Setting

- Fixed Switching Frequency at 2.1MHz

- EMI Reduction features including Spread Spectrum and Phase-Shift Operation

- HVBuck1 Supports Input Voltage from 4V to 24V with Load Dump Protection (36V for ≤ 400ms Transient), Adjustable Output Voltage, and up to 1.5A Output Current

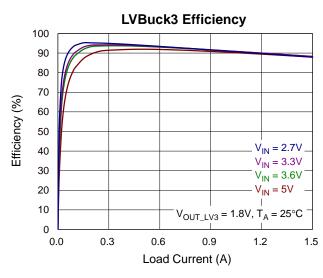

- LVBuck2 and LVBuck3 Support Input Voltage from 2.7V to 5V, Adjustable Output Voltage and up 1.5A Output Current

- Pins Related to LVBuck2/LVBuck3 Can Floating if the Channel is Unused

- Low Dropout Regulator (LDO)

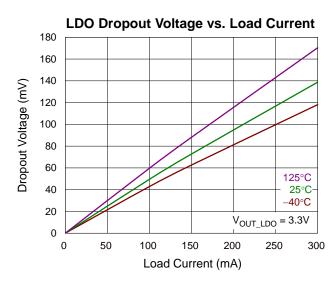

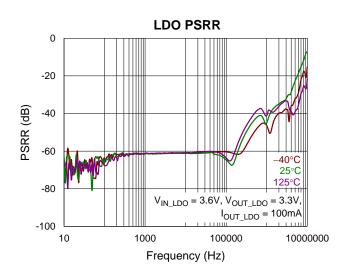

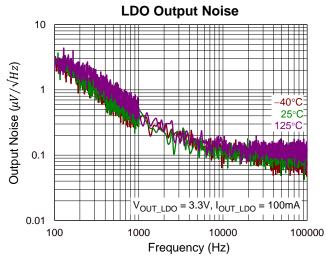

- LDO with 2.7V to 5V Input Voltage, Adjustable Output Voltage, up to 0.3A Output Current, and High PSRR with 0.1A Output Current (60dB at 100kHz, 40dB at 1MHz)

- Input and Output Functions

- Power and Error Status Indication via PGOOD

- Small Form Factor Wettable WET-UQFN-16L 3x3 (FC) Package with Compact BOM

- Ambient Temperature Range: -40°C to 125°C

- Junction Temperature Range: –40°C to 125°C

May

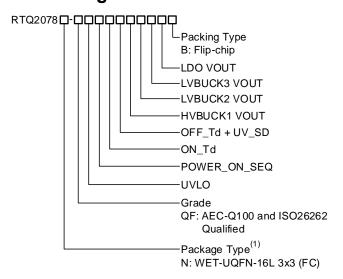

# 4 Ordering Information

### Note 1.

Richtek products are Richtek Green Policy compliant and marked with <sup>(1)</sup> indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

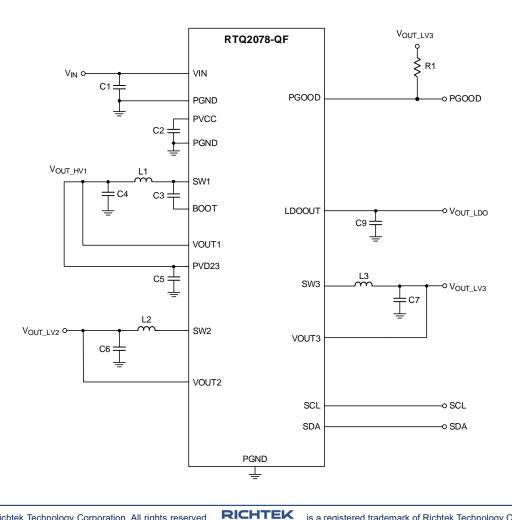

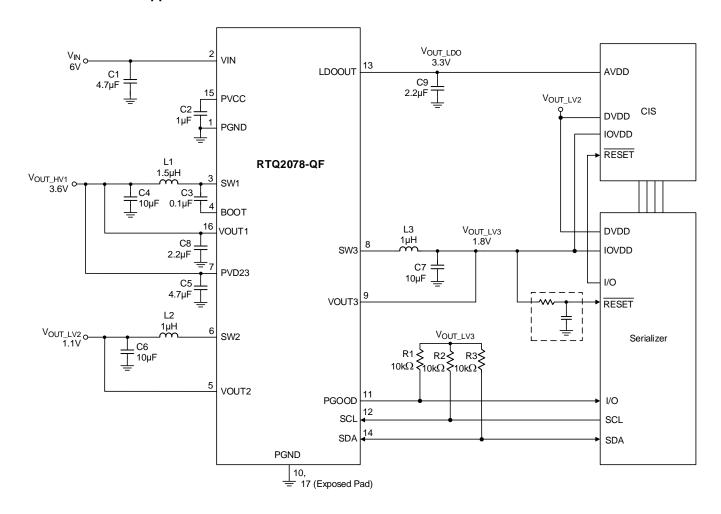

# **6 Simplified Application Circuit**

# **5 Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

# **Table of Contents**

| 1  | General Description1                |    | 17.7 Channel Floating Allowable2               | 22 |

|----|-------------------------------------|----|------------------------------------------------|----|

| 2  | Applications1                       |    | 17.8 Reboot Operation2                         | 22 |

| 3  | Features 1                          |    | 17.9 Power-Good and Error Indication2          | 22 |

| 4  | Ordering Information2               | 18 | Application Information2                       | 23 |

| 5  | Marking Information2                |    | 18.1 Device and Channel Enable Control2        | 23 |

| 6  | Simplified Application Circuit2     |    | 18.2 Device Register Configuration Control2    | 23 |

| 7  | Pin Configuration4                  |    | 18.3 Device State Machine2                     | 23 |

| 8  | Functional Pin Description4         |    | 18.4 Power Sequence and Interval Time Setting2 | 27 |

| 9  | Functional Block Diagram 6          |    | 18.5 Power-On/Off Control2                     | 27 |

| 10 | Absolute Maximum Ratings7           |    | 18.6 Output Voltage Setting2                   | 29 |

| 11 | ESD Rating7                         |    | 18.7 Reset Function                            | 29 |

| 12 | Recommended Operating Conditions7   |    | 18.8 Protection Features2                      | 29 |

| 13 | Thermal Information7                |    | 18.9 Inductor Selection                        | 33 |

| 14 | Electrical Characteristics 8        |    | 18.10 Input and Output Capacitor Selection3    | 33 |

|    | 14.1 System Characteristics         |    | 18.11 I <sup>2</sup> C Interface               | 34 |

| 15 | Typical Application Circuit18       |    | 18.12 Thermal Considerations                   | 35 |

|    | 15.1 General CIS Application18      |    | 18.13 Layout Considerations                    | 36 |

| 16 | Typical Operating Characteristics19 | 19 | Functional Register Description                | 38 |

| 17 | Operation21                         | 20 | Outline Dimension                              | 57 |

|    | 17.1 System Undervoltage and        | 21 | Footprint Information                          | 58 |

|    | Overvoltage Protection21            | 22 | Packing Information                            | 59 |

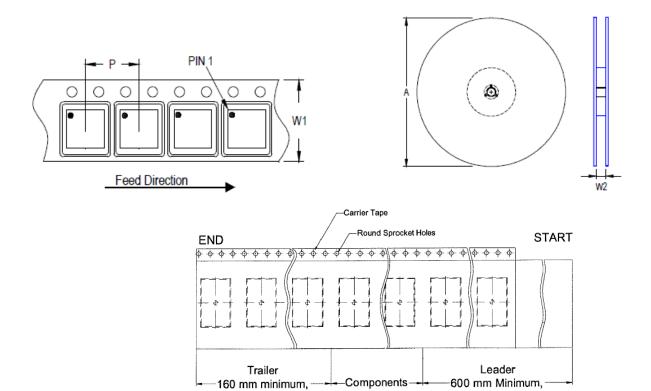

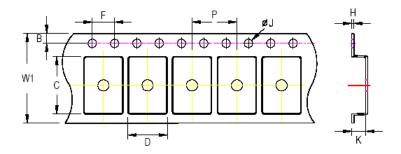

|    | 17.2 Over-Temperature Protection21  |    | 22.1 Tape and Reel Data5                       | 59 |

|    | 17.3 Pre-Regulator21                |    | 22.2 Tape and Reel Packing6                    | 30 |

|    | 17.4 Peak Current Mode Control21    |    | 22.3 Packing Material Anti-ESD Property6       | 31 |

|    | 17.5 Spread Spectrum Operation21    | 23 | Datasheet Revision History6                    | ô2 |

|    | 17.6 Phase-Shift Operation          |    |                                                |    |

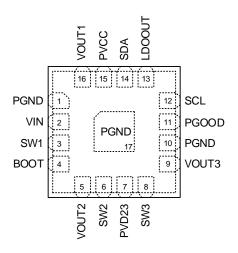

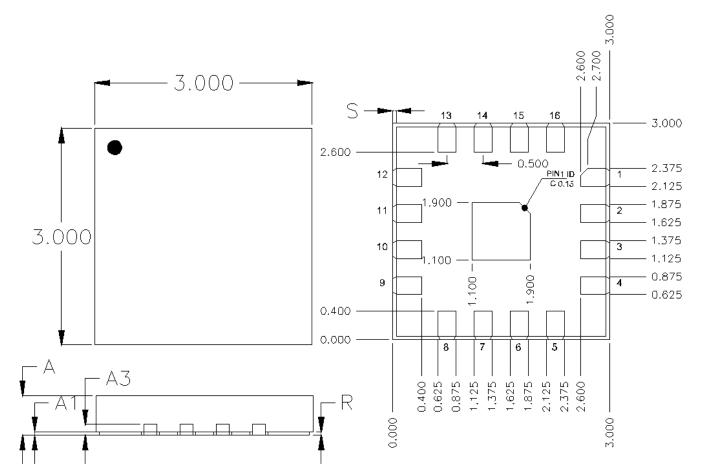

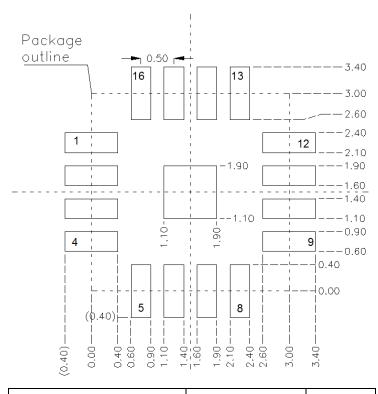

# 7 Pin Configuration

(TOP VIEW)

WET-UQFN-16L 3x3 (FC)

# **8 Functional Pin Description**

| Pin No.                    | Pin Name | Pin Function                                                                                                                                                   |

|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 10,<br>17 (Exposed Pad) | PGND     | IC thermal pad and power ground. It must be connected to the main ground plane for proper operation.                                                           |

| 2                          | VIN      | HVBuck1 and PMIC system input source power.                                                                                                                    |

| 3                          | SW1      | HVBuck1 switch node.                                                                                                                                           |

| 4                          | воот     | HVBuck1 BOOT pin.                                                                                                                                              |

| 5                          | VOUT2    | LVBuck2 output voltage feedback. It is recommended to directly connect the output capacitor node to this pin for better regulation.                            |

| 6                          | SW2      | LVBuck2 switch node.                                                                                                                                           |

| 7                          | PVD23    | LVBuck2/3 input source power. Assume that PVD23 connects to the HVbuck1 output.                                                                                |

| 8                          | SW3      | LVBuck3 switch node.                                                                                                                                           |

| 9                          | VOUT3    | LVBuck3 output voltage feedback. It is recommended to directly connect the output capacitor node to this pin for better regulation.                            |

| 11                         | PGOOD    | Open-drain output, PMIC power status for indication. When PGOOD is in a high state, it indicates that all outputs are functioning normally.                    |

| 12                         | SCL      | I <sup>2</sup> C interface serial clock input pin, open-drain. Connect to an external pull-up resistor is required.                                            |

| 13                         | LDOOUT   | LDO output pin. It is recommended to directly connect the output capacitor node to this pin for better regulation.                                             |

| 14                         | SDA      | I <sup>2</sup> C interface serial data pin, open-drain. Connect to an external pull-up resistor is required.                                                   |

| 15                         | PVCC     | Internal analog power output. Connect a $1\mu F$ ceramic decouple capacitor between this pin and ground. Additional external loading to this pin is forbidden. |

| Pi | n No. | Pin Name | Pin Function                                                                                                                                                                                                                       |

|----|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 16    |          | HVBuck1 output voltage feedback. It is recommended to directly connect the output capacitor node to this pin for better regulation. This pin is also the LDO input source power and transmits the power through the internal path. |

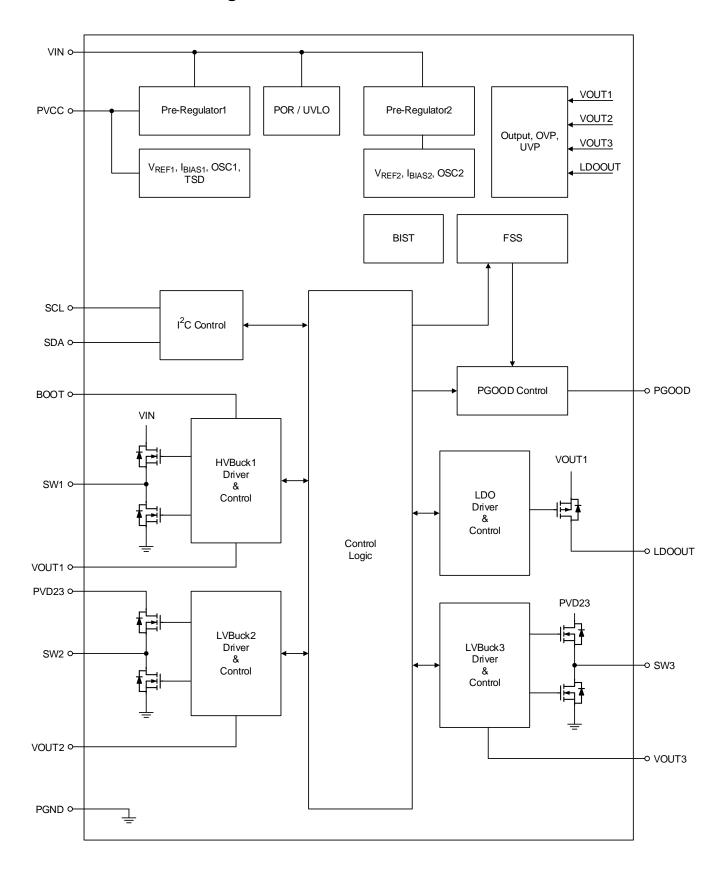

# 9 Functional Block Diagram

## 10 Absolute Maximum Ratings

### (Note 2)

| • VIN, SW1                                      | -0.3V to 36V   |

|-------------------------------------------------|----------------|

| • BOOT                                          | -0.3V to 36V   |

| • BOOT to SW1                                   | –0.3V to 5V    |

| • VOUT1, PVD23, VOUT2, SW2, SW3, VOUT3, LDOOUT, |                |

| PVCC, PGOOD, SDA, SCL                           | -0.3V to 6.5V  |

| Lead Temperature (Soldering, 10 sec.)           | 260°C          |

| • Junction Temperature                          | 150°C          |

| Storage Temperature Range                       | –65°C to 150°C |

Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

# 11 ESD Rating

### (Note 3)

ESD Susceptibility HBM (Human Body Model) ------ 2kV

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

# 12 Recommended Operating Conditions

### (Note 4)

| Supply Voltage, VIN        | 4V to 24V     |

|----------------------------|---------------|

| Supply Voltage, PVD23      | 2.7V to 5V    |

| Ambient Temperature Range  | 40°C to 125°C |

| Junction Temperature Range | 40°C to 125°C |

Note 4. The device is not guaranteed to function outside its operating conditions.

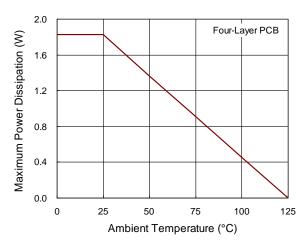

### 13 Thermal Information

### (Note 5)

|                     | Thermal Parameter                                       | WET-UQFN-16L 3x3 | Unit |

|---------------------|---------------------------------------------------------|------------------|------|

| θЈА                 | Junction-to-ambient thermal resistance (JEDEC standard) | 54.87            | °C/W |

| θJC(Top)            | Junction-to-case (top) thermal resistance               | 5.73             | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 12.4             | °C/W |

| θЈВ                 | Junction-to-board thermal resistance                    | 24               | °C/W |

Note 5. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

## 14 Electrical Characteristics

$(T_A = T_J = -40^{\circ}C \text{ to } 125^{\circ}C, \ V_{IN} = 6V, \ V_{OUT\_HV1} = 3.6V, \ V_{OUT\_LV2} = 1.1V, \ V_{OUT\_LV3} = 1.8V, \ V_{OUT\_LDO} = 3.3V, \ unless otherwise$ specified.)

| Parameter                                    | Symbol            | Test Conditions                                                                                                                                        | Min    | Тур  | Max    | Unit |

|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|------|

| System                                       |                   |                                                                                                                                                        |        |      |        |      |

| VIN Undervoltage<br>Lock-out Falling         | Vuvlo_f           |                                                                                                                                                        | 3.135  | 3.3  | 3.465  | V    |

| VIN Undervoltage<br>Lock-out Rising          | Vuvlo_r           |                                                                                                                                                        | 3.61   | 3.8  | 3.99   | V    |

| VIN Overvoltage<br>Rising Protection         | VOVP_VIN          |                                                                                                                                                        | 24.735 | 25.5 | 26.265 | V    |

| VIN Overvoltage<br>Hysteresis                | VOVP_HYS_VIN      |                                                                                                                                                        | 5      | 6    | 7      | V    |

| Pre-Regulator (N                             | <u>ote 6</u> )    |                                                                                                                                                        |        |      |        |      |

| PVCC Voltage<br>Range                        | VPVCC             |                                                                                                                                                        | 4.4    | 4.65 | 4.9    | V    |

| CH1_HVBuck1                                  |                   |                                                                                                                                                        |        |      |        |      |

| Input Voltage<br>Range                       | VIN_HV1           | VIN_HV1 = VIN                                                                                                                                          | 4      |      | 24     | V    |

| Output Voltage<br>Range                      | Vout_HV1          | VIN_HV1 = 4V to 24V                                                                                                                                    | 2.7    |      | 5      | V    |

| Output Voltage<br>Accuracy                   | VOUT_ACC_HV1_FPWM | V <sub>OUT</sub> <sub>HV1</sub> = 2.7V to 5V,<br>V <sub>IN</sub> <sub>HV1</sub> = 6V, 9V, 12V,<br>I <sub>OUT</sub> <sub>HV1</sub> = 0 to 1.5A,<br>FPWM | -1.5   |      | 1.5    | %    |

| Soft-Start Time                              | tss_HV1           | Time from VOUT_HV1 to rise from 10% to 90% of target value, no load                                                                                    | 500    | 1000 | 1500   | μS   |

| Switching<br>Frequency                       | fsw_HV1           |                                                                                                                                                        | 1.89   | 2.1  | 2.31   | MHz  |

| Spread Spectrum<br>Range                     | fssp              |                                                                                                                                                        |        | 12   |        | %    |

| High-Side<br>MOSFET On-<br>Resistance        | Ron_ug_hv1        |                                                                                                                                                        |        | 210  |        | mΩ   |

| Low-Side<br>MOSFET On-<br>Resistance         | RON_LG_HV1        |                                                                                                                                                        |        | 120  |        | mΩ   |

| Minimum On-Time                              | tmin_on_hv1       |                                                                                                                                                        |        |      | 40     | ns   |

| Minimum Off-Time                             | tMIN_OFF_HV1      |                                                                                                                                                        |        |      | 50     | ns   |

| Positive Inductor<br>Peak Current Limit      | ICL_PK_HV1        |                                                                                                                                                        | 1.9    | 2.5  | 3.1    | А    |

| Positive Inductor<br>Valley Current<br>Limit | ICL_VALLEY_HV1    |                                                                                                                                                        |        | 1.6  |        | А    |

| Negative Inductor<br>Peak Current Limit      | ICL_N_PK_HV1      | HVBuck1 in FPWM                                                                                                                                        | 1.3    | 1.8  | 2.3    | А    |

DSQ2078-QF-00

| Parameter                                                                 | Symbol            | Test Conditions                                                                                                   | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Output Discharge<br>Resistor                                              | RDIS_HV1          |                                                                                                                   | 20   | 50   | 80   | Ω    |

| HVBuck1 Output<br>Undervoltage<br>Falling Threshold<br>Detection          | VUVP_HV1          |                                                                                                                   |      | 80   |      | %    |

| HVBuck1 Output<br>Undervoltage<br>Falling Threshold<br>Detection Accuracy | VUVP_ACC_HV1      |                                                                                                                   | -1.3 |      | 1.3  | %    |

| HVBuck1 Output<br>Overvoltage Rising<br>Threshold<br>Detection            | VOVP_HV1          |                                                                                                                   |      | 110  |      | %    |

| HVBuck1 Output<br>Overvoltage Rising<br>Threshold<br>Detection Accuracy   | Vovp_acc_hv1      |                                                                                                                   | -1.3 |      | 1.3  | %    |

| CH2_LVBuck2                                                               |                   |                                                                                                                   |      |      |      |      |

| Input Voltage<br>Range                                                    | VIN_LV2           |                                                                                                                   | 2.7  |      | 5    | V    |

| Output Voltage<br>Range                                                   | VOUT_LV2          |                                                                                                                   | 0.6  | 1.1  | 1.9  | ٧    |

| Output Voltage<br>Accuracy                                                | VOUT_ACC_LV2_FPWM | V <sub>OUT_LV2</sub> = 0.6V to 1.9V,<br>V <sub>IN_LV2</sub> = 3.6V,<br>I <sub>OUT_LV2</sub> = 0A to 1.5A,<br>FPWM | -1.5 |      | 1.5  | %    |

| Soft-Start Time                                                           | tss_Lv2           | Time for VOUT_LV2 to rise from 10% to 90% of target value, no load                                                | 600  | 1200 | 1800 | μS   |

| Switching<br>Frequency                                                    | fsw_LV2           |                                                                                                                   | 1.89 | 2.1  | 2.31 | MHz  |

| Spread Spectrum<br>Range                                                  | fssp              |                                                                                                                   |      | 12   |      | %    |

| Hide-Side<br>MOSFET On-<br>Resistance                                     | RON_UG_LV2        |                                                                                                                   |      | 56   |      | mΩ   |

| Low-Side<br>MOSFET On-<br>Resistance                                      | Ron_lg_lv2        |                                                                                                                   | -    | 34   |      | mΩ   |

| Minimum On-Time                                                           | tmin_on_lv2       |                                                                                                                   |      |      | 44   | ns   |

| Positive Inductor<br>Peak Current Limit                                   | ICL_PK_LV2        |                                                                                                                   | 2.1  | 2.5  | 2.9  | А    |

| Positive Inductor<br>Valley Current<br>Limit                              | ICL_VALLEY_LV2    |                                                                                                                   |      | 1.8  |      | A    |

| Negative Inductor<br>Peak Current Limit                                   | ICL_N_PK_LV2      | LVBuck2 in FPWM                                                                                                   | 0.7  | 1.7  | 2.9  | А    |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

| Parameter                                                                 | Symbol            | Test Conditions                                                                 | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------|------|------|------|------|

| Output Discharge<br>Resistor                                              | RDIS_LV2          |                                                                                 | 6    | 9    | 14   | Ω    |

| LVBuck2 Output<br>Undervoltage<br>Falling Threshold<br>Detection          | VUVP_LV2          |                                                                                 |      | 95   |      | %    |

| LVBuck2 Output<br>Undervoltage<br>Falling Threshold<br>Detection Accuracy | VUVP_ACC_LV2      |                                                                                 | -1.3 |      | 1.3  | %    |

| LVBuck2 Output<br>Overvoltage<br>Rising Threshold<br>Detection            | VOVP_LV2          |                                                                                 |      | 105  |      | %    |

| LVBuck2 Output Overvoltage Rising Threshold Detection Accuracy            | VOVP_ACC_LV2      |                                                                                 | -1.3 |      | 1.3  | %    |

| PVD23<br>Overvoltage Rising<br>Protection                                 | VOVP_PVD23        |                                                                                 | 5.35 | 5.8  | 6.25 | V    |

| PVD23<br>Overvoltage<br>Hysteresis                                        | VOVP_HYS_PVD23    |                                                                                 |      | 580  |      | mV   |

| CH3_LVBuck3                                                               |                   |                                                                                 |      |      |      |      |

| Input Voltage<br>Range                                                    | VIN_LV3           |                                                                                 | 2.7  |      | 5    | V    |

| Output Voltage<br>Range                                                   | Vout_Lv3          |                                                                                 | 0.6  | 1.8  | 1.9  | V    |

| Output Voltage<br>Accuracy                                                | VOUT_ACC_LV3_FPWM | Vout_Lv3 = 0.6V to 1.9V,<br>Vin_Lv3 = 3.6V,<br>Iout_Lv3 = 0A to 1.5A,<br>FPWM   | -1.5 |      | 1.5  | %    |

| Soft-Start Time                                                           | tss_LV3           | Time from V <sub>OUT_LV3</sub> to rise from 10% to 90% of target value, no load | 600  | 1200 | 1800 | μS   |

| Switching<br>Frequency                                                    | fsw_Lv3           |                                                                                 | 1.89 | 2.1  | 2.31 | MHz  |

| Spread-Spectrum<br>Range                                                  | fssp              |                                                                                 |      | 12   |      | %    |

| High-Side<br>MOSFET On-<br>Resistance                                     | RON_UG_LV3        |                                                                                 |      | 56   |      | mΩ   |

| Low-Side<br>MOSFET On-<br>Resistance                                      | RON_LG_LV3        |                                                                                 |      | 34   |      | mΩ   |

| Minimum On-Time                                                           | tmin_on_lv3       |                                                                                 |      |      | 44   | ns   |

| Positive Inductor<br>Peak Current Limit                                   | ICL_PK_LV3        |                                                                                 | 2.1  | 2.5  | 2.9  | А    |

| Parameter                                                                 | Symbol         | Test Conditions                                                                    | Min  | Тур | Max  | Unit |

|---------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------|------|-----|------|------|

| Positive Inductor<br>Valley Current<br>Limit                              | ICL_VALLEY_LV3 |                                                                                    |      | 1.8 |      | А    |

| Negative Inductor<br>Peak Current Limit                                   | ICL_N_PK_LV3   | LVBuck3 in FPWM                                                                    | 0.7  | 1.7 | 2.9  | А    |

| Output Discharge<br>Resistor                                              | RDIS_LV3       |                                                                                    | 6    | 9   | 14   | Ω    |

| LVBuck3 Output<br>Undervoltage<br>Falling Threshold<br>Detection          | VUVP_LV3       |                                                                                    |      | 95  |      | %    |

| LVBuck3 Output<br>Undervoltage<br>Falling Threshold<br>Detection Accuracy | VUVP_ACC_LV3   |                                                                                    | -1.3 |     | 1.3  | %    |

| LVBuck3 Output<br>Overvoltage Rising<br>Threshold<br>Detection            | VOVP_LV3       |                                                                                    |      | 105 |      | %    |

| LVBuck3 Output<br>Overvoltage Rising<br>Threshold<br>Detection Accuracy   | VOVP_ACC_LV3   |                                                                                    | -1.3 |     | 1.3  | %    |

| PVD23<br>Overvoltage Rising<br>Protection                                 | VOVP_PVD23     |                                                                                    | 5.35 | 5.8 | 6.25 | V    |

| PVD23<br>Overvoltage<br>Hysteresis                                        | VOVP_HYS_PVD23 |                                                                                    |      | 580 |      | mV   |

| CH4_LDO                                                                   |                |                                                                                    |      |     |      |      |

| Input Voltage<br>Range                                                    | VIN_LDO        |                                                                                    | 2.7  |     | 5    | V    |

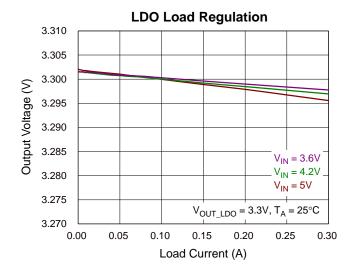

| Output Voltage<br>Range                                                   | Vout_ldo       |                                                                                    | 1.8  | 3.3 | 3.5  | V    |

| Output Voltage<br>Accuracy                                                | VOUT_ACC_LDO   | VOUT_LDO = 1.8V to 3.5V, (VIN_LDO - VOUT_LDO) $\geq$ 0.3V, IOUT_LDO = 0mA to 300mA | -1.5 |     | 1.5  | %    |

| Soft-Start Time                                                           | tss_LDO        | Time for V <sub>OUT_LDO</sub> to rise from 10% to 90% of target value, no load.    | 200  | 700 | 1100 | μs   |

| Dropout Voltage                                                           | VDROP_300_LDO  | IOUT_LDO = 300mA                                                                   |      |     | 300  | m\/  |

| ( <u>Note 7</u> )                                                         | VDROP_150_LDO  | IOUT_LDO = 150mA                                                                   |      |     | 150  | mV   |

| Maximum Output<br>Current                                                 | IOUT_MAX_LDO   |                                                                                    | 300  |     |      | mA   |

| Output Current<br>Limit                                                   | ICL_LDO        |                                                                                    | 345  | 450 | 555  | mA   |

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **RTQ2078-QF**

| Parameter                                                             | Symbol       | Test Conditions                                                                                                                      | Min  | Тур | Max | Unit |

|-----------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| Output Discharge<br>Resistor                                          | RDIS_LDO     |                                                                                                                                      | 48   | 76  | 104 | Ω    |

| LDO Output<br>Undervoltage<br>Falling Threshold<br>Detection          | Vuvp_ldo     |                                                                                                                                      |      | 95  |     | %    |

| LDO Output<br>Undervoltage<br>Falling Threshold<br>Detection Accuracy | VUVP_ACC_LDO |                                                                                                                                      | -1.3 |     | 1.3 | %    |

| LDO Output<br>Overvoltage Rising<br>Threshold<br>Detection            | VOVP_LDO     |                                                                                                                                      |      | 105 |     | %    |

| LDO Output Overvoltage Rising Threshold Detection Accuracy            | Vovp_acc_ldo |                                                                                                                                      | -1.3 |     | 1.3 | %    |

| I/O Control                                                           |              |                                                                                                                                      |      |     |     |      |

| PGOOD Low-Level<br>Output Voltage                                     | Vol_PGOOD    | Current into the PGOOD pin is equal to 5mA                                                                                           |      |     | 200 | mV   |

| PGOOD Input<br>Leakage Current                                        | ILEAK_PGOOD  | 1.8V is applied on the PGOOD pin                                                                                                     |      |     | 1   | μА   |

| PGOOD Delay<br>Time                                                   | tpgood_dly   | Time interval between the completion of the soft-start process for the last channel and the subsequent assertion of the PGOOD signal | 9    | 10  | 11  | ms   |

Note 6. PVCC is the pre-regulator output voltage only for internal circuitry. External loading on the PVCC pin is forbidden.

www.richtek.com

**Note 7**. Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100mV below its nominal value.

## 14.1 System Characteristics

The following specifications are guaranteed by design and are not performed in production testing. ( $T_A = T_J = -40^{\circ}\text{C}$  to 125°C,  $V_{IN} = 6\text{V}$ ,  $V_{OUT\_HV1} = 3.6\text{V}$ ,  $V_{OUT\_LV2} = 1.1\text{V}$ ,  $V_{OUT\_LV3} = 1.8\text{V}$ ,  $V_{OUT\_LDO} = 3.3\text{V}$ , unless otherwise specified.)

| Parameter                                        | Symbol              | Test Conditions                                                                                                                                                | Min  | Тур | Max | Unit |

|--------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| System                                           |                     | ,                                                                                                                                                              | •    | •   |     | •    |

| Quiescent<br>Current of VIN                      | IQ_ON               | EN = H, VuvLo_R ≤ VIN ≤ 24V, VouT_Hv1 ties to PVD23 and PVD45, all channels are ON, no load.                                                                   |      | 20  |     | mA   |

| Quiescent<br>Current of VIN                      | IQ_OFF              | EN = H, V <sub>UVLO_R</sub> ≤ V <sub>IN</sub> ≤ 24V, V <sub>OUT_HV1</sub> ties to PVD23 and PVD45, all channels are OFF.                                       |      | 3   |     | mA   |

| Over-<br>Temperature<br>Protection               | TTSD                |                                                                                                                                                                |      | 170 |     | °C   |

| Over-<br>Temperature<br>Protection<br>Hysteresis | TTSD_HYS            |                                                                                                                                                                |      | 20  |     | °C   |

| CH1_HVBuck1                                      |                     |                                                                                                                                                                |      |     |     |      |

| Maximum<br>Output Current                        | IOUT_MAX_HV1        | Depends on the input voltage and the output voltage                                                                                                            | 1.5  |     |     | А    |

| Load Transient                                   | VLOAD_TRAN_HV1_FPWM | V <sub>OUT</sub> <sub>HV1</sub> = 3.6V,<br>V <sub>IN</sub> <sub>HV1</sub> = 6V/9V/12V,<br>I <sub>OUT</sub> <sub>HV1</sub> = 10mA to 0.5A to<br>10mA, 1μs, FPWM | -150 |     | 150 | mV   |

| Line Transient                                   | VLINE_TRAN_HV1_FPWM | VOUT_HV1 = 3.6V,<br>VIN_HV1 = 5V to 18.5V to<br>5V, 100μs,<br>IOUT_HV1 = 0.5A, FPWM                                                                            | -50  |     | 50  | mV   |

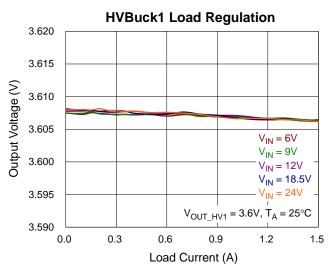

| Load Regulation                                  | VLOAD_REG_HV1       | V <sub>OUT</sub> <sub>_HV1</sub> = 3.6V,<br>V <sub>IN</sub> <sub>_HV1</sub> = 6V/9V/12V,<br>Δ <sub>IOUT</sub> <sub>_BK1</sub> = 1.5A, FPWM                     |      |     | 0.1 | %    |

| Line Regulation                                  | VLINE_REG_HV1       | VOUT_HV1 = 3.6V,<br>VIN_HV1 = 5V to 18.5V,<br>IOUT_HV1 = 1.5A                                                                                                  |      |     | 1   | %    |

| Output Ripple<br>Voltage                         | VRIPPLE_HV1_FPWM    | Peak to peak in one<br>switching cycle, FPWM,<br>SSP_EN bit = 0                                                                                                |      |     | 20  | mVpp |

| CH2_LVBuck2                                      |                     |                                                                                                                                                                |      |     |     |      |

| Maximum<br>Output Current                        | IOUT_MAX_LV2        |                                                                                                                                                                | 1.5  |     |     | А    |

| Load Transient                                   | VLOAD_TRAN_LV2_FPWM | VOUT_LV2 = 1.1V,<br>VIN_LV2 = 3.6V,<br>IOUT_LV2 = 100mA to 0.5A<br>to 100mA, 1µs, FPWM                                                                         | -50  |     | 50  | mV   |

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

13

| Parameter                 | Symbol              | Test Conditions                                                                                                            | Min | Тур | Max  | Unit |

|---------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Line Transient            | VLINE_TRAN_LV2_FPWM | VOUT_LV2 = 1.1V,<br>VIN_LV2 = 3V to 5V to 3V,<br>50μs, IOUT_LV2 =<br>10mA/0.75A/1.5A, FPWM                                 | -50 |     | 50   | mV   |

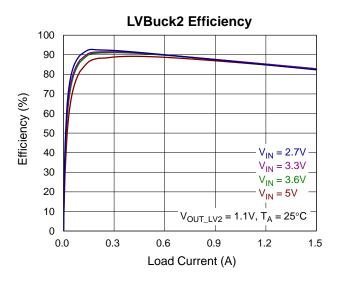

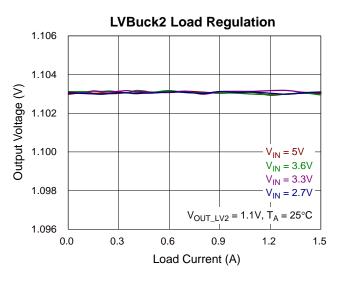

| Load Regulation           | VLOAD_REG_LV2       | V <sub>OUT_LV2</sub> = 1.1V,<br>V <sub>IN_LV2</sub> = 3.6V,<br>ΔI <sub>OUT_BK2</sub> = 1.5A, FPWM                          |     |     | 0.15 | %    |

| Line Regulation           | VLINE_REG_LV2       | VOUT_LV2 = 1.1V,<br>VIN_LV2 = 2.7V to 5V,<br>IOUT_LV2 = 1.5A                                                               |     |     | 1    | %    |

| Output Ripple<br>Voltage  | VRIPPLE_LV2_FPWM    | Peak to peak in one<br>switching cycle, FPWM,<br>SSP_EN bit = 0                                                            |     |     | 10   | mVpp |

| CH3_LVBuck3               |                     |                                                                                                                            |     |     |      |      |

| Maximum<br>Output Current | IOUT_MAX_LV3        |                                                                                                                            | 1.5 |     |      | А    |

| Load Transient            | VLOAD_TRAN_LV3_FPWM | V <sub>OUT_LV3</sub> = 1.8V,<br>V <sub>IN_LV3</sub> = 3.6V,<br>I <sub>OUT_LV3</sub> = 100mA to 0.5A<br>to 100mA, 1μs, FPWM | -50 |     | 50   | mV   |

| Line Transient            | VLINE_TRAN_LV3_FPWM | VOUT_LV3 = 1.8V,<br>VIN_LV3 = 3V to 5V to 3V,<br>50μs, IOUT_LV3 =<br>10mA/0.75A/1.5A, FPWM                                 | -50 |     | 50   | mV   |

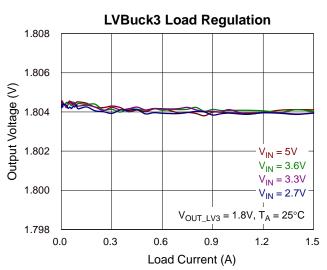

| Load Regulation           | VLOAD_REG_LV3       | VOUT_LV3 = 1.8V,<br>VIN_LV3 = 3.6V,<br>ΔIOUT_BK3 = 1.5A, FPWM                                                              |     |     | 0.15 | %    |

| Line Regulation           | VLINE_REG_LV3       | V <sub>OUT_LV3</sub> = 1.8V,<br>V <sub>IN_LV3</sub> = 2.7V to 5V,<br>I <sub>OUT_LV3</sub> = 1.5A                           |     |     | 1    | %    |

| Output Ripple<br>Voltage  | VRIPPLE_LV3_FPWM    | Peak to peak in one<br>switching cycle, FPWM,<br>SSP_EN bit = 0                                                            |     |     | 10   | mVpp |

| CH4_LDO                   |                     |                                                                                                                            |     |     |      |      |

| Power Supply              | Debb                | VOUT_LDO = 3.3V, VIN_LDO<br>≥ 3.6V, IOUT_LDO = 100mA,<br>f = 100kHz<br>Disturbing signal = 100mV                           |     | 60  |      | dB   |

| Rejection Ratio           | PSRR                | VOUT_LDO = 3.3V, VIN_LDO<br>≥ 3.6V, IOUT_LDO = 100mA,<br>f = 100kHz to 1MHz<br>Disturbing signal = 100mV                   |     | 40  |      | dB   |

| Load Transient            | VLOAD_TRAN_LDO      | VOUT_LDO = 3.3V, VIN_LDO<br>= 3.6V, IOUT_LDO = 10mA to<br>0.2A to 10mA, 1μs, CO_LDO<br>= 2.2μF                             | -25 |     | 25   | mV   |

| Line Transient            | VLINE_TRAN_LDO      | VOUT_LDO = 3.3V, VIN_LDO step 600mV, 10µs, the LDO is not in dropout condition, IOUT_LDO = 1mA/0.3A                        | -25 |     | 25   | mV   |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

| Parameter                                               | Symbol       | Test Conditions                                                                              | Min  | Тур | Max  | Unit |

|---------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------|------|-----|------|------|

| I <sup>2</sup> C                                        |              |                                                                                              | 1    |     | l    |      |

| SCL, SDA High-<br>Level Input<br>Threshold<br>Voltage   | VIH_I2C      |                                                                                              | 1.2  |     |      | V    |

| SCL, SDA Low-<br>Level Input<br>Threshold<br>Voltage    | VIL_I2C      |                                                                                              |      |     | 0.4  | V    |

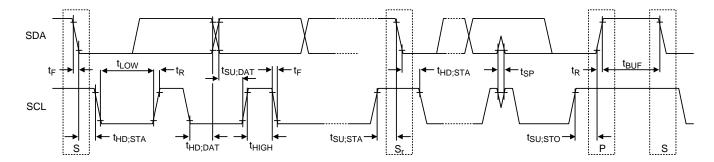

| SCL Clock<br>Frequency                                  | fscL         |                                                                                              |      |     | 1000 | kHz  |

| (Repeated) Start<br>Hold Time                           | thd;sta      | Hold time (repeated) start condition. After this period, the first clock pulse is generated. | 0.26 |     |      | μs   |

| SCL Clock Low<br>Time                                   | tLOW         |                                                                                              | 0.5  |     |      | μS   |

| SCL Clock High<br>Time                                  | thigh        |                                                                                              | 0.26 |     |      | μS   |

| (Repeated) Start<br>Setup Time                          | tsu;sta      | Set-up time for a repeated START condition                                                   | 0.26 |     |      | μs   |

| SDA Data Hold<br>Time                                   | thd;dat      |                                                                                              | 0    |     |      | ns   |

| SDA Set-up<br>Time                                      | tsu;dat      |                                                                                              | 50   |     |      | ns   |

| STOP Condition<br>Setup Time                            | tsu;sto      |                                                                                              | 0.26 |     |      | μs   |

| Bus Free Time<br>between Stop<br>and Start<br>Condition | tBUF         |                                                                                              | 0.5  |     |      | μs   |

| Rising Time of<br>Both SDA and<br>SCL Signals           | tR           |                                                                                              |      |     | 120  | ns   |

| Falling Time of<br>Both SDA and<br>SCL Signals          | tF           |                                                                                              |      |     | 120  | ns   |

| SDA Output Low<br>Sink Current                          | IOL_I2C      | SDA voltage = 0.4V                                                                           | 2    |     |      | mA   |

| Protection Time I                                       | Deglitch     |                                                                                              |      |     |      |      |

| HVBuck1 Output<br>UVP Deglitch<br>Time                  | tUVP_DEG_HV1 |                                                                                              |      | 50  |      | μS   |

| LVBuck2 Output<br>UVP Deglitch<br>Time                  | tuvp_deg_lv2 |                                                                                              |      | 50  |      | μs   |

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Parameter                              | Symbol            | Test Conditions | Min  | Тур | Max  | Unit |

|----------------------------------------|-------------------|-----------------|------|-----|------|------|

| LVBuck3 Output<br>UVP Deglitch<br>Time | tuvp_deg_lv3      |                 |      | 50  |      | μS   |

| LDO Output<br>UVP Deglitch<br>Time     | tuvp_deg_ldo      |                 |      | 50  |      | μs   |

| HVBuck1 Output<br>OVP Deglitch<br>Time | tOVP_DEG_HV1      |                 |      | 50  |      | μS   |

| LVBuck2 Output<br>OVP Deglitch<br>Time | tovp_deg_lv2      |                 |      | 50  |      | μS   |

| LVBuck3 Output<br>OVP Deglitch<br>Time | tovp_deg_lv3      |                 |      | 50  |      | μs   |

| LDO Output<br>OVP Deglitch<br>Time     | tovp_deg_ldo      |                 |      | 50  |      | μs   |

| PVD23 OVP<br>Rising Deglitch<br>Time   | tovp_r_deg_pvd23  | ΔV = 700mV      |      | 5   | 6    | μs   |

| PVD23 OVP<br>Falling Deglitch<br>Time  | tovp_F_DEG_PVD23  | ΔV = 700mV      |      | 5   | 6    | μS   |

| HVBuck1 OCP<br>Deglitch Time           | tOCP_DEG_HV1      |                 |      | 1   |      | ms   |

| LVBuck2 OCP<br>Deglitch Time           | tocp_deg_lv2      |                 |      | 1   |      | ms   |

| LVBuck3 OCP<br>Deglitch Time           | tOCP_DEG_LV3      |                 |      | 1   |      | ms   |

| LDO OCP<br>Deglitch Time               | tocp_deg_ldo      |                 |      | 1   |      | ms   |

| Component Cons                         | straint (Note 4)  |                 |      |     |      |      |

| Effective Output                       | LHV1              |                 | 1    | 1.5 | 2    |      |

| Effective Output Inductance            | L <sub>L</sub> V2 |                 | 0.68 | 1   | 1.2  | μΗ   |

|                                        | LLV3              |                 | 0.68 | 1   | 1.2  |      |

| Effective Boot Capacitance             | Своот             |                 | 0.07 | 0.1 | 0.13 | μF   |

| Effective PVCC Capacitance             | CPVCC             |                 | 0.3  | 1   | 1.4  | μF   |

|                                        | CIN_HV1           |                 | 1.5  | 4.7 | 10   |      |

| Effective Input Capacitance            | CIN_PVD23         |                 | 1.5  | 4.7 | 10   | μF   |

|                                        | CIN_VOUT1         | For LDO input   | 0.7  | 2.2 | 4    |      |

| Parameter                                                     | Symbol | Test Conditions | Min | Тур | Max | Unit |

|---------------------------------------------------------------|--------|-----------------|-----|-----|-----|------|

|                                                               | Co_HV1 |                 | 3.3 | 10  | 14  |      |

| Effective Output                                              | Co_LV2 |                 | 4.5 | 10  | 14  |      |

| Capacitance                                                   | Co_LV3 |                 | 4.5 | 10  | 14  | μF   |

|                                                               | Co_LDO |                 | 0.7 | 2.2 | 33  |      |

| Output Capacitance ESR for HVBuck1, LVBuck2, LVBuck3, and LDO | Co_esr |                 |     | 10  | 20  | mΩ   |

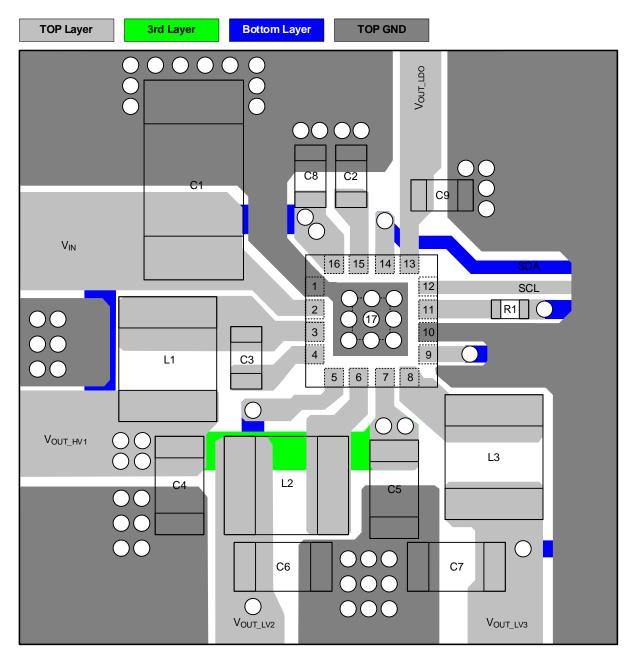

# 15 Typical Application Circuit

### 15.1 General CIS Application

**Table 1. Recommended Component List for Evaluation Board**

| Reference  | Qty | Part Number          | Description           | Package | Manufacturer |

|------------|-----|----------------------|-----------------------|---------|--------------|

| C1         | 1   | GCJ31CC71H475KA01    | 4.7μF/50V/X7S         | 1206    | MURATA       |

| C2         | 1   | GRT155C81A105KE01    | 1μF/10V/X6S           | 0402    | MURATA       |

| C3         | 1   | GRT155R71C104KE01    | 0.1μF/16V/X7R         | 0402    | MURATA       |

| C4, C6, C7 | 3   | GRT188C81A106ME13    | 10μF/10V/X6S          | 0603    | MURATA       |

| C5         | 1   | GRT188C81C475KE13    | 4.7μF/16V/X6S         | 0603    | MURATA       |

| C8, C9     | 2   | GRT155C81A225KE13    | 2.2μF/10V/X6S         | 0402    | MURATA       |

| L1         | 1   | TFM201610ALMA1R5MTAA | 1.5μH/3.1A/85mΩ       | 0806    | TDK          |

| L2, L3     | 2   | TFM201610ALMA1R0MTAA | 1μH/3.7A/50m $\Omega$ | 0806    | TDK          |

| R1         | 1   | MR02X1002FAL         | 10kΩ/1%               | 0201    | WALSIN       |

www.richtek.com

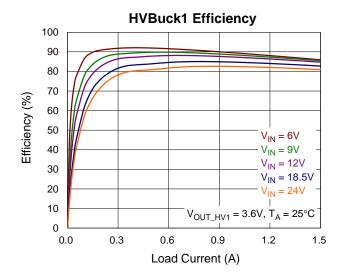

# 16 Typical Operating Characteristics

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

DSQ2078-QF-00

## 17 Operation

The RTQ2078-QF is a highly integrated power management integrated circuit (PMIC) for automotive camera system. It includes three step-down converters (HVBuck1, LVBuck2, and LVBuck3) and one generic LDO.

### 17.1 System Undervoltage and Overvoltage Protection

The RTQ2078-QF disables all channels if the VIN voltage falls below the Undervoltage Lock-Out level ( $VUVLO_F$ ) and the duration time is longer than  $32\mu s$ . The device initializes in its default state after the VIN voltage recovers from  $VUVLO_R$ .

When the VIN voltage reaches the overvoltage protection level (VovP\_R\_VIN), the step-down converters and LDO are disabled immediately. Then the IC enters the "Regulator Off" state, and PGOOD changes from "H" to "L" to indicate the IC is in a fault status. When VIN falls below 19.5V and the duration time is longer than  $5\mu$ s, then the RTQ2078-QF resumes operation automatically.

If the VIN voltage exceeds 20V, ensure the start-up rise slope is below  $80\text{mV}/\mu\text{s}$ . This cannot be controlled by the SEQ\_CTRL bit 0x00[0] for power on/off sequences to guarantee correct execution of the overvoltage protection function.

### 17.2 Over-Temperature Protection

The RTQ2078-QF features thermal shutdown (TSD) protection. When the junction temperature exceeds the typical threshold of 170°C, the TSD function is activated, resulting in the disabling all outputs as the device enters the "Regulator Off" state. Meanwhile, the PGOOD status also changes from "H" to "L" state to indicate the IC is in a fault status. The RTQ2078-QF will automatically resume normal operation once the junction temperature falls below the TSD threshold with a 20°C hysteresis band and VIN is below 19.5V.

### 17.3 Pre-Regulator

The device integrates a 4.58V linear regulator (PVCC) supplied by VIN to provide power to the internal circuitry. The PVCC is "NOT" allowed to power any other device or circuitry. A  $1\mu F$  decoupling capacitor must be connected between PVCC and PGND to filter noise, and it needs to be placed as close as possible to the PVCC pin.

### 17.4 Peak Current Mode Control

The three step-down converters utilize peak current mode control. At the beginning of each clock cycle, the internal high-side MOSFET turns on, allowing the current to ramp up in the inductor. By comparing the inductor peak current signal with the internal compensation signal derived from the feedback voltage, the turn-on time of high-side and low-side MOSFETs in every switching cycle are determined. In other words, the inductor current is used to control the duty-cycle and output voltage regulation of the converter.

### 17.5 Spread Spectrum Operation

Due to the periodicity of the switching signal, energy tends to concentrate at the fundamental frequency and its N-order harmonics. This concentration of energy can result in radiation that may cause the EMI issues. To address this, the RTQ2078-QF is equipped with a spread spectrum function designed to reduce EMI and ensure compliance with automotive EMC standards (CISPR 25). The spread spectrum function employs a pseudo-random sequence to modulate the switching frequency, allowing it to vary randomly within a range of 0% to 12%. For example, with a 2.1MHz typical switching frequency, the actual frequency will randomly oscillate between 2.1MHz and 2.352MHz. As a result, the RTQ2078-QF effectively prevents the switching frequency from interfering with the 1.8MHz AM band, which is a critical requirement of CISPR 25.

RICHTEK is a registered trademark of Richtek Technology Corporation.

### 17.6 Phase-Shift Operation

The RTQ2078-QF supports phase-shift operation to prevent all step-down converters from switching simultaneously, further reducing the radiation quantity of energy. The phase-shift difference in the clock between each step-down converter automatically changes based on the numbers of enabled channels. For example, when two step-down converters are in use, the initial turn-on time between two high-side MOSFETs has a 180-degree phase difference. Likewise, there is a 120-degree phase difference when three step-down converters are in use.

### 17.7 Channel Floating Allowable

To save PCB layout space and reduce material costs, the unused low-voltage step-down converters (CH2/CH3) can be left with floating pins, eliminating the need for inductors and output capacitors. The RTQ2078-QF automatically detects the pin status during the power-on procedure to determine whether the channel is used or not. After that, any malfunction in an unused channel will not impact the device operation.

### 17.8 Reboot Operation

The RTQ2078-QF features a reboot function applicable when VIN does not exceed 20V.

If the register bit 0x00[1] is set to 1, the device will disable all channels upon detecting a fault event. It will then exit the Fail-safe state and reboot, while preserve the record of the fault event. Conversely, if the register bit at 0x00[1] is set to 0, the IC remains in the Fail-safe state.

### 17.9 Power-Good and Error Indication

The RTQ2078-QF features an open-drain output pin named PGOOD (Power-Good) to indicate both the output voltage status of all channels and errors. Connect a pull-up resistor from the PGOOD pin to an external voltage. When the last channel in the power-on sequence reaches 90% of its target output voltage, the PGOOD signal will be pulled high to indicate a "Power-Good" status after a 10ms delay.

Table 2. Unused Channel Pin Considerations

Channel Unused Pin Number Unused Pin Name

| Unused Channel   | <b>Unused Pin Number</b> | Unused Pin Name | Pin Configuration                                  |

|------------------|--------------------------|-----------------|----------------------------------------------------|

|                  | 5                        | VOUT2           | Floating                                           |

| LVBuck2          | 6                        | SW2             | Floating                                           |

|                  | 7                        | PVD23           | Connect to a stable voltage                        |

|                  | 7                        | PVD23           | Connect to a stable voltage                        |

| LVBuck3          | 8                        | SW3             | Floating                                           |

|                  | 9                        | VOUT3           | Floating                                           |

| LDO              | 13                       | LDOOUT          | Floating with minimum effective output capacitance |

| PGOOD            | 11                       | PGOOD           | Floating                                           |

| I <sup>2</sup> C | 12                       | SCL             | Connect to ground                                  |

| 10               | 14                       | SDA             | Connect to ground                                  |

## 18 Application Information

(Note 8)

#### 18.1 **Device and Channel Enable Control**

When the supply voltage VIN reaches the power-on reset level 2.7V (typical), the device is enabled and ready to receive I<sup>2</sup>C commands for configuration. When VIN exceeds the UVLO rising voltage and the SEQ\_CTRL register at 0x00[0] = 1, the power-on sequence gets started. The channels are sequenced power-off if the SEQ\_CTRL register at 0x00[0] = 0. All channels shut down immediately without any sequence once VIN falls below UVLO falling voltage.

### **Device Register Configuration Control**

Write access to the registers or bits marked as "CFG\_LOCK (Configured Lock)" is restricted via the TM\_PASS\_CODE registers at 0x20 and 0x21. Before the configuration of the registers can be changed, the correct password must be written to enter Guest Mode to unlock the control registers. To exit Guest Mode and lock the control registers, thereby preventing unexpected operations, an incorrect password must be entered once changes are finalized.

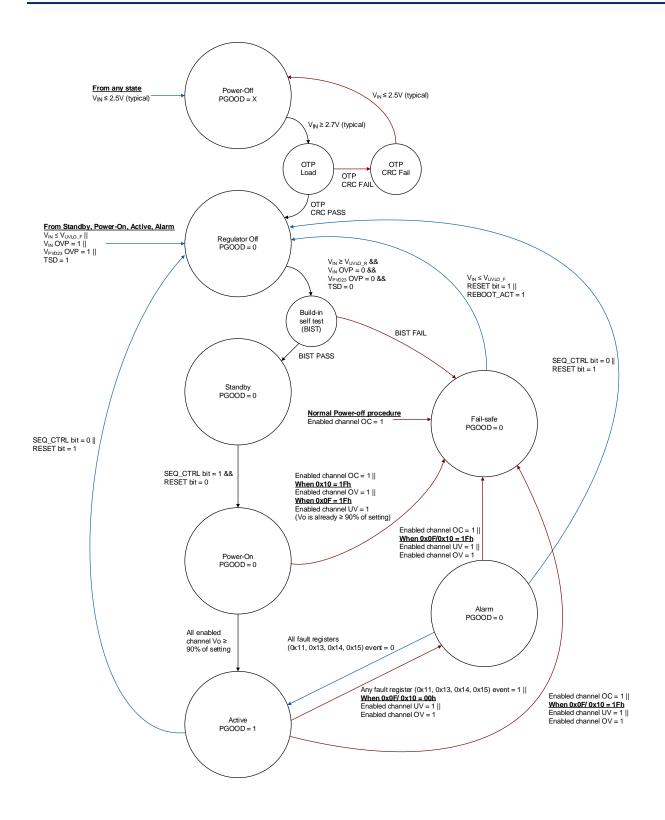

### **Device State Machine**

There are seven main states listed in the Table 3.

Table 3. Device State

| State         | Description                                                                                                                                                                | Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Exit                                                                                                                                       |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Power-Off     | The device is in non-operation state.                                                                                                                                      | V <sub>IN</sub> ≤ 2.5V (typical)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>IN</sub> ≥ 2.7V (typical)                                                                                                           |

| Regulator Off | The device loads OTP for the default setting and passes OTP CRC checksum value comparison. All channels are still disabled and the PGOOD signal are driven at a low state. | <ul> <li>From Power-Off</li> <li>Pass OTP CRC checksum value comparison</li> <li>From Standby/Power-On</li> <li>VIN ≤ VUVLO_F</li> <li>Fault event (VIN OVP, VPVD23 OVP, TSD)</li> <li>RESET behavior (RESET bit)</li> <li>From Active/Alarm</li> <li>VIN ≤ VUVLO_F</li> <li>Fault event (VIN OVP, VPVD23 OVP, TSD)</li> <li>RESET behavior (RESET bit)</li> <li>SEQ_CTRL_bit 0x00[0] = 0</li> <li>From Fail-Safe</li> <li>VIN ≤ VUVLO_F</li> <li>RESET behavior (RESET bit)</li> <li>RESET behavior (RESET bit)</li> <li>RESET behavior (RESET bit)</li> </ul> | To Power-Off  VIN ≤ 2.5V (typical)  To BIST  VIN ≥ VUVLO_R and no fault event (VIN OVP, VPVD23 OVP, TSD) and no RESET behavior (RESET bit) |

| State    | Description                                                                                                                                                         | Entry                                                                                                                                                | Exit                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standby  | The device passes built-in self-<br>test (BIST) and waits for an I <sup>2</sup> C<br>command to enable all<br>channels.                                             | BIST pass                                                                                                                                            | To Regulator Off  VIN ≤ VUVLO_F  Fault event (VIN OVP, VPVD23 OVP, TSD)  To Power-On  SEQ_CTRL 0x00[0] = 1 AND No RESET behavior (RESET bit)                                                                                                                                                                                                                                       |

| Power-On | Channel power-on procedure gets started.                                                                                                                            | From Standby  • SEQ_CTRL 0x00[0] = 1 AND  No RESET behavior (RESET bit)                                                                              | To Regulator Off  VIN ≤ VUVLO_F  Fault event (VIN OVP, VPVD23 OVP, TSD)  To Active  The output voltages of all enabled channels rise to 90% of target values  To Fail-Safe Fault event (CH Vo UVP, CH Vo OVP) if the register 0x0F = 1Fh, 0x10 = 1Fh Fault event (CH OCP)                                                                                                          |

| Active   | The output voltages of all enabled channels rise to 90% of target values. The PGOOD signal changes to high state to indicate the power status and any fault events. | From Power-On  All enabled channels output voltages rise to 90% of target values  From Alarm  All fault registers (0x11, 0x13, 0x14, 0x15) event = 0 | To Regulator Off  VIN ≤ VUVLO_F  Fault event (VIN OVP, VPVD23 OVP, TSD)  RESET behavior (RESET bit)  SEQ_CTRL 0x00[0] = 0  To Alarm  Fault event (CH Vo UVP, CH Vo OVP) if register 0x0F = 00h, 0x10 = 00h  Any fault register (0x11 to 0x15, except 0x12[6]) event = 1  To Fail-Safe  Fault event (CH Vo UVP, CH Vo OVP) if register 0x0F = 1Fh, 0x10 = 1Fh  Fault event (CH OCP) |

| State     | Description                                                                                                                                       | Entry                                                                                                                                       | Exit                                                                                                                                                                                                                                                                                                    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alarm     | When a fault event is detected but the channel is not turned off, the PGOOD signal changes to low state to indicate power status and fault event. | From Active • Fault event (CH Vo UVP, CH Vo OVP) if register 0x0F = 00h, 0x10 = 00h • Any fault register (0x11, 0x13, 0x14, 0x15) event = 1 | To Regulator Off  VIN ≤ VUVLO_F  Fault event (VIN OVP, VPVD23 OVP, TSD)  RESET behavior (RESET bit)  SEQ_CTRL 0x00[0] = 0  To Active  All fault registers (0x11, 0x13, 0x14, 0x15) event = 0  To Fail-Safe  Fault event (CH VO UVP, CH VO OVP) if register 0x0F = 1Fh, 0x10 = 1Fh  Fault event (CH OCP) |

| Fail-safe | the PGOOD signal changes to<br>a low state to indicate the                                                                                        | <ul> <li>BIST fail</li> <li>Fault event (CH Vo UVP, CH Vo OVP) if register 0x0F = 1Fh, 0x10 = 1Fh</li> <li>Fault event (CH OCP)</li> </ul>  | To Regulator Off  VIN ≤ VUVLO_F  RESET behavior (RESET bit)  REBOOT_ACT 0x00[1] = 1                                                                                                                                                                                                                     |

Figure 1. State Diagram

DSQ2078-QF-00

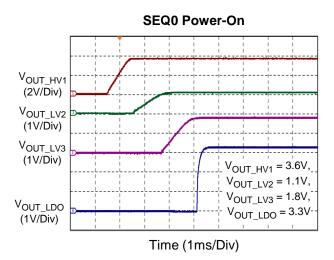

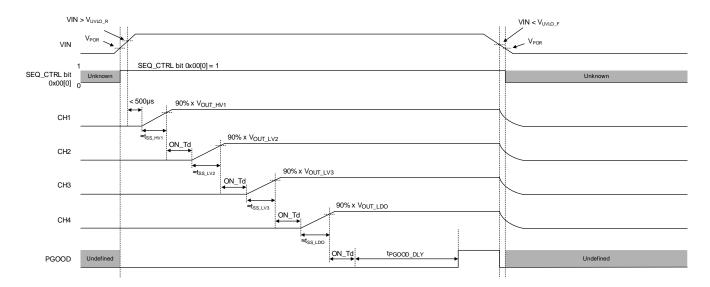

#### 18.4 **Power Sequence and Interval Time Setting**

The RTQ2078-QF supports four power-on sequences, as shown in Table 4. Only when the SEQ\_CTRL register at 0x00[0] = 0, the power sequence register at 0x02[2:0] and the interval time register at 0x02[6:3] between adjacent channels can be configured by I<sup>2</sup>C. The new settings will be applied at the next power-up. The RTQ2078-QF is also equipped with the OTP36 register at 0xE4[6:0] to provide OTP (One-Time Programmable) settings of power sequence and interval time to establish factory default settings.

| SEQ No. | Sequence |               |     |     |  |  |  |

|---------|----------|---------------|-----|-----|--|--|--|

| SEQ0    | CH1      | CH2           | CH3 | CH4 |  |  |  |

| SEQ1    | CH1      | CH4           | СНЗ | CH2 |  |  |  |

| SEQ2    | CH1      | CH3           | CH4 | CH2 |  |  |  |

| SEQ3    | CH1      | CH2, CH3, CH4 |     |     |  |  |  |

Table 4. Power-On Sequence

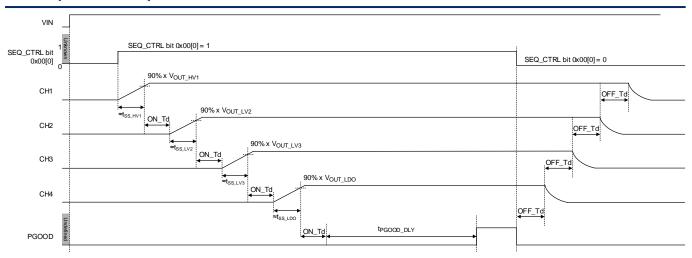

#### 18.5 **Power-On/Off Control**

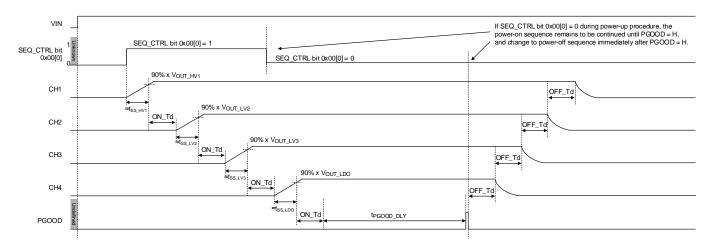

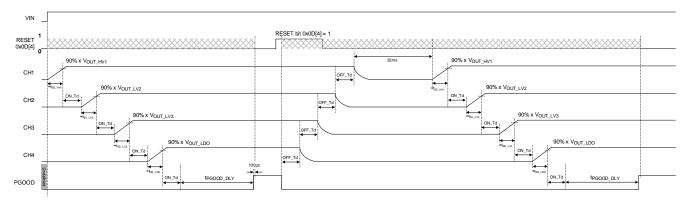

There are methods using VUVLO, the SEQ\_CTRL register bit at 0x00[0] or the RESET register bit at 0x0D[4] to flexibly control the RTQ2078-QF power sequence for different requirements and applications. The power-off sequence is the reverse order of the power-on sequence.

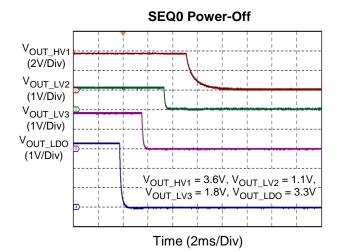

Figure 2. Example of SEQ0 Power Sequence Triggered by VuvLo

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Figure 3. Example 1 of SEQ0 Power Sequence Triggered by SEQ\_CTRL

Figure 4. Example 2 of SEQ0 Power Sequence Triggered by SEQ\_CTRL

Figure 5. Example of SEQ0 Power Sequence Triggered by the RESET bit

#### 18.6 **Output Voltage Setting**

The output voltage settings of all rails are controlled through I<sup>2</sup>C by configuring the relevant registers. The RTQ2078-QF also equipped with OTP37 to OTP38 registers, ranging from 0xE5 to 0xE6, to enable one-time programmable settings for corresponding output voltages, establishing them as the factory default settings.

#### HVBuck1, LVBuck2 and LVBuck3 18.6.1

HVBuck1 output voltage can be set via the register at 0x03[3:0] from 2.7V to 5V, and the default voltage is 3.6V. LVBuck2 output voltage can be set via the register at 0x04[4:0] from 0.6V to 1.9V, and the default voltage is 1.1V. LVBuck3 output voltage can be set via the register at 0x05[4:0] from 0.6V to 1.9V, and the default voltage is 1.8V.

#### 18.6.2 LDO

LDO output voltage can be set via the register at 0x06[4:0] from 1.8V to 3.5V. The default voltage is set at 3.3V.

#### 18.7 **Reset Function**

The RTQ2078-QF is equipped with a RESET register at 0x0D[4] to reset the device when VIN does not exceed 20V. The device activates the RESET function 100µs after the PGOOD signal asserts high.

The RESET\_ACT register bit at 0x0D[3] offers two configuration options:

- If register bit 0x0D[3] = 0, all registers, except for the sequence control related registers at 0x02[4:0] and fault event indication registers at 0x11, 0x13, 0x14, 0x15 are reset to their default values. The device follows the sequence settings to disable output rails. The fault event log remains stored in the corresponding registers and can be accessed by the ECU after the reset.

- If register bit 0x0D[3] = 1, all registers, except for the sequence control related register at 0x02[4:0] are reset to their default values. The device follows the sequence settings to disable output rails.

#### 18.8 **Protection Features**

The RTQ2078-QF is equipped with multiple protections to safeguard the device from damage caused by abnormal operations or fault conditions, including overload, short-circuit, soldering issues, and more.

#### 18.8.1 Channel Output Undervoltage Protection (UVP)

There are four configurable UVP thresholds via the registers at 0x08. The output UVP deglitch time is adjustable through the registers at 0x09[3:0]. When any of the bits at 0x0F[4:1] is configured to 1, the device disables all channels simultaneously and enters a Fail-safe State once an UV fault is detected on any channel. Conversely, if all bits at 0x0F[4:1] are configured to 0 when an UV fault is detected, the device does not disable any channels but enters an Alarm State instead. The registers at 0x13[4:1] indicate that an UV fault event occurred on the corresponding channel, independent of the setting at 0x0F[4:1]. The RTQ2078-QF also includes OTP35 at registers 0xE3[1], providing one-time programmable settings of the channel output UVP behavior to be set as the factory default. Based on various states, there are different methods to reset the device, as shown in Table 3.

#### 18.8.2 Channel Output Overvoltage Protection (OVP)

There are four configurable OVP thresholds via the registers at 0x0A. The output OVP deglitch time is adjustable through the registers at 0x0B[3:0]. When any of the bits at 0x10[4:1] is configured to 1, the device disables all channels simultaneously and enters a Fail-safe State once an OV fault is detected on any channel. Conversely, if all bits at 0x10[4:1] are configured to 0 when an OV fault is detected, the device does not disable any channels but enters an Alarm State instead. The registers at 0x14[4:1] indicate that the OV fault event occurred on the

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

corresponding channel, independent of the setting at 0x10[4:1]. The RTQ2078-QF also includes OTP35 at registers 0xE3[2], providing one-time programmable settings of the channel output OVP behavior to be set as the factory default. Based on various states, there are different methods to reset the device, as shown in Table 3.

### 18.8.3 Channel Overcurrent Protection (OCP)

This section describes overcurrent protection function of HVBuck1, LVBuck2, and LVBuck3 and LDO.

### 18.8.3.1 HVBuck1, LVBuck2, and LVBuck3

The step-down converter includes a cycle-by-cycle peak current-limit protection for the high-side MOSFET, safeguarding against abnormal increases in inductor current, including those beyond the inductor's saturation current rating. In the event of an overcurrent, the controller immediately turns off the high-side MOSFET and turns on the low-side MOSFET to keep the inductor current within the peak current limit. After the inductor current decreases to below the valley current limit, the high-side MOSFET resumes switching. If an overcurrent fault is continuously detected for a duration longer than the deglitch time, the device disables all channels simultaneously and enters a Fail-safe State. There are different methods to reset the device, as shown in Table 3.

### 18.8.3.2 LDO

When the load reaches the current-limit threshold, the output current is regulated to maintain the current limit level. If an overcurrent fault persists beyond the deglitch time, the device simultaneously disables all channels and enters a Fail-safe State. There are different methods to reset the device, as shown in <u>Table 3</u>.

### 18.8.4 Channel Input Overvoltage Protection (OVP)

If the input voltage of step-down converters (LVBUCK2 and LVBUCK3), and LDO reaches the overvoltage protection threshold, the device disables all channels simultaneously and enters a Regulator Off State. The device then automatically restarts and powers back on once the input voltage falls below the overvoltage threshold minus the hysteresis value.

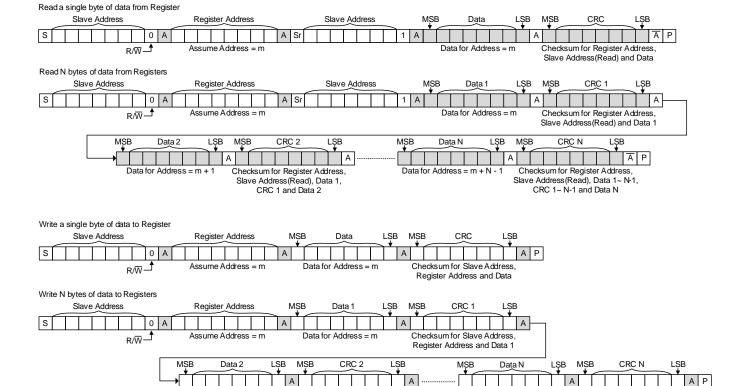

### 18.8.5 Built-In Self Test Protection