# RICHTEK®

# 5V Capable Low-Voltage DPDT Analog Switch

## **General Description**

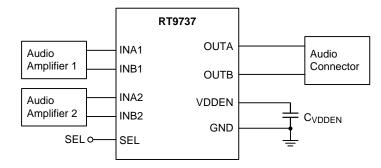

RT9737 is a 5V high quality low-voltage double-pole double-throw (DPDT) analog switch. RT9737 supply voltage is designed to operate from 2.5V to 5.5V. Supply voltage can be smaller than input voltage while keeping 5V input range. With  $70m\Omega$  turn-on resistance, power-loss and signal distortion can be minimized. RT9737 is ideal for switching audio signal from outputs of audio amplifiers. The break-before-make feature prevents signal distortion during the transferring of a signal from one path to another for audio applications.

# **Ordering Information**

RT9737

Package Type WSC : WL-CSP-9B 1.24x1.24 (BSC)

Note :

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes

# **Marking Information**

1P : Product Code

W : Date Code

# **Simplified Application Circuit**

Copyright © 2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

# Features

- Maximum Input Signal Range 0 to 5.5V

- $70m\Omega$  Turn-On Resistance

- 2.5V to 5.5V Supply Voltage

- 40µA Quiescent Current

- Break-Before-Make Between Channel Transition

- Available in 9Ball WL-CSP Package

# Applications

- Smartphone

- Tablet

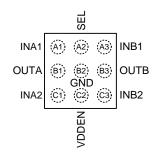

# Pin Configurations

(TOP VIEW)

WL-CSP-9B 1.24x1.24 (BSC)

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function               |

|---------|----------|----------------------------|

| A1      | INA1     | Input 1 of Channel A.      |

| A2      | SEL      | Selection for Input 1or 2. |

| A3      | INB1     | Input 1 of Channel B.      |

| B1      | OUTA     | Output of Channel A.       |

| B2      | GND      | Ground.                    |

| B3      | OUTB     | Output of Channel B.       |

| C1      | INA2     | Input 2 of Channel A.      |

| C2      | VDDEN    | Supply Voltage.            |

| C3      | INB2     | Input 2 of Channel B.      |

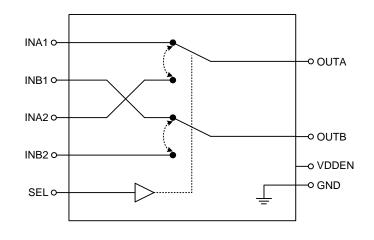

# **Function Block Diagram**

# Operation

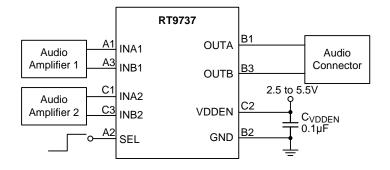

The switches are fully specified to operate from a single 2.5V to 5.5V power supply. RT9737 via internal design, be able to handle when the input signal is greater than the supply voltage range and don't cause the signal distortion. RT9737 control the switches with a control pin, SEL. When SEL voltage under low level, internal switch is thrown to position 1. Audio signal are

via INA1 and INB1 to IC OUTA and OUTB. And then OUTA, OUTB output to the load and Audio connector. When SEL voltage above high level, internal switch is thrown to position 2. When the supply voltage VDDEN under operation range, the switches impedance are risen and all analog signal ports can keep out signals from 0V to 5.5V.

# RICHTEK

# Absolute Maximum Ratings (Note 1)

| • VDDEN, INA1, INA2, INB1, INB2, OUTA, OUTB, SEL | –0.3 to 6V                       |

|--------------------------------------------------|----------------------------------|

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$   |                                  |

| WL-CSP-9B 1.24x1.24 (BSC)                        | 1.28W                            |

| Package Thermal Resistance (Note 2)              |                                  |

| WL-CSP-9B 1.24x1.24 (BSC), θ <sub>JA</sub>       | 78.1°C/W                         |

| Lead Temperature (Soldering, 10 sec.)            | 260°C                            |

| Junction Temperature                             | 150°C                            |

| Storage Temperature Range                        | $-65^{\circ}C$ to $150^{\circ}C$ |

| ESD Susceptibility (Note 3)                      |                                  |

| HBM (Human Body Model)                           | 2kV                              |

| MM (Machine Model)                               | 200V                             |

# Recommended Operating Conditions (Note 4)

| Supply Input Voltage, VDDEN | 2.5V to 5.5V                     |

|-----------------------------|----------------------------------|

| Junction Temperature Range  | $-40^{\circ}C$ to $125^{\circ}C$ |

| Ambient Temperature Range   | –40°C to 85°C                    |

# **Electrical Characteristics**

(V<sub>DDEN</sub> = 2.5V, C<sub>VDDEN</sub> =  $0.1\mu$ F, T<sub>A</sub>= 25°C, for each LDO unless otherwise specified)

| Parameter                    | Symbol                                                              | Test Conditions                                              | Min | Тур   | Max | Unit |  |

|------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------|-----|-------|-----|------|--|

| Power Supply                 |                                                                     |                                                              |     |       |     |      |  |

| Power Supply Range           | V <sub>DDEN</sub>                                                   |                                                              | 2.5 |       | 5.5 | V    |  |

| Power Supply Rejection Ratio | PSRR                                                                | Vp-p = 200mV, f = 20kHz, $R_L = 32\Omega$ (Note 5)           |     | 80    |     | dB   |  |

| Quiescent Current            | lq                                                                  | VDDEN = 2.5V to 5.5V                                         |     | 40    | 60  | μΑ   |  |

| Analog Switch                |                                                                     |                                                              |     |       |     |      |  |

| Input Signal Range           |                                                                     |                                                              | 0   |       | 5.5 | V    |  |

| Turn On Bogistones           | D                                                                   | VDDEN = 2.5V, OUT = 0V, I <sub>OUT</sub> =100mA              |     | 90    | 125 | mΩ   |  |

| Turn-On Resistance           | R <sub>DS(ON)</sub>                                                 | VDDEN = 3.6V, OUT = 0V, I <sub>OUT</sub> = 100mA             |     | 70    | 100 | mΩ   |  |

| Off State Leakage Current    |                                                                     | INA, INB, OUTA, OUTB, VDDEN = 5.5V                           |     | 1.2   | 1.5 | μΑ   |  |

| Off-State Leakage Current    |                                                                     | INA, INB, OUTA, OUTB = 5.5V, VDDEN = 0V                      |     | 0.12  | 0.2 | μΑ   |  |

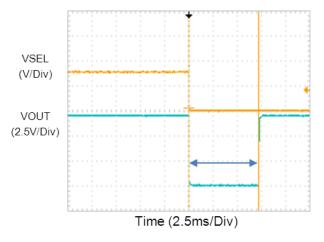

| Turn-On Time                 | t <sub>ON</sub>                                                     | INA, INB = 0V                                                |     | 5     | 10  | ms   |  |

| Turn-Off Time                | t <sub>OFF</sub>                                                    | INA, INB = 0V (Note 5)                                       |     |       | 100 | μS   |  |

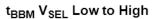

| Break-Before-Make Time       | t <sub>BBM</sub>                                                    | INA, INB = 0V                                                |     | 5     | 10  | ms   |  |

| Off-Isolation (Note 5)       |                                                                     | VDDEN = 0V, $R_L = 50\Omega$ , INA/INB = 0.5Vpp, 20kHz       |     | -50   |     | dB   |  |

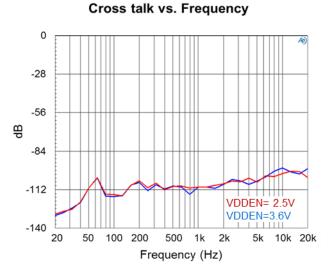

| Crosstalk (Note 5)           | talk (Note 5) $R_L = 50\Omega$ , INA/INB = 0.5Vpp, 20kHz            |                                                              | -   | -80   |     | dB   |  |

| THD+N (Note 5)               |                                                                     | $R_L$ = 50 $\Omega,~INA/INB$ = 0.5Vpp, 1kHz, DC bias = 0.25V |     | 0.001 |     | %    |  |

| -3dB Bandwidth (Note 5)      | Bandwidth (Note 5) $R_L = 50\Omega$                                 |                                                              |     | 2     |     | MHz  |  |

| INA/INB Capacitance          | VINB Capacitance INA /INB = 0.5V <sub>P-P</sub> , f = 1MHz (Note 5) |                                                              |     | 70    |     | pF   |  |

| OUTA/OUTB Capacitance        |                                                                     | $INA / INB = 0.5V_{P-P}$ , f = 1MHz (Note 5)                 |     | 120   |     | pF   |  |

# RICHTEK

| Parameter                 | Symbol | Test Conditions   | Min  | Тур | Max | Unit |

|---------------------------|--------|-------------------|------|-----|-----|------|

| Digital I/O               |        |                   |      |     |     |      |

| Input Logic-Hi Threshold  | VIH    |                   | 1.4  |     |     | V    |

| Input Logic-Low Threshold | VIL    |                   |      |     | 0.4 | V    |

| Input Leakage Current     |        | SEL = 0V or VDDEN | -0.1 |     | 0.1 | μΑ   |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

**Note 3.** Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guarantee by design.

# **Typical Application Circuit**

Copyright © 2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

WWW.richtek.com

DS9737-00 February 2014

# RICHTEK

Quiescent Current (uA)

36

28

20

# **Typical Operating Characteristics**

# Quiescent Current vs. VDDEN

2.5 3 3.5 4 4.5 5 VDDEN (V)

5.5

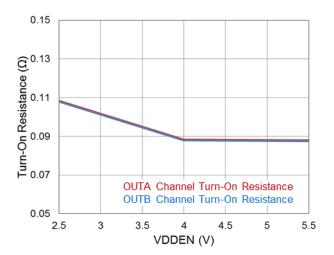

Turn-On Resistance vs. VDDEN

SEL Leakage Current vs. VSEL

5

# **RT9737**

# RICHTEK

# **Application Information**

RT9737 is a 5V high quality low-voltage double-pole double-throw (DPDT) analog switch. RT9737 supply voltage is designed to operate from 2.5 to 5.5V. Supply voltage can be smaller than input voltage while keeping 5V input range. With 70m $\Omega$  turn-on resistance, powerloss and signal distortion can be minimized. RT9737 is ideal for switching audio signal from outputs of audio amplifiers. The break-before-make feature prevents signal distortion during the transferring of a signal from one path to another for audio applications.

### **Analog Input**

RT9737 internal topology design for input and output voltage level can greater than supply voltage.

Low turn-on resistance and excellent channel to channel matching are ideal for audio applications.

### Switch Logic Control

RT9737 can use SEL pin to control internal switches position for another audio source application. SEL pin input current is very low.

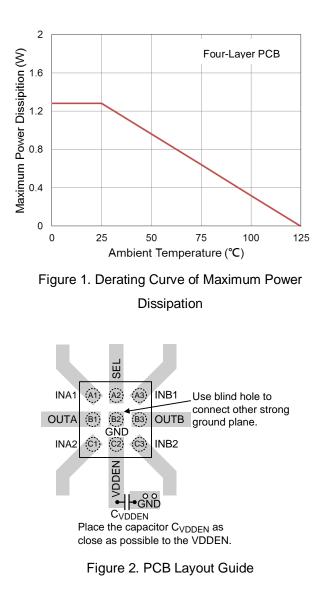

### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) \ / \ \theta_{\mathsf{JA}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is  $125^{\circ}$ C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WL-CSP-9B 1.24x1.24 (BSC) packages, the thermal resistance,  $\theta_{JA}$ , is 78.1°C/W on

a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula :

$\label{eq:PDMAX} \begin{array}{l} {\sf P}_{D(MAX)} \ = \ (125^{\circ}C \ - \ 25^{\circ}C) \ / \ (78.1^{\circ}C/W) \ = \ 1.28W \ for \\ {\sf WL-CSP-9B} \ 1.24x1.24 \ (BSC) \ package \end{array}$

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

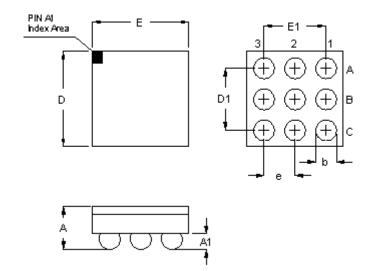

### **Outline Dimension**

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

|        | Min.       | Max.           | Min.                 | Max.  |  |

| A      | 0.500      | 0.600          | 0.020                | 0.024 |  |

| A1     | 0.170      | 0.230          | 0.007                | 0.009 |  |

| b      | 0.240      | 0.300          | 0.009                | 0.012 |  |

| D      | 1.190      | 1.290          | 0.047                | 0.051 |  |

| D1     | 0.800      |                | 0.0                  | )31   |  |

| E      | 1.190      | 1.290          | 0.047                | 0.051 |  |

| E1     | 0.800      |                | 0.0                  | )31   |  |

| е      | 0.4        | 100            | 0.0                  | 016   |  |

WL-CSP-9B 1.24x1.24 (BSC) Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation