Evaluation Boards

#### ign **کے** Sample & Is Buy

# RICHTEK

# RT9478M

### 24V Input for 2 to 4 Cell NVDC Buck-Boost Battery Charge Controller with PROCHOT, IBAT, and IBUS Pins, and SMBus

### 1 General Description

The RT9478M is a 4-switch bidirectional buck-boost Narrow Voltage DC (NVDC) charge controller, designed to charge 2- to 4-cell batteries from a wide range of DC power sources, including USB-C Power Delivery (PD) sources, conventional AC-DC charger adapters, and mobile batteries.

The device's SMBus serial communication interface allows for flexible programming of various parameters, including charging current, charging voltage, and protection thresholds for overvoltage and undervoltage conditions affecting the input, battery, and system outputs.

The recommended junction temperature range is  $-40^{\circ}$ C to  $125^{\circ}$ C, and the ambient temperature range is  $-40^{\circ}$ C to  $85^{\circ}$ C.

### 2 Applications

- Drones

- Portable Speakers

- Portable Devices and Accessories

### **3** Features

- Programmable Frequency: 720kHz/800kHz/1.2MHz

- Wide Input Voltage Range from 3.8V to 24V

- Average Input Current Regulation (AICR)

- Minimum Input Voltage Regulation (MIVR)

- Support 10m $\Omega$  and 5m $\Omega$  Sensing Resister

- High Accuracy for 2% Battery Charge Current and 0.5% Voltage Regulation

- Wide Battery Regulation Voltage Range from 5V to 19.2V

- Support USB On-The-Go (OTG)

- 5V NMOSFET Gate Driver

- 8-Bit A/D Converter for Monitor Functions

- Input, System and Battery Voltage

- Input and Battery Current

- System Power

- Independent Comparator Input Voltage

- Input (IBUS) and Battery (IBAT) Current

- Low Battery Quiescent Current

- Programmable System Overvoltage Protection

- Protection

- Input, System and Battery Overvoltage

- System Undervoltage Protection

- Input and Battery Overcurrent Protection

- Over-Temperature Protection

- SMBus Compliant Serial Communication

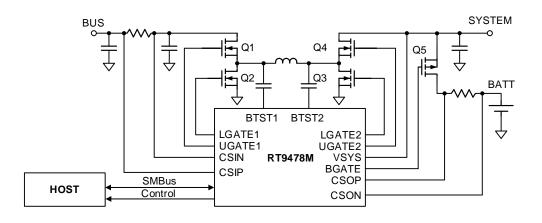

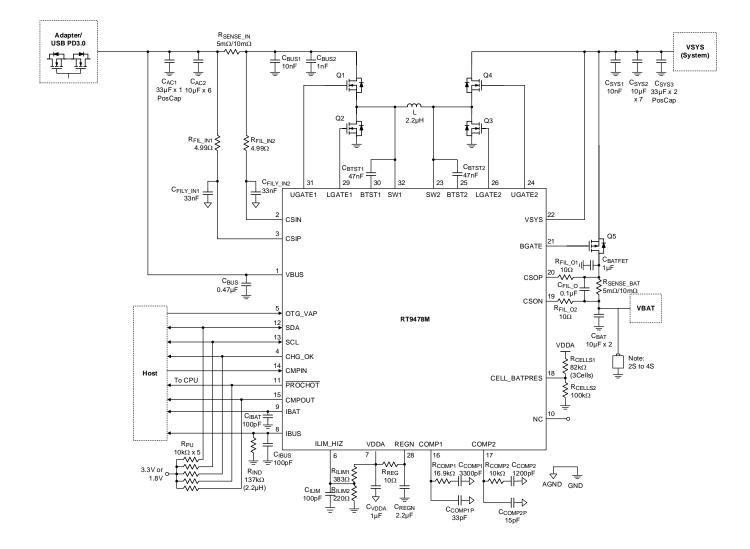

#### **Simplified Application Circuit** 4

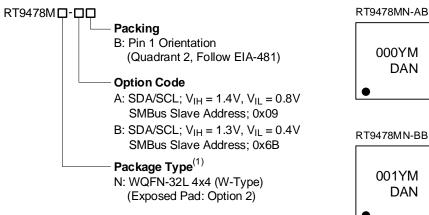

#### **Ordering Information** 5

#### Note 1.

Richtek products are Richtek Green Policy compliant and marked with (1) indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

#### **Marking Information** 6

001YM

DAN

000: Product Code YMDAN: Date Code

#### 001: Product Code YMDAN: Date Code

### **Table of Contents**

| 1  | Gene                                 | ral Description                                                                                | 1                          |

|----|--------------------------------------|------------------------------------------------------------------------------------------------|----------------------------|

| 2  | Appli                                | cations                                                                                        | 1                          |

| 3  | Featu                                | res                                                                                            | 1                          |

| 4  | Simpl                                | ified Application Circuit                                                                      | 2                          |

| 5  | Order                                | ing Information                                                                                | 2                          |

| 6  | Marki                                | ng Information                                                                                 | 2                          |

| 7  | Pin C                                | onfiguration                                                                                   | 4                          |

| 8  | Funct                                | ional Pin Description                                                                          | 4                          |

|    | 8.1                                  | IO Type Definition                                                                             | 5                          |

| 9  | Funct                                | ional Block Diagram                                                                            | 6                          |

| 10 |                                      | ute Maximum Ratings                                                                            |                            |

| 11 | Reco                                 | nmended Operating Conditions                                                                   | 8                          |

| 12 | Electi                               | ical Characteristics                                                                           | 8                          |

| 13 | Typic                                | al Application Circuit                                                                         |                            |

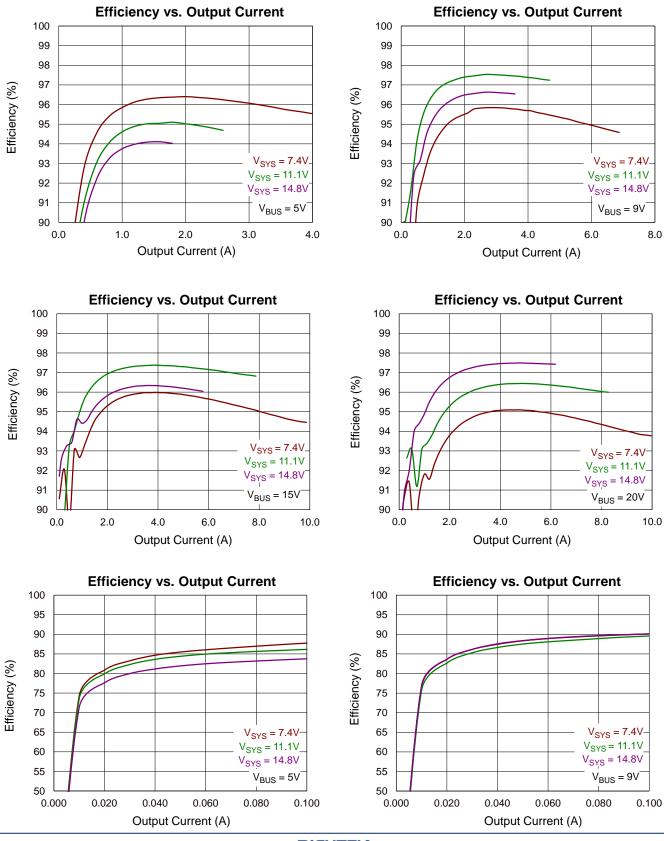

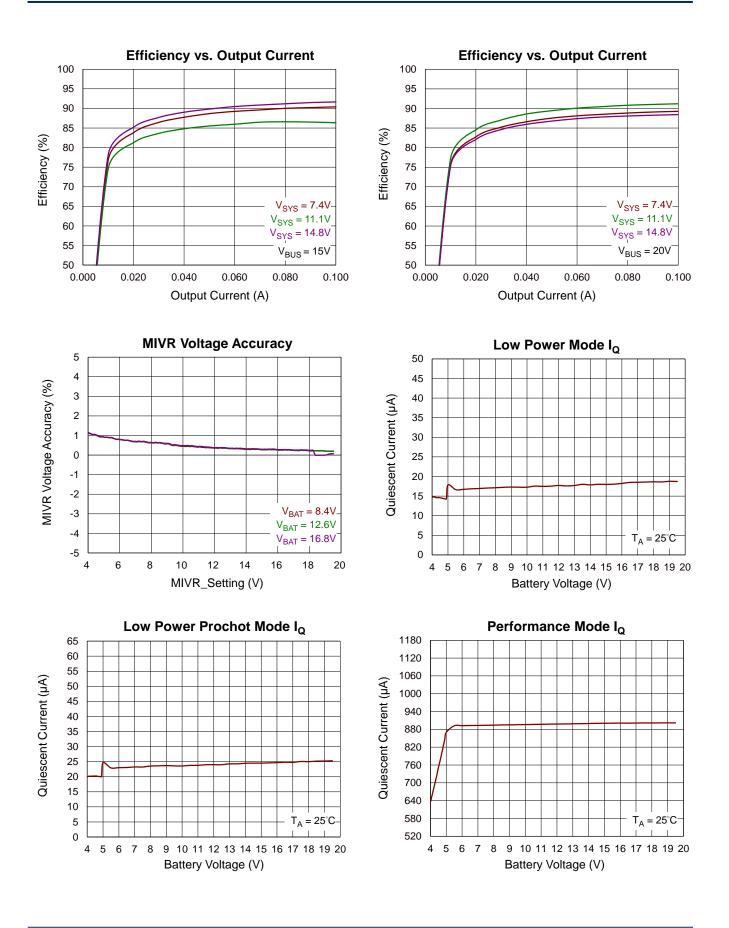

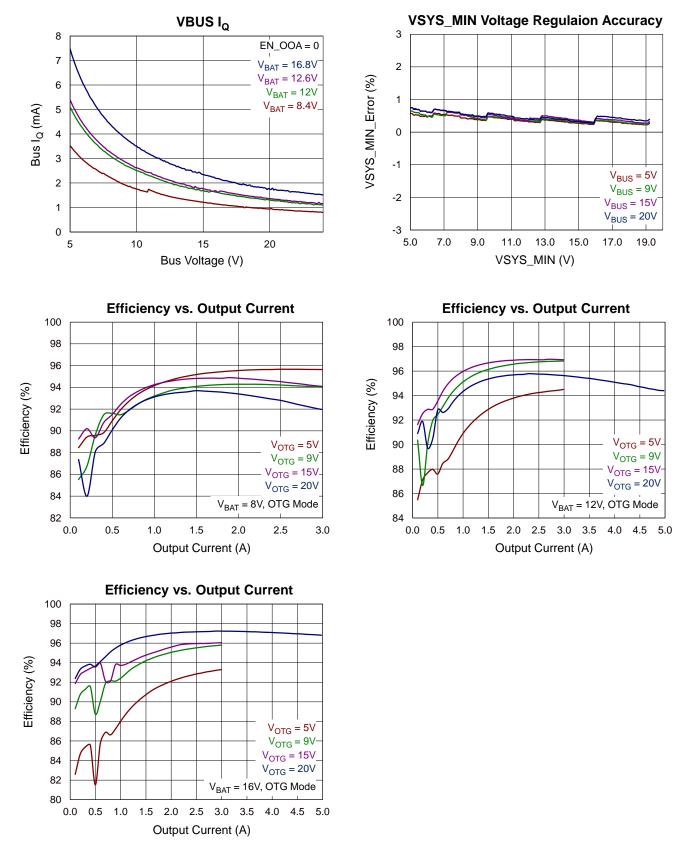

| 14 |                                      | al Operating Characteristics                                                                   |                            |

|    |                                      |                                                                                                |                            |

| 15 | Opera                                | ition                                                                                          |                            |

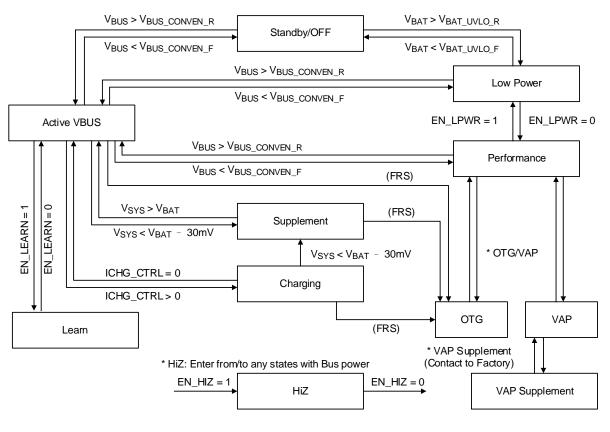

| 15 | <b>Opera</b><br>15.1                 | ition<br>Overview                                                                              |                            |

| 15 |                                      | Overview                                                                                       | 25                         |

| 15 | 15.1                                 |                                                                                                | 25<br>27                   |

| 15 | 15.1<br>15.2                         | Overview<br>Power-Up Sequence<br>Configuration                                                 | 25<br>27<br>28             |

| 15 | 15.1<br>15.2<br>15.3                 | Overview<br>Power-Up Sequence<br>Configuration<br>Charging Battery                             | 25<br>27<br>28<br>30       |

| 15 | 15.1<br>15.2<br>15.3<br>15.4         | Overview<br>Power-Up Sequence<br>Configuration                                                 | 25<br>27<br>28<br>30       |

| 15 | 15.1<br>15.2<br>15.3<br>15.4<br>15.5 | Overview<br>Power-Up Sequence<br>Configuration<br>Charging Battery<br>Dynamic Power Management | 25<br>27<br>28<br>30<br>32 |

|    | 15.8    | OTG Mode (USB On-The-Go)               |    |

|----|---------|----------------------------------------|----|

|    | 15.9    | Vmin Active Protection (VAP)           | 37 |

|    | 15.10   | HiZ Mode                               | 37 |

|    | 15.11   | Learn Mode                             | 37 |

|    | 15.12   | Force Converter Off Mode               | 37 |

|    | 15.13   | Processor Hot (PROCHOT)                | 38 |

|    | 15.14   | Protection                             |    |

|    | 15.15   | Other Features                         | 43 |

|    | 15.16   | SMBus Communication Interface          | 44 |

| 16 | Applic  | ation Information                      | 45 |

|    | 16.1    | Thermal Considerations                 | 45 |

|    | 16.2    | Register to be Reset by Input Power is |    |

|    |         | Unplugged                              | 46 |

|    | 16.3    | Register to be Reset by                |    |

|    |         | the CELL_BATPRES Pin Pulled Down       | 46 |

| 17 | Functi  | onal Register Description              | 47 |

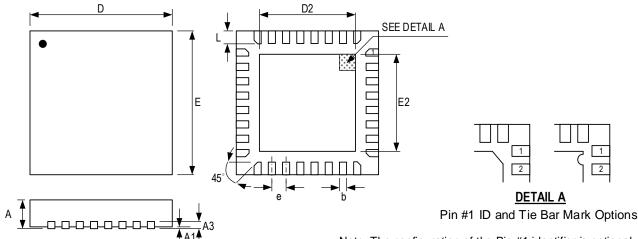

| 18 | Outline | e Dimension                            | 77 |

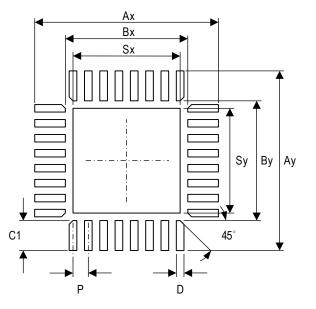

| 19 | Footpr  | int Information                        | 78 |

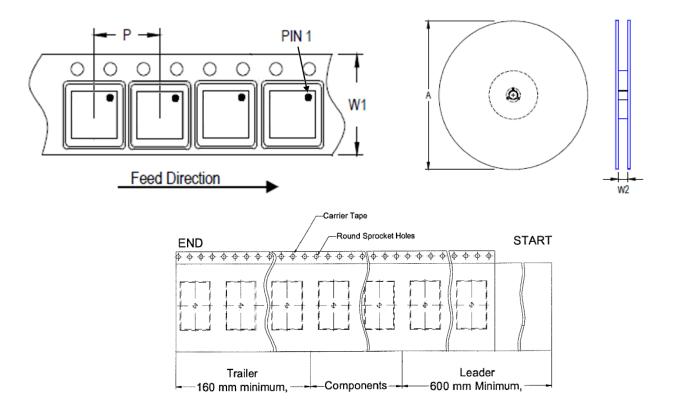

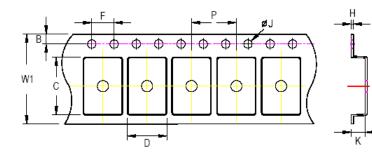

| 20 | Packin  | g Information                          | 79 |

|    | 20.1    | Tape and Reel Data                     | 79 |

|    | 20.2    | Tape and Reel Packing                  | 80 |

|    | 20.3    | Packing Material Anti-ESD Property     |    |

| 21 | Datash  | neet Revision History                  | 82 |

|    |         |                                        |    |

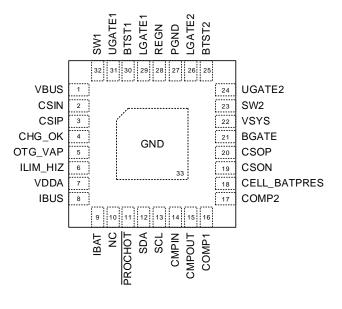

### 7 Pin Configuration

(TOP VIEW)

WQFN-32L 4x4

### 8 Functional Pin Description

| Pin No. | Pin Name | I/O | Pin Function                                                                                                    |

|---------|----------|-----|-----------------------------------------------------------------------------------------------------------------|

| 1       | VBUS     | PWR | Charger input voltage.                                                                                          |

| 2       | CSIN     | Ι   | Input current sense negative input.                                                                             |

| 3       | CSIP     | Ι   | Input current sense positive input.                                                                             |

| 4       | CHG_OK   | 0   | Open drain, active high indicator to inform the system for charging.                                            |

| 5       | OTG_VAP  | I   | Mode enables pin for OTG/VAP in reverse mode. If OTG and VAP are not used, this pin can be connected to GND.    |

| 6       | ILIM_HIZ | Ι   | Input current limit programming and HiZ mode enable input pin.                                                  |

| 7       | VDDA     | PWR | Internal power supply pin. Connect REGN through a filter.                                                       |

| 8       | IBUS     | 0   | Input current monitor analog output pin. This pin is also used to detect inductor value.                        |

| 9       | IBAT     | 0   | Battery current monitor analog output pin. This pin can be unconnected if battery current monitor is not used.  |

| 10      | NC       | 0   | This pin has to be disconnected                                                                                 |

| 11      | PROCHOT  | 0   | Processor hot indicator open drain output.                                                                      |

| 12      | SDA      | I/O | Open drain data signal input/output pin of the SMBus interface.                                                 |

| 13      | SCL      | I   | Clock signal input pin of the SMBus interface.                                                                  |

| 14      | CMPIN    | I   | Independent comparator input pin. This pin can be connected to GND if independent comparator is not used.       |

| 15      | CMPOUT   | 0   | Open drain output of independent comparator. This pin can be unconnected if independent comparator is not used. |

| 16      | COMP1    | Ι   | Buck-boost converter compensation pin 1.                                                                        |

| <b>RT9478M</b> |

|----------------|

|----------------|

| Pin No.                | Pin Name         | I/O | Pin Function                                                                                                                                                                      |

|------------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                     | COMP2            | I   | Buck-boost converter compensation pin 2.                                                                                                                                          |

| 18                     | CELL_BATPRE<br>S | I   | Battery cell selection pin for 2- to 4-cell battery setting. This pin should be biased from VDDA through a resister divider. This pin is also used for battery removal detection. |

| 19                     | CSON             | I   | Battery charge current sense negative input. Positive in case of battery discharge.                                                                                               |

| 20                     | CSOP             | I   | Battery charge current sense positive input. Negative in case of battery discharge.                                                                                               |

| 21                     | BGATE            | 0   | P-channel battery FET (BATFET) gate driver output. Connect to the gate of the battery P-MOSFET, Q5 in the simplified application circuit.                                         |

| 22                     | VSYS             | PWR | System sensing voltage input.                                                                                                                                                     |

| 23                     | SW2              | PWR | Boost mode switch node. Connect to the power inductor.                                                                                                                            |

| 24                     | UGATE2           | ο   | Boost mode high-side gate driver output. Connect to the gate of high-side N-MOSFET, Q4 in the simplified application circuit.                                                     |

| 25                     | BTST2            | PWR | Boost mode supply for high-side Q4 gate driver. Connect a 47nF bootstrap capacitor from this pin to the SW2 pin.                                                                  |

| 26                     | LGATE2           | ο   | Boost mode low-side gate driver output. Connect to the gate of low-<br>side N-MOSFET, Q3 in the simplified application circuit.                                                   |

| 27                     | PGND             | GND | Power Ground.                                                                                                                                                                     |

| 28                     | REGN             | PWR | $5V$ LDO output supplied from VBUS or VSYS. Connect a $2.2\mu F$ capacitor from this pin to GND. This output is internally used for gate drive only.                              |

| 29                     | LGATE1           | ο   | Buck mode low-side gate driver output. Connect to gate of low-side N-MOSFET, Q2 in the simplified application circuit.                                                            |

| 30                     | BTST1            | PWR | Buck mode supply for high-side Q1 gate driver. Connect a 47nF bootstrap capacitor from this pin to the SW1 pin.                                                                   |

| 31                     | UGATE1           | 0   | Buck mode high-side gate driver output. Connect to the gate of high-<br>side N-MOSFET, Q1 in the simplified application circuit.                                                  |

| 32                     | SW1              | PWR | Buck mode switch node. Connect to the power inductor.                                                                                                                             |

| 33<br>(Exposed<br>Pad) | GND              | GND | Ground. The exposed pad must be soldered to a large PCB pattern to achieve sufficient thermal performance.                                                                        |

### 8.1 IO Type Definition

- PWR: Power Pin

- GND: Ground Pin

- I: Input Pin

- O: Output Pin

- I/O: Input/Output Pin

RICHTEK

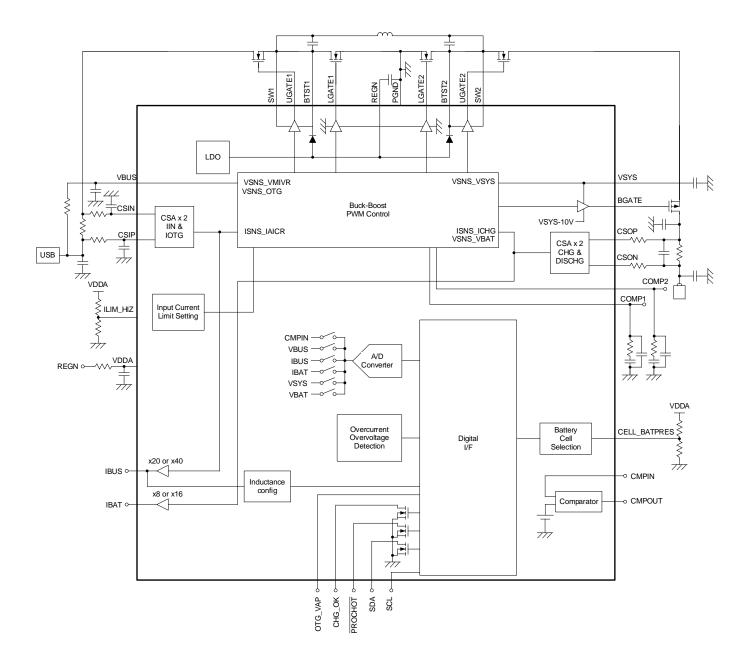

### 9 Functional Block Diagram

### **10 Absolute Maximum Ratings**

| (Note 2, Note 3)                                                     |                           |

|----------------------------------------------------------------------|---------------------------|

| • BTST1, BTST2, UGATE1, UGATE2                                       | –0.3V to 35V              |

| • BGATE                                                              | –0.3V to 30V              |

| • LGATE1, LGATE2                                                     | –0.3V to 6V               |

| • SW1, SW2                                                           | -2V (50ns), -0.3V (DC) to |

| 30V                                                                  |                           |

| CSIP, CSIN, CSOP, CSON                                               | –0.3V to 30V              |

| CSIP to CSIN, CSOP to CSON                                           | -0.5V to 0.5V             |

| VBUS, VSYS                                                           | –0.3V to 30V              |

| <ul> <li>CHG_OK, OTG_VAP, REGN, VDDA, ILIM_HIZ, SDA, SCL,</li> </ul> |                           |

| PROCHOT, CELL_BATPRES, CMPIN, CMPOUT, COMP1, COMP2                   | -0.3V to 6V               |

| • IBUS, IBAT                                                         | -0.3V to 3.6V             |

| BTST1 to SW1, BTST2 to SW2, UGATE1 to SW1, UGATE2 to SW2             | –0.3V to 6V               |

| VSYS to BGATE                                                        | 15V to -0.3V              |

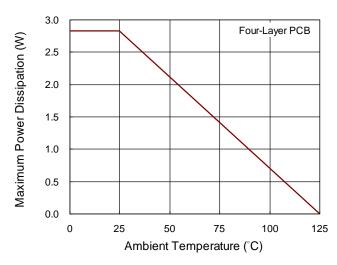

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul>                |                           |

| WQFN-32L 4x4                                                         | 2.82W                     |

| Package Thermal Resistance ( <u>Note 4</u> )                         |                           |

| WQFN-32L 4x4, θja                                                    | 35.43°C/W                 |

| WQFN-32L 4x4, θ <sub>JC</sub>                                        | 0.95°C/W                  |

| Lead Temperature (Soldering, 10 sec.)                                | 260°C                     |

| Junction Temperature                                                 | 150°C                     |

| Storage Temperature Range                                            | –65°C to 150°C            |

| ESD Susceptibility ( <u>Note 5</u> )                                 |                           |

| HBM (Human Body Model)                                               | 2kV                       |

| CDM (Charged Device Model)                                           | 500V                      |

- **Note 2**. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3. Absolute Maximum Ratings and ESD Susceptibility are guaranteed at  $T_J$  = 25°C.

- **Note 4**.  $\theta_{JA}$  is simulated under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is simulated at the bottom of the package

- Note 5. Devices are ESD sensitive. Handling precautions are recommended.

### **11 Recommended Operating Conditions**

### (<u>Note 6</u>)

| • VBUS                                              | 0V to 24V     |

|-----------------------------------------------------|---------------|

| CSON (Battery Voltage)                              | 0V to 19.2V   |

| • CHG_OK, OTG_VAP, SDA, SCL, PROCHOT, CMPIN, CMPOUT | 0V to 5.5V    |

| Ambient Temperature Range                           | 40°C to 85°C  |

| Junction Temperature Range                          | 40°C to 125°C |

Note 6. The device is not guaranteed to function outside its operating conditions.

### **12 Electrical Characteristics**

(V\_BUS\_UVLO\_R < V\_BUS < V\_BUS\_OVP\_F, -40°C < T\_J < 125°C, unless otherwise specified.)

| Parameter                                     | Symbol               | Test Conditions                           | Min           | Тур            | Мах            | Unit |

|-----------------------------------------------|----------------------|-------------------------------------------|---------------|----------------|----------------|------|

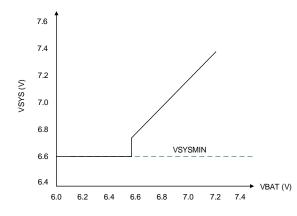

| VSYS Voltage Regulation                       | on                   | ·                                         |               |                |                |      |

| System Voltage                                |                      | VBAT_REG (0x15[14:3])<br>= 0x41A0 (16.8V) | Vcson<br>+ 30 | Vcson<br>+ 150 | Vcson<br>+ 480 | mV   |

| Regulation Accuracy<br>(Charge Disabled and   | Vsys_reg_acc         | VBAT_REG (0x15[14:3])<br>= 0x3138 (12.6V) | Vcson<br>+ 30 | Vcson<br>+ 150 | Vcson<br>+ 400 | mV   |

| OOA Disabled)                                 |                      | VBAT_REG (0x15[14:3])<br>= 0x20D0 (8.4V)  | Vcson<br>+ 30 | Vcson<br>+ 150 | Vcson<br>+ 400 | mV   |

| Minimum System<br>Voltage Regulation<br>Range | Vsys_min_reg_<br>rng |                                           | 5             |                | 19.2           | V    |

|                                               | Vsys_min_reg_<br>acc | VSYS_MIN (0x3E[15:8])                     |               | 12.3           |                | V    |

| Minimum System                                |                      | = 0x7B00                                  | -2            |                | 2              | %    |

| Voltage Regulation                            |                      | VSYS_MIN (0x3E[15:8])<br>= 0x5C00         |               | 9.2            |                | V    |

| Accuracy (VCSON below<br>Reg 0x3E setting,    |                      |                                           | -2            |                | 2              | %    |

| EN_OOA = 0b)                                  |                      | VSYS_MIN (0x3E[15:8])<br>= 0x4200         |               | 6.6            |                | V    |

|                                               |                      |                                           | -3            |                | 3              | %    |

| Battery Voltage Regula                        | tion                 | ·                                         |               |                |                |      |

| Battery Voltage<br>Regulation Range           | VBAT_REG_RNG         |                                           | 5             |                | 19.2           | V    |

|                                               |                      | VBAT_REG (0x15[14:3])                     |               | 16.8           |                | V    |

|                                               |                      | = $0x41A0$ , TJ = 0 to $85^{\circ}C$      | -0.5          |                | 0.5            | %    |

| Battery Voltage                               |                      | VBAT_REG (0x15[14:3])                     |               | 12.6           |                | V    |

| Regulation Accuracy<br>(Charge Enable)        | VBAT_REG_ACC         | =0x3138, TJ = 0 to 85°C                   | -0.5          |                | 0.5            | %    |

| , ,                                           |                      | VBAT_REG (0x15[14:3])                     |               | 8.4            |                | V    |

|                                               |                      | =0x20D0, T <sub>J</sub> = 0 to 85°C       | -0.6          |                | 0.6            | %    |

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

| Parameter                                                   | Symbol                 | Test Conditions                                        | Min | Тур   | Мах   | Unit |

|-------------------------------------------------------------|------------------------|--------------------------------------------------------|-----|-------|-------|------|

| Battery Current Regulat                                     | ion                    |                                                        | 1   |       | 1     |      |

| Battery Current<br>Regulation Differential<br>Voltage Range | Vchg_reg_rng           | Vcso = Vcsop – Vcson                                   | 0   |       | 81.28 | mV   |

|                                                             |                        | ICHG_CTRL (0x14[12:6])                                 |     | 4.096 |       | A    |

|                                                             |                        | = 0x1000, T <sub>J</sub> = 0 to 85°C                   | -3  |       | 2     | %    |

|                                                             |                        | ICHG_CTRL (0x14[12:6])                                 |     | 2.048 |       | А    |

| Charge Battery Current<br>Regulation Accuracy               | ICHG_REG_ACC           | = $0x0800$ , T <sub>J</sub> = 0 to $85^{\circ}C$       | -4  |       | 3     | %    |

|                                                             |                        | ICHG CTRL (0x14[12:6])                                 |     | 1.024 |       | А    |

|                                                             |                        | = $0x0\overline{4}00$ , T <sub>J</sub> = $25^{\circ}C$ | -5  |       | 6     | %    |

|                                                             |                        | ICHG_CTRL (0x14[12:6])<br>= 0x0400, TJ = 0 to 85°C     |     | 1.024 |       | А    |

|                                                             |                        |                                                        | -10 |       | 7     | %    |

|                                                             |                        | ICHG_CTRL (0x14[12:6])<br>= 0x0200, TJ = 25°C          |     | 0.512 |       | А    |

|                                                             |                        |                                                        | -12 |       | 12    | %    |

|                                                             |                        | ICHG_CTRL (0x14[12:6])                                 |     | 0.512 |       | А    |

|                                                             |                        | = 0x0200, T <sub>J</sub> = 0 to 85°C                   | -18 |       | 13    | %    |

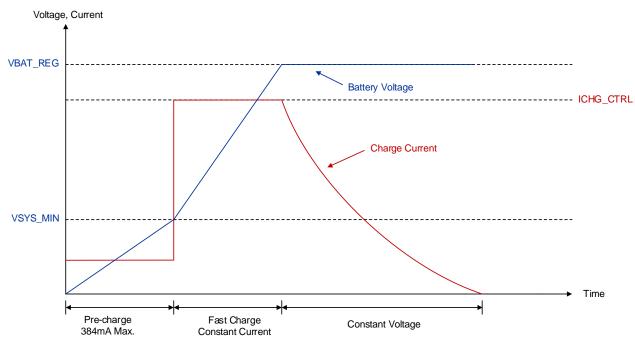

| Pre-Charge Battery<br>Current Limit                         | ILIM_PRECHG            | V <sub>CSON</sub> < VSYS_MIN<br>(0x3E[15:8])           |     | 384   |       | mA   |

|                                                             |                        | ICHG_CTRL (0x14[12:6])                                 |     | 384   |       | mA   |

|                                                             |                        | = 0x0180, TJ = 0 to 85°C                               | -15 |       | 15    | %    |

| Pre-Charge Battery                                          |                        | ICHG_CTRL (0x14[12:6])                                 |     | 256   |       | mA   |

| Current Regulation                                          | IPRECHG_REG_ACC        | = 0x0100, TJ = 0 to 85°C                               | -20 |       | 20    | %    |

| Accuracy with RSENSE_IN = $10m\Omega$                       |                        | ICHG_CTRL (0x14[12:6])                                 |     | 192   |       | mA   |

| 1011122                                                     |                        | = 0x00C0, TJ = 0 to 85°C                               | -25 |       | 25    | %    |

|                                                             |                        | ICHG_CTRL (0x14[12:6])                                 |     | 128   |       | mA   |

|                                                             |                        | = 0x0080, TJ = 0 to 85°C                               | -30 |       | 30    | %    |

| CSOP, CSON Leakage<br>Current Mismatch                      | ILK_DIFF_CSOP_<br>CSON |                                                        | -45 |       | -9.5  | μA   |

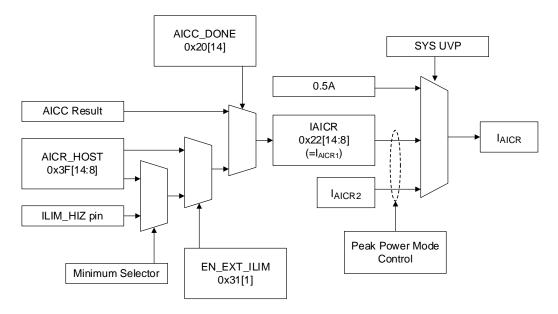

| Average Input Current R                                     | egulation (AICR)       |                                                        |     |       |       |      |

| AICR Differential Voltage<br>Range with RSENSE_IN =<br>10mΩ | VIAICR_REG_RNG         | Differential voltage:<br>Vcsip – Vcsin                 | 0.5 |       | 64    | mV   |

#### Copyright © 2025 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                                                      | Symbol                 | Test Conditions                                       | Min   | Тур    | Max   | Unit |

|----------------------------------------------------------------|------------------------|-------------------------------------------------------|-------|--------|-------|------|

|                                                                |                        | AICR_HOST (0x3F[14:8])<br>= 0x4E00, TJ = -40 to 105°C | 3800  | 3900   | 4000  | mA   |

| AICR Accuracy with 10mΩ CSIP/CSIN Series                       |                        | AICR_HOST (0x3F[14:8])<br>= 0x3A00, TJ = -40 to 105°C | 2800  | 2900   | 3000  | mA   |

| Resistor                                                       |                        | AICR_HOST (0x3F[14:8])<br>= 0x1C00, TJ = -40 to 105°C | 1300  | 1400   | 1500  | mA   |

|                                                                |                        | AICR_HOST (0x3F[14:8])<br>= 0x0800, TJ = -40 to 105°C | 300   | 400    | 500   | mA   |

| CSIP, CSIN Leakage<br>Current Mismatch                         | ILK_DIFF_CSIP_CSIN     | VCSIP = VCSIN = 11V                                   | -37.5 |        | -13   | μA   |

| Setting Voltage Range<br>for AICR (ILIM_HIZ Pin)               | Vaicr_rng_ilim_hi<br>z |                                                       | 0.958 |        | 3.333 | V    |

|                                                                |                        | VILIM_HIZ = 2.166V<br>TJ = -40 to 105°C               | 3800  | 4000   | 4200  | mA   |

| AICR Setting Voltage                                           | IAICR_REG_ACC_         | VILIM_HIZ = 1.833V<br>TJ = -40 to 105°C               | 2800  | 3000   | 3200  | mA   |

| Accuracy on the<br>ILIM_HIZ pin                                | ILIM_HIZ               | VILIM_HIZ = 1.333V<br>TJ = -40 to 105°C               | 1300  | 1500   | 1700  | mA   |

|                                                                |                        | VILIM_HIZ = 1.0 V<br>TJ = -40 to 105°C                | 300   | 500    | 700   | mA   |

| ILIM_HIZ Pin Leakage<br>Current                                | Ilk_ilim_hiz           | VILIM_HIZ = 5V                                        | -1    |        | 1     | μΑ   |

| Minimum Input Voltage I                                        | Regulation (MIVR)      |                                                       |       |        |       |      |

| MIVR Range                                                     | Vmivr_reg_rng          |                                                       | 3.2   |        | 19.52 | V    |

|                                                                |                        | VMIVR (0x3D[13:6])                                    |       | 18.688 |       | V    |

|                                                                |                        | = 0x3C80                                              | -2    |        | 2     | %    |

| MIVR Accuracy                                                  |                        | VMIVR (0x3D[13:6])<br>= 0x7B00                        |       | 10.88  |       | V    |

| INITY R ACCULACY                                               | Vmivr_reg_acc          |                                                       | -2.5  |        | 2.5   | %    |

|                                                                |                        | VMIVR (0x3D[13:6])<br>= 0x0500                        |       | 4.48   |       | V    |

|                                                                |                        |                                                       | -5    |        | 5     | %    |

| OTG Current Regulation                                         | I                      |                                                       |       |        |       |      |

| OTG Output Current<br>Regulation Differential<br>Voltage Range | VIOTG_REG_RNG          |                                                       | 0     |        | 63.5  | mV   |

|                                                                |                        | OTG_CUR (0x3C[14:8])<br>= 0x3C00                      | 2.8   | 3      | 3.2   | А    |

| OTG Output Current<br>Regulation Accuracy                      | IOTG_ACC               | OTG_CUR (0x3C[14:8])<br>= 0x1E00                      | 1.3   | 1.5    | 1.7   |      |

|                                                                |                        | OTG_CUR (0x3C[14:8])<br>= 0x0A00                      | 0.3   | 0.5    | 0.7   |      |

| OTG Voltage Regulation                                         |                        |                                                       | •     |        |       |      |

| OTG Voltage Regulation<br>Range (OOA Disabled)                 | Votg_reg_rng           |                                                       | 3     |        | 24    | V    |

| Parameter                                              | Symbol        | Test Conditions                                                                                                                                      | Min  | Тур | Max  | Unit |

|--------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

|                                                        |               | OTG_VOL (0x3B[13:2])                                                                                                                                 |      | 20  |      | V    |

|                                                        |               | = 0x2710                                                                                                                                             | -2   |     | 2    | %    |

| OTG Voltage Regulation                                 |               | OTG_VOL (0x3B[13:2])                                                                                                                                 |      | 12  |      | V    |

| Accuracy (OOA<br>Disabled)                             | Votg_reg_acc  | = 0x1770                                                                                                                                             | -2   |     | 2    | %    |

|                                                        |               | OTG_VOL (0x3B[13:2])                                                                                                                                 |      | 5   |      | V    |

|                                                        |               | = 0x09C4                                                                                                                                             | -3   |     | 3    | %    |

| REGN Regulator                                         |               |                                                                                                                                                      |      |     |      |      |

| REGN Regulator Voltage                                 | VREGN_REG     | VBUS = 10V                                                                                                                                           | 4.75 | 5   | 5.25 | V    |

| REGN Voltage in Drop<br>Out Mode                       | VREGN_DROP    | VBUS = 5V, IREGN = 20mA                                                                                                                              |      | 100 | 200  | mV   |

| REGN Current Limit<br>when Converter is<br>Enabled     | ILIM_REGN     | VBUS = 10V                                                                                                                                           | 65   | 78  |      | mA   |

| REGN Undervoltage                                      | VREGN_UVLO_F  |                                                                                                                                                      | 3    | 3.1 | 3.2  | V    |

| Quiescent Current                                      |               |                                                                                                                                                      |      |     | ·    |      |

|                                                        |               | Low power mode<br>V <sub>BAT</sub> = 18V,<br>EN_LPWR (0x12[15])<br>= 1 (Low power mode),<br>EN_PROCHOT_LPWR<br>= 0 (PROCHOT disabled)                |      | 18  | 45   |      |

| Device Powered by<br>Battery. BATFET On                | IQ_BATFET_ON  | Low power mode with<br>PROCHOT<br>V <sub>BAT</sub> = 18V,<br>EN_LPWR (0x12[15])<br>= 1 (Low power mode),<br>EN_PROCHOT_LPWR<br>= 1 (PROCHOT enabled) |      | 24  | 60   | μΑ   |

|                                                        |               | Performance mode<br>V <sub>BAT</sub> = 18V,<br>EN_LPWR (0x12[15])<br>= 0 (Performance mode)                                                          |      | 850 | 1170 |      |

|                                                        | IQ_STBY_BUCK  | VBUS = 20V, VBAT = 12.6V,<br>Qg = 7.5nC, no load,<br>EN_OOA (0x12[10])<br>= 0 (OOA disabled)                                                         |      | 1.4 |      |      |

| Device Powered VBUS<br>BATFET Off<br>( <u>Note 7</u> ) | IQ_STBY_BOOST | V <sub>BUS</sub> = 5V, V <sub>BAT</sub> = 8.4V,<br>Qg = 7.5nC, no load,<br>EN_OOA (0x12[10])<br>= 0 (OOA disabled)                                   |      | 3.6 |      | mA   |

|                                                        | IQ_STBY_BB    | V <sub>BUS</sub> = 12V, V <sub>BAT</sub> = 12V,<br>Qg = 7.5nC, no load,<br>EN_OOA (0x12[10])<br>= 0 (OOA disabled)                                   |      | 2.1 |      |      |

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

11

www.richtek.com

| Parameter                                                   | Symbol             | Test Conditions                                                                                                                      | Min | Тур | Max  | Unit |

|-------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Device Powered by<br>Battery, OTG Mode<br>( <u>Note 7</u> ) |                    | V <sub>BAT</sub> = 8.4V, VOTG_REG<br>(0x3B[13:2]) = 0x09C4 (5V),<br>Qg = 7.5nC, no load,<br>EN_OOA (0x12[10])<br>= 0 (OOA disabled)  |     | 1.8 |      |      |

|                                                             | IQ_STBY_OTG        | V <sub>BAT</sub> = 8.4V, VOTG_REG<br>(0x3B[13:2]) = 0x1770 (12V),<br>Qg = 7.5nC, no load,<br>EN_OOA (0x12[10])<br>= 0 (OOA disabled) |     | 3.0 |      | mA   |

|                                                             |                    | V <sub>BAT</sub> = 8.4V, VOTG_REG<br>(0x3B[13:2]) = 0x2710 (20V),<br>Qg = 7.5nC, no load,<br>EN_OOA (0x12[10])<br>= 0 (OOA disabled) |     | 5.3 |      |      |

| Input Current and Batte                                     | ry Current Monitor |                                                                                                                                      |     |     |      |      |

| Input Common Mode<br>Range                                  | VCSIP_CSIN_RNG     |                                                                                                                                      | 3.8 |     | 24   | V    |

| IBUS Output Clamp<br>Voltage                                | VIBUS_CLAMP        |                                                                                                                                      | 3.1 | 3.2 | 3.3  | V    |

| IBUS Output Current                                         | libus              |                                                                                                                                      |     |     | 1    | mA   |

| Input Current Sensing                                       | Aibus              | IBUS_GAIN (0x12[4]) = 0                                                                                                              |     | 20  |      |      |

| Gain                                                        | AIBUS              | IBUS_GAIN (0x12[4]) = 1                                                                                                              | -   | 40  | V/V  |      |

|                                                             | VIBUS_ACC          | V(CSIP – CSIN) = 40.96mV                                                                                                             | -4  |     | 2    | - %  |

| Input Current Monitor                                       |                    | V(CSIP – CSIN) = 20.48mV                                                                                                             | -5  |     | 3    |      |

| Accuracy                                                    |                    | V(CSIP – CSIN) = 10.24mV                                                                                                             | -8  |     | 6    |      |

|                                                             |                    | V(CSIP – CSIN) = 5.12mV                                                                                                              | -15 |     | 10   |      |

| Maximum Capacitance<br>at the IBUS Pin<br>( <u>Note 7</u> ) | CIBUS_MAX          |                                                                                                                                      |     |     | 100  | pF   |

| Input Common Mode<br>Range                                  | VCSOP_CSON_RNG     |                                                                                                                                      | 3.8 |     | 19.2 | V    |

| IBAT Output Clamp<br>Voltage                                | VIBAT_CLAMP        |                                                                                                                                      | 3.1 | 3.2 | 3.3  | V    |

| IBAT Output Current                                         | IIBAT              |                                                                                                                                      |     |     | 1    | mA   |

| Charge and Discharge                                        | Aibat              | IBAT_GAIN (0x12[3]) = 0                                                                                                              | -   | 8   |      | V/V  |

| Current Sensing Gain                                        |                    | IBAT_GAIN (0x12[3]) = 1                                                                                                              |     | 16  |      | V/V  |

|                                                             |                    | V(CSOP - CSON) = 40.96mV                                                                                                             | -2  |     | 2    |      |

| Charge and Discharge<br>Current Monitor                     | Vibat acc          | V(CSOP - CSON) = 20.48mV                                                                                                             | -4  |     | 4    | %    |

| Accuracy                                                    | VIBAT_ACC          | V(CSOP - CSON) = 10.24mV                                                                                                             | -7  |     | 7    | /0   |

|                                                             |                    | V(CSOP - CSON) = 5.12mV                                                                                                              | -15 |     | 15   |      |

| Maximum Capacitance<br>at the IBAT Pin<br>( <u>Note 7</u> ) | Сіват_мах          |                                                                                                                                      |     |     | 100  | pF   |

| <b>RT9478N</b> |  |

|----------------|--|

|----------------|--|

| Parameter                                                | Symbol                   | Test Conditions                       | Min  | Тур  | Мах  | Unit |  |  |  |  |  |

|----------------------------------------------------------|--------------------------|---------------------------------------|------|------|------|------|--|--|--|--|--|

| Vmin Active Protection PROCHOT Comparator                |                          |                                       |      |      |      |      |  |  |  |  |  |

| VAP VSYS Rising<br>Threshold 1                           | VSYS_VAP1_R              | VSYS_TH1 (0x33 [7:2])<br>= 100000     | 6.3  | 6.5  | 6.65 | V    |  |  |  |  |  |

| VAP VSYS Falling<br>Threshold 1                          | VSYS_VAP1_F              | VSYS_TH1 (0x33 [7:2])<br>= 100000     | 6.2  | 6.4  | 6.65 | V    |  |  |  |  |  |

| VAP VSYS Threshold 1<br>Hysteresis                       | VSYS_VAP1_HYS            |                                       |      | 100  |      | mV   |  |  |  |  |  |

| VSYS Threshold 1<br>Falling Deglitch for VAP<br>Shooting | tDEGLITCH_VSYS_<br>VAP1  |                                       |      | 4    |      | μs   |  |  |  |  |  |

| VAP VSYS Rising<br>Threshold 2                           | Vsys_vap2_r              | VSYS_TH2 (0x37 [7:2])<br>= 0x011011   | 5.8  | 6    | 6.15 | V    |  |  |  |  |  |

| VAP VSYS Falling<br>Threshold 2                          | VSYS_VAP2_F              | VSYS_TH2 (0x37 [7:2])<br>= 0x011011   | 5.7  | 5.9  | 6.05 | V    |  |  |  |  |  |

| VAP VSYS Threshold 2<br>Hysteresis                       | Vsys_vap2_hys            |                                       |      | 100  |      | mV   |  |  |  |  |  |

| VSYS Threshold 2<br>Falling Deglitch for<br>Throttling   | tdeglitch_vsys_<br>_vap2 |                                       |      | 4    |      | μs   |  |  |  |  |  |

| VAP Mode VBUS Rising<br>Threshold                        | VBUS_VAP_R               | VBUS_VAP_TH (0x37[15:9])<br>= 0000101 | 3.65 | 3.85 | 4.0  | V    |  |  |  |  |  |

| VAP Mode VBUS Falling<br>Threshold                       | VBUS_VAP_F               | VBUS_VAP_TH (0x37[15:9])<br>= 0000101 | 3.5  | 3.7  | 3.85 | V    |  |  |  |  |  |

| VAP Mode VBUS<br>Threshold Hysteresis                    | VBUS_VAP_HYS             |                                       |      | 150  |      | mV   |  |  |  |  |  |

| VBUS Falling Deglitch<br>for Throttling                  | tdeglitch_vbus_<br>_vap  |                                       |      | 4    |      | μs   |  |  |  |  |  |

| Protection Comparators                                   | ;<br>;                   |                                       |      |      |      |      |  |  |  |  |  |

| VSYS Undervoltage<br>Rising Threshold                    | VSYS_UVP_R               | VSYS_UVP (0x36[15:13])<br>= 001       | 3.7  | 3.8  | 3.9  | V    |  |  |  |  |  |

| VSYS Undervoltage<br>Falling Threshold                   | VSYS_UVP_F               | VSYS_UVP (0x36[15:13])<br>= 001       | 3.55 | 3.65 | 3.75 | V    |  |  |  |  |  |

| VSYS Undervoltage<br>Hysteresis                          | VSYS_UVP_HYS             |                                       |      | 150  |      | mV   |  |  |  |  |  |

| VBUS Undervoltage<br>Rising Threshold                    | Vbus_uvlo_r              |                                       | 3.1  | 3.2  | 3.3  | V    |  |  |  |  |  |

| VBUS Undervoltage<br>Falling Threshold                   | VBUS_UVLO_F              |                                       | 3    | 3.1  | 3.2  | V    |  |  |  |  |  |

| VBUS Undervoltage<br>Hysteresis                          | VBUS_UVLO_HYS            |                                       |      | 100  |      | mV   |  |  |  |  |  |

| VBUS Converter Enable<br>Rising Threshold                | VBUS_CONVEN_R            |                                       | 3.7  | 3.8  | 3.9  | V    |  |  |  |  |  |

| VBUS Converter Enable<br>Falling Threshold               | VBUS_CONVEN_F            |                                       | 3.4  | 3.5  | 3.6  | V    |  |  |  |  |  |

| VBUS Converter Enable<br>Hysteresis                      | VBUS_CONVEN_HYS          |                                       |      | 300  |      | mV   |  |  |  |  |  |

## RICHTEK

| Parameter                                       | Symbol                      | Test Conditions                                               | Min   | Тур  | Мах   | Unit |

|-------------------------------------------------|-----------------------------|---------------------------------------------------------------|-------|------|-------|------|

| VBUS Overvoltage<br>Rising Threshold            | VBUS_OVP_R                  |                                                               | 26    | 26.8 | 27.7  | V    |

| VBUS Overvoltage<br>Falling Threshold           | VBUS_OVP_F                  |                                                               | 25    | 25.8 | 26.7  | V    |

| VBUS Overvoltage<br>Hysteresis                  | VBUS_OVP_HYS                |                                                               |       | 1    |       | V    |

| VBUS Deglitch<br>Overvoltage Rising             | tDEGLITCH_VBUS_<br>OVP_R    |                                                               |       | 100  |       | μs   |

| VBUS Deglitch<br>Overvoltage Falling            | tDEGLITCH_VBUS_<br>OVP_F    |                                                               |       | 1    |       | ms   |

| VBUS (OTG)<br>Undervoltage Falling<br>Threshold | VBUS_OTG_UVP_F              | As percentage of OTG_VOL (0x3B[13:2])                         |       | 85   |       | %    |

| VBUS (OTG)<br>Undervoltage Deglitch<br>Time     | tdeglitch_vbus_<br>_otg_uvp |                                                               |       | 7    |       | ms   |

| VBUS (OTG)<br>Overvoltage Rising<br>Threshold   | VBUS_OTGOVP_R               | As percentage of OTG_VOL (0x3B[13:2])                         |       | 110  |       | %    |

| VBUS (OTG)<br>Overvoltage Deglitch<br>Time      | tdeglitch_vbus_<br>_otg_uvp |                                                               |       | 10   |       | ms   |

| VBAT Undervoltage<br>Rising Threshold           | VBAT_UVLO_R                 | VCSON rising                                                  | 3.58  | 3.7  | 3.82  | V    |

| VBAT Undervoltage<br>Falling Threshold          | VBAT_UVLO_F                 | VCSON falling                                                 | 3.46  | 3.58 | 3.7   | V    |

| VBAT Undervoltage<br>Hysteresis                 | Vbat_uvlo_hys               |                                                               |       | 120  |       | mV   |

| VBAT OTG Enable<br>Rising Threshold             | VBAT_OTGEN_R                | VCSON rising                                                  | 4.28  | 4.4  | 4.52  | V    |

| VBAT OTG Enable<br>Falling Threshold            | VBAT_OTGEN_F                | VCSON falling                                                 | 3.93  | 4.05 | 4.17  | V    |

| VBAT OTG Enable<br>Hysteresis                   | VBAT_OTGEN_HYS              |                                                               |       | 350  |       | mV   |

|                                                 |                             | As percentage of VBAT_REG(0x15[14:3]), $6.5V \le VBAT < 7.4V$ | 102   | 104  | 106   |      |

| VBAT Overvoltage<br>Rising Threshold            | Vbat_ovp_r                  | As percentage of VBAT_REG(0x15[14:3]), 7.4V $\leq$ VBAT < 11V | 102.5 | 104  | 105.5 | %    |

|                                                 |                             | As percentage of VBAT_REG(0x15[14:3]), $11V \leq VBAT$        | 103   | 104  | 105   |      |

| Parameter                                                                              | Symbol                   | Test Conditions                                                                                             | Min   | Тур  | Max   | Unit |  |

|----------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------|-------|------|-------|------|--|

|                                                                                        |                          | As percentage of VBAT_REG(0x15[14:3]), $6.5V \le VBAT < 7.4V$                                               | 100   | 102  | 104   |      |  |

| VBAT Overvoltage<br>Falling Threshold                                                  | VBAT_OVP_F               | As percentage of VBAT_REG(0x15[14:3]), 7.4V $\leq$ V <sub>BAT</sub> < 11V                                   | 100.5 | 102  | 103.5 | %    |  |

|                                                                                        |                          | As percentage of VBAT_REG(0x15[14:3]), $11V \le VBAT$                                                       | 101   | 102  | 103   |      |  |

| VBAT Overvoltage<br>Hysteresis                                                         | VBAT_OVP_HYS             | As percentage of<br>VBAT_REG(0x15[14:3])                                                                    |       | 2    |       | %    |  |

| Discharge Current during<br>BATOVP                                                     | IDISCHG_BAT_OVP          | Discharge current through the VSYS pin                                                                      |       | 40   |       | mA   |  |

|                                                                                        |                          | VSYS_OVP (0x40[14:12]) =<br>000 (Depends on cell count),<br>2s by CELL_BATPRES                              | 11.7  | 12   | 12.2  |      |  |

| System Overvoltage<br>Rising Threshold to Turn<br>Off Converter                        | Vsys_ovp_r               | VSYS_OVP (0x40[14:12]) =<br>000 (Depends on cell count),<br>3s by CELL_BATPRES                              | 19    | 19.5 | 20    | V    |  |

|                                                                                        |                          | VSYS_OVP (0x40[14:12]) =<br>000 (Depends on cell count),<br>4s, by CELL_BATPRES                             | 19    | 19.5 | 20    |      |  |

| System Overvoltage<br>Hysteresis                                                       | Vsys_ovp_hys             |                                                                                                             |       | 200  |       | mV   |  |

| Discharge Current during SYSOVP                                                        | IDISCHG_SYS_OVP          | Discharge current through the VSYS pin                                                                      |       | 40   | 1     | mA   |  |

| Pre-Charge to Fast Char                                                                | ge Transition            |                                                                                                             |       |      |       |      |  |

| Pre-Charge to Fast<br>Charge Mode Transient                                            |                          | As percentage of VSYS_MIN<br>(0x3E[15:8]), VBAT < 6.5V                                                      | 97.5  | 100  | 102.5 | 0/   |  |

| Threshold, Vcson Rising                                                                | Vprechg_r                | As percentage of VSYS_MIN (0x3E[15:8]), VBAT $\geq$ 6.5V                                                    | 98    | 100  | 102   | )2   |  |

| Pre-Charge to Fast<br>Charge Mode Transient<br>Threshold, V <sub>CSON</sub><br>Falling | Vprechg_f                | As percentage of VSYS_MIN<br>(0x3E[15:8])                                                                   | -     | 97.5 |       | %    |  |

| Fast Charge to Pre-<br>Charge Mode Transient<br>Threshold Hysteresis                   | Vprechg_hys              | As percentage of VSYS_MIN<br>(0x3E[15:8])                                                                   |       | 2.5  |       | %    |  |

| Input Overcurrent Comp                                                                 | arator                   |                                                                                                             |       |      |       |      |  |

| CSIP to CSIN Rising<br>Threshold                                                       | IBUS_OCP1_R              | As percentage of<br>IAICR2 (0x33[15:11]),<br>IBUS_OCP1_TH (0x31[2])<br>= 1 (200% of IAICR2), IAICR2<br>> 2A | 180   | 200  | 220   | %    |  |

| Rising Deglitch Time                                                                   | tDEGLITCH_<br>BUS_OCP1_R |                                                                                                             |       | 250  |       | μs   |  |

| Relax Time                                                                             | tRELAX_BUS_OCP1          |                                                                                                             |       | 250  | -     | ms   |  |

| Parameter                                                                     | Symbol          | Test Conditions                                                                  | Min | Тур | Мах | Unit |  |  |  |  |

|-------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|

| Converter Overcurrent Comparator                                              |                 |                                                                                  |     |     |     |      |  |  |  |  |

|                                                                               |                 | Q2_OCP (0x31[5])<br>= 1                                                          |     | 150 |     | mV   |  |  |  |  |

|                                                                               | VLIM_Q2_OCP     | Q2_OCP (0x31[5])<br>= 0                                                          |     | 210 |     |      |  |  |  |  |

| Converter Overcurrent<br>Limit Across Q2<br>MOSFET Drain to<br>Source Voltage | VLIM Q2 OCP S   | Q2_OCP (0x31[5])<br>= 1 (150mV),<br>Vsys < Vsys_uvlo_f or<br>Vcson < Vbat_uvlo_r |     | 45  |     | mV   |  |  |  |  |

|                                                                               | VLIM_Q2_OCP_S   | Q2_OCP (0x31[5])<br>= 0 (210mV),<br>Vsys < Vsys_uvlo_f or<br>Vcson < Vbat_uvlo_r |     | 60  |     | iiiv |  |  |  |  |

|                                                                               |                 | IBUS_OCP2_TH (0x31[4])<br>= 1,<br>RSNS_IN (0x30[11])<br>= 0 (10mΩ)               |     | 150 |     |      |  |  |  |  |

| Converter Overcurrent<br>Limit Across CSIP -                                  |                 | IBUS_OCP2_TH (0x31[4])<br>= 0,<br>RSNS_IN (0x30[11])<br>= 0 (10mΩ)               |     | 280 |     |      |  |  |  |  |

| CSIN Input Current<br>Sensing Resistor                                        | VBUS_OCP2       | IBUS_OCP2_TH (0x31[4])<br>= 0,<br>Vsys < Vsys_uvlo_f or<br>Vcson < Vbat_uvlo_r   |     | 150 |     | mV   |  |  |  |  |

|                                                                               |                 | IBUS_OCP2_TH (0x31[4])<br>= 1,<br>Vsys < Vsys_uvlo_f or<br>Vcson < Vbat_uvlo_r   |     | 90  |     |      |  |  |  |  |

| Ship-Mode Discharge C                                                         | Current         |                                                                                  |     |     |     | •    |  |  |  |  |

|                                                                               | ICSON_DCHG      | EN_SHIP_DCHG (0x30[1])<br>= 1 (enabled)                                          |     | 10  |     |      |  |  |  |  |

| Discharge VBAT Cap                                                            | ICSOP_DCHG      | EN_SHIP_DCHG (0x30[1])<br>= 1 (enabled)                                          |     | 10  |     | mA   |  |  |  |  |

| Over-Temperature Prot                                                         | ection (OTP)    |                                                                                  |     |     |     |      |  |  |  |  |

| Over-Temperature<br>Protection Rising<br>Threshold ( <u>Note 7</u> )          | Totp_r          |                                                                                  |     | 140 |     | °C   |  |  |  |  |

| Over-Temperature<br>Protection Falling<br>Threshold ( <u>Note 7</u> )         | Totp_f          |                                                                                  |     | 125 |     | °C   |  |  |  |  |

| Over-Temperature<br>Protection Threshold<br>Hysteresis ( <u>Note 7</u> )      | Тотр_нуѕ        |                                                                                  |     | 15  |     | °C   |  |  |  |  |

| Over-Temperature<br>Protection Rising<br>Deglitch                             | tDEGLITCH_OTP_R |                                                                                  |     | 100 |     | μs   |  |  |  |  |

| Over-Temperature<br>Protection Falling<br>Deglitch                            | tDEGLITCH_OTP_F |                                                                                  |     | 12  |     | ms   |  |  |  |  |

Copyright © 2025 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

**RT9478M**

| Parameter                                                               | Symbol            | Test Conditions                                               | Min    | Тур     | Max       | Unit    |

|-------------------------------------------------------------------------|-------------------|---------------------------------------------------------------|--------|---------|-----------|---------|

| ICRIT PROCHOT Compa                                                     | rator             |                                                               |        |         |           |         |

| Input Current Rising<br>Threshold for Throttling<br>as 10% above IAICR2 | Icrit             | Only when IAICR2 setting is higher than 2A                    | 104    | 110     | 118       | %       |

| INOM PROCHOT Compa                                                      | irator            |                                                               |        |         |           |         |

| INOM Rising Threshold<br>as 10% above ILIM1                             | linom             | Only when IAICR1 setting is<br>higher than 2A                 | 104    | 110     | 117       | %       |

| Battery Discharge Curre                                                 | ent Limit PROCHOT | Comparator                                                    |        |         |           |         |

| IDCHG Threshold1                                                        | IDISCHG1          | IDCHG_TH1 (0x34[15:10])<br>= 010000,<br>with 10mΩ Rsense_bat  | <br>96 | 8192    | <br>103.5 | mA<br>% |

| IDCHG Threshold1<br>Deglitch Time                                       | tDEGLITCH_DISCHG1 | IDCHG_DEG1 (0x34[9:8])<br>= 01                                | 1.0625 | 1.25    | 1.4375    | s       |

| IDCHG Threshold2                                                        | IDISCHG2          | IDCHG_TH1 (0x34[15:10])<br>= 010000,<br>IDCHG_TH2 (0x36[5:3]) |        | 12288   |           | mA      |

|                                                                         |                   | = 001 (150% of IDCHG1_TH1) with $10m\Omega$ RSENSE_BAT        | 96     |         | 103.5     | %       |

| IDCHG Threshold2<br>Deglitch Time                                       | tDEGLITCH_DISCHG2 | IDCHG_DEG2 (0x36[7:6])<br>= 01                                |        | 1.6     |           | ms      |

| Independent Comparato                                                   | r                 |                                                               |        |         |           |         |

| Independent Comparator                                                  | VCMPIN_F          | CMP_REF (0x30[7])<br>= 1, CMPIN falling                       | 1.17   | 1.2     | 1.23      | V       |

| Threshold                                                               |                   | CMP_REF (0x30[7])<br>= 0, CMPIN falling                       | 2.27   | 2.3     | 2.33      | v       |

| Independent Comparator<br>Hysteresis                                    | VCMPIN_HYS        | CMPIN rising                                                  |        | 100     |           | mV      |

| Independent Comparator<br>Threshold in Low Power<br>Mode                | VCMPIN_LPWR_F     | CMPIN rising,<br>EN_PROCHOT_LPWR<br>(0x30[14]) = 1 (enabled)  |        | 1.2     |           | V       |

| Converter Switching Fre                                                 | equency           |                                                               |        |         |           |         |

|                                                                         |                   | PWM_FREQ (0x12[9])<br>= 0                                     | 1020   | 1200    | 1260      |         |

| Converter Switching<br>Frequency                                        | fsw               | PWM_FREQ (0x12[9])<br>= 1                                     | 680    | 800     | 840       | kHz     |

|                                                                         |                   | PWM_LOWFREQ (0x40[10])<br>= 1                                 | 612    | 720     | 756       |         |

| Converter OOA Minimum<br>Frequency                                      | fsw_ooa_min       | EN_OOA (0x12[10])<br>= 1 (OOA enabled)                        |        | 25      |           | kHz     |

|                                                                         |                   | DITHER_EN (0x36[12:11])<br>= 00                               |        | Disable |           |         |

| Frequency Dither<br>Configuration                                       | fsw_dither        | DITHER_EN (0x36[12:11])<br>= 01                               |        | ±2      |           | %       |

|                                                                         |                   | DITHER_EN (0x36[12:11])<br>= 10                               |        | ±4      |           |         |

|                                                                         |                   |                                                               |        |         |           |         |

| Parameter                                                         | Parameter Symbol Test Conditions |                                                                                                     | Min | Тур | Мах  | Unit |

|-------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|------|------|

|                                                                   |                                  | DITHER_EN (0x36[12:11])<br>= 11                                                                     |     | ±6  |      |      |

| BATFET Gate Driver                                                | ·                                |                                                                                                     |     |     |      |      |

| Gate Drive Voltage on<br>BATFET                                   | VBGATE_ON                        | VBGATE = VVSYS – VBGATE                                                                             | 8.5 | 10  | 11.5 | V    |

| Drain-Source Voltage on<br>BATFET during Ideal<br>Diode Operation | VF_IDEAL                         | VF_IDEAL = VCSON – VVSYS                                                                            |     | 30  |      | mV   |

| BATFET Turn-On<br>Resistance                                      | RBGATE_ON                        | Measured by sourcing 10μA<br>and 100μA current to BGATE                                             | 1.5 | 2.5 | 4    | kΩ   |

| BATFET Turn-Off<br>Resistance                                     | RBGATE_OFF                       | Measured by sinking 10µA current from BGATE                                                         |     | 0.8 | 2.1  | kΩ   |

| Input High-Side Driver (                                          | UGATE1)                          |                                                                                                     |     |     |      |      |

| High-Side Driver (Q1)                                             |                                  | VBTST1 – VSW1 = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 1 (strong drive disabled)                         |     | 3.1 |      |      |

| Turn-On Resistance                                                | Rds_on_q1                        | VBTST1 – VSW1 = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 0 (strong drive enabled)                          |     | 1.6 |      | Ω    |

| High-Side Driver (Q1)                                             |                                  | VBTST1 - VSW1 = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 1 (strong drive disabled)                         |     | 0.8 |      |      |

| Turn-Off Resistance                                               | RDS_OFF_Q1                       | V <sub>BTST1</sub> – V <sub>SW1</sub> = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 0 (strong drive enabled)  |     | 0.5 |      | Ω    |

| Input High-Side Driver (                                          | UGATE2)                          |                                                                                                     |     |     | 1    | 1    |

| High-Side Driver (Q4)                                             | Rds on Q4                        | V <sub>BTST2</sub> – V <sub>SW2</sub> = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 1 (strong drive disabled) |     | 3.2 |      | Ω    |

| Turn-On Resistance                                                | 1103_011_04                      | VBTST2 – VSW2 = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 0 (strong drive enabled)                          |     | 1.7 |      | 22   |

| High-Side Driver (Q4)                                             |                                  | VBTST2 – VSW2 = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 1 (strong drive disabled)                         | 1   | 0.8 |      | 0    |

| Turn-Off Resistance                                               | Rds_off_q4                       | VBTST2 – VSW2 = 5V,<br>DIS_STRGDRV (0x12[8])<br>= 0 (strong drive enabled)                          | -   | 0.5 |      | Ω    |

| Input Low-Side Driver (L                                          | _GATE1)                          |                                                                                                     |     |     |      |      |

| Low-Side Driver (Q2)<br>Turn-On Resistance                        | Rds_on_q2                        | VREGN = 5V                                                                                          |     | 1.7 |      | Ω    |

| Low-Side Driver (Q2)<br>Turn-Off Resistance                       | RDS_OFF_Q2                       | VREGN = 5V                                                                                          |     | 0.7 |      | Ω    |

| Output Low-Side Driver                                            | (LGATE2)                         |                                                                                                     |     | -   |      |      |

| Low-Side Driver (Q3)<br>Turn-On Resistance                        | Rds_on_q3                        | VREGN = 5V                                                                                          |     | 1.8 |      | Ω    |

| Parameter                                      | Symbol            | Test Conditions                                        | Min  | Тур  | Max  | Unit |

|------------------------------------------------|-------------------|--------------------------------------------------------|------|------|------|------|

| Low-Side Driver (Q3)<br>Turn-Off Resistance    | Rds_off_q3        | VREGN = 5V                                             |      | 0.3  |      | Ω    |

| Integrated Bootstrap Sw                        | vitch (BTST1/BTST | 2)                                                     |      |      |      |      |

| On Resistance                                  | RBTST_ON          |                                                        | 1    | 2.1  | 4    | Ω    |

| Reverse Breakdown<br>Voltage                   | Vbtst_rbd         |                                                        | 25   |      |      | V    |

| Internal Soft-Start Durin                      | g Charge Enable   |                                                        |      |      | 1    | 1    |

| Charge Current Soft-<br>Start Rate             | SRICHG            |                                                        |      | 64   |      | A/s  |

| Converter Soft-Start                           |                   |                                                        |      |      |      |      |

| VSYS Slew Rate                                 | SRsys             | VCSON < VSYS_MIN<br>(0x3E[15:8])                       |      | 12.5 |      | V/ms |

| VBUS Slew Rate<br>(In OTG Mode)                | SRBUS             |                                                        |      | 8    |      | V/ms |

| Logic Pins (CHG_OK, O                          | TG_VAP, and ILIM  | _HIZ or SCL/SDA if Specified)                          | )    |      | 1    | 1    |

|                                                |                   | SCL/SDA Option Code A                                  |      |      | 0.8  |      |

| Input Low Threshold                            | VIL_SMBUS         | SCL/SDA Option Code B                                  |      |      | 0.4  | V    |

| Lessent I Park Theory I and I                  |                   | SCL/SDA Option Code A                                  | 1.4  |      |      |      |

| Input High Threshold                           | VIH_SMBUS         | SCL/SDA Option Code B                                  | 1.3  |      |      | V    |

| Output Low Voltage                             | Vol_smbus         | SCL/SDA<br>Drain current = 5mA                         |      |      | 0.4  | V    |

| Leakage Current                                | ILK_SMBUS         | Pin voltage = 5V                                       |      |      | 1    | μA   |

| Output Low Voltage                             | Vol_od            | Drain current = 5mA<br>At CHG_OK and CMPOUT<br>pins    |      |      | 0.3  | V    |

| Leakage Current                                | Ilk_od            | Pin voltage = 5V<br>At CHG_OK and CMPOUT<br>pins       |      |      | 1    | μΑ   |

| Output Low Voltage                             | Vol_prochot       | 50Ω is pulled up to<br>1.05V/5mA                       |      |      | 0.3  | V    |

| Leakage Current                                | ILK_PROCHOT       | Pin voltage = 5V<br>At PROCHOT pin                     |      |      | 1    | μA   |

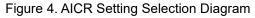

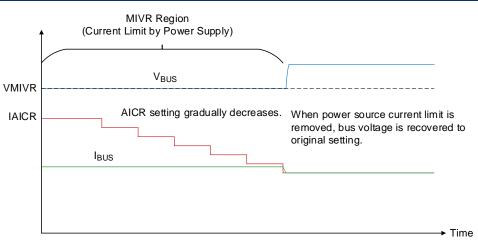

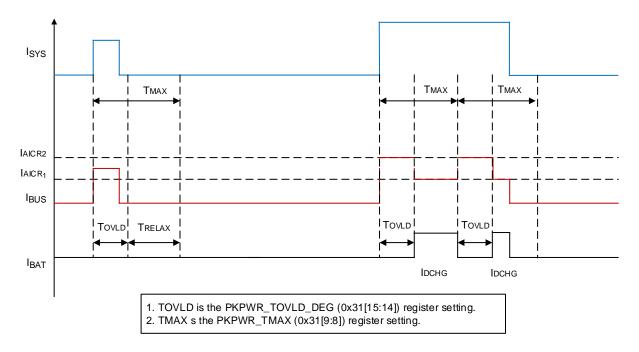

| Input Low Threshold                            | VIL_LOGIC         | At OTG_VAP pin                                         |      |      | 0.8  | V    |