## **RT9297**

## **3A High-Performance Boost Converter**

### **1** General Description

The RT9297 is a high-performance boost converter that provides a regulated supply voltage for activematrix thin-film transistor (TFT) liquid-crystal displays (LCDs).

The boost converter incorporates current-mode, fixedfrequency, pulse-width modulation (PWM) circuitry with a built-in N-Channel power MOSFET to achieve high efficiency and fast transient response.

The RT9297 is available in a WDFN-10L 3x3 package. The recommended junction temperature range is  $-40^{\circ}$ C to 125°C, and the ambient temperature range is  $-40^{\circ}$ C to 85°C.

### 2 Ordering Information

## RT9297

# —Pin 1 Orientation Empty: Quadrant 1 (2): Quadrant 2, Follow EIA-481

-----**Package Type**<sup>(1)</sup> QW: WDFN-10L 3x3 (W-Type)

-Lead Plating System G: Green (Halogen Free and Pb Free)<sup>(2)</sup>

#### Note 1.

- Marked with <sup>(1)</sup> indicated: Compatible with the current requirements of IPC/JEDEC J-STD-020.

- Marked with <sup>(2)</sup> indicated: Richtek products are Richtek Green Policy compliant.

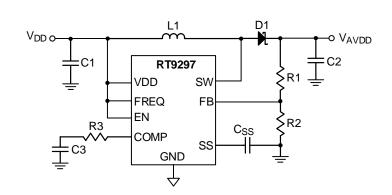

### **6 Simplified Application Circuit**

### 3 Features

Technical Documentation

High Efficiency up to 90%

Evaluation Boards

- Adjustable Output Voltage: VDD to 24V

- Wide Input Supply Voltage: 2.6V to 5.5V

- Input Undervoltage-Lockout

- Pin-Programmable Switching Frequency 640kHz/1.2MHz

- Programmable Soft-Start

- Small 10-Lead WDFN Package

### 4 Applications

- Notebook Computer Displays

- LCD Monitor Panels

- LCD TV Panels

### 5 Marking Information

EZ=YM DNN EZ=: Product Code YMDNN: Date Code

OP=: Product Code YMDNN: Date Code

## **Table of Contents**

| 1  | General Description               | 1  |

|----|-----------------------------------|----|

| 2  | Ordering Information              | 1  |

| 3  | Features                          | 1  |

| 4  | Applications                      | 1  |

| 5  | Marking Information               | 1  |

| 6  | Simplified Application Circuit    | 1  |

| 7  | Pin Configuration                 | 3  |

| 8  | Functional Pin Description        | 3  |

| 9  | Functional Block Diagram          | 4  |

| 10 | Absolute Maximum Ratings          | 5  |

| 11 | Recommended Operating Conditions  |    |

| 12 | Electrical Characteristics        | 5  |

| 13 | Typical Application Circuit       | 7  |

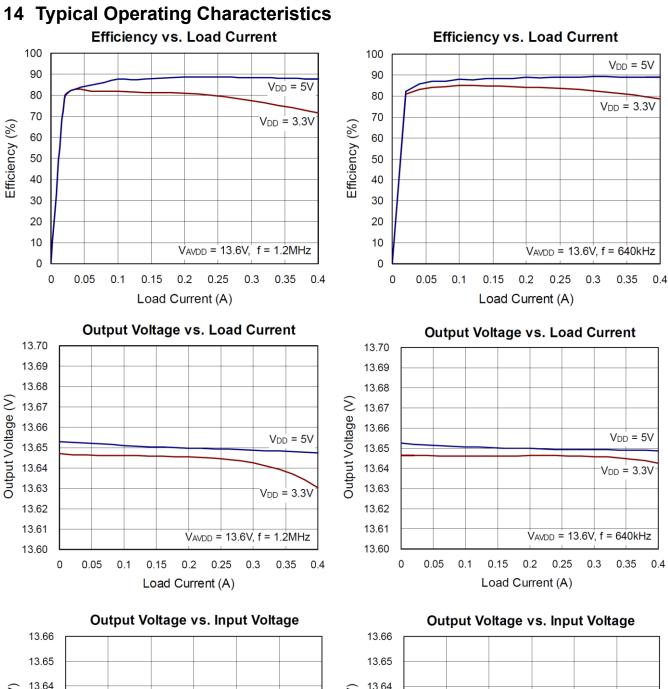

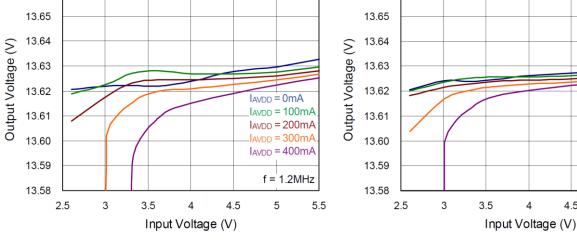

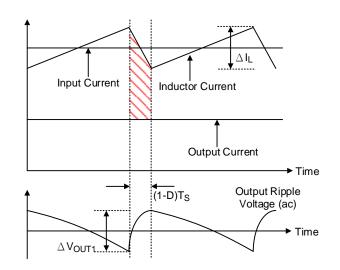

| 14 | Typical Operating Characteristics | 8  |

| 15 | Application Information           | 10 |

|    | 15.1 Boost Converter              |    |

|    | 15.2 Soft-Start Function          |    |

|    |                                   |    |

|    | 15.3  | Output Voltage Setting             | 10 |

|----|-------|------------------------------------|----|

|    | 15.4  | Loop Compensation                  | 10 |

|    | 15.5  | Overcurrent Protection             | 10 |

|    | 15.6  | Over-Temperature Protection        | 11 |

|    | 15.7  | Inductor Selection                 | 11 |

|    | 15.8  | Diode Selection                    | 11 |

|    | 15.9  | Capacitor Selection                | 11 |

|    | 15.10 | Input Capacitor Selection          | 12 |

|    | 15.11 | Thermal Considerations             | 12 |

|    | 15.12 | Layout Considerations              | 13 |

| 16 |       | e Dimension                        |    |

| 17 | Footp | rint Information                   | 16 |

| 18 | Packi | ng Information                     | 17 |

|    | 18.1  | Tape and Reel Data                 | 17 |

|    | 18.2  | Tape and Reel Packing              | 20 |

|    | 18.3  | Packing Material Anti-ESD Property | 23 |

| 19 | Datas | heet Revision History              | 24 |

|    |       |                                    |    |

www.richtek.com

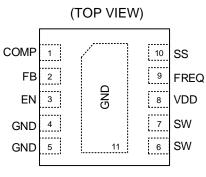

## 7 Pin Configuration

### 8 Functional Pin Description

| Pin No.                   | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                       |

|---------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | COMP     | Compensation pin. Connect a series RC circuit from the COMP pin to ground for error amplifier compensation.                                                                                                                                                                                                                        |

| 2                         | FB       | Feedback pin. The nominal feedback regulation voltage is 1.24V. Connect an external resistor voltage divider between the boost converter's output (VAVDD) and ground (GND), with the center tap connected to the FB pin. To reduce noise coupling, place the voltage-divider close to the IC and minimize the trace area.          |

| 3                         | EN       | Enable control input. Drive EN low to turn off the boost converter.                                                                                                                                                                                                                                                                |

| 4, 5,<br>11 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                                        |

| 6, 7                      | SW       | Switch node. SW serves as the drain of the internal MOSFET. To minimize electromagnetic interference (EMI), connect the junction of the inductor and rectifier diode to SW and ensure the trace area is as small as possible.                                                                                                      |

| 8                         | VDD      | Supply pin. Bypass VDD by connecting a ceramic capacitor with a minimum value of $1\mu F$ directly to GND.                                                                                                                                                                                                                         |

| 9                         | FREQ     | Frequency-select input. The oscillator frequency is set to 640kHz when the FREQ input is low, and is set to 1.2MHz when FREQ is high. Additionally, this input features a pull-down current of $6\mu$ A.                                                                                                                           |

| 10                        | SS       | Soft-start control pin. Connect a soft-start capacitor (CSS) to this pin. A $4\mu$ A constant current charges the soft-start capacitor. When EN is connected to GND, the soft-start capacitor is discharged. When EN is connected to VDD high, the soft-start capacitor is charged to VDD. Leave floating if not using soft-start. |

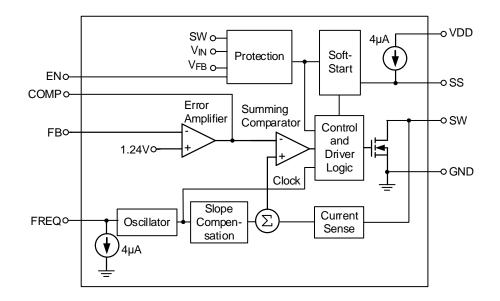

## 9 Functional Block Diagram

www.richtek.com

### **10 Absolute Maximum Ratings**

#### (Note 2)

| SW to GND                                             | 0.3V to 26V      |

|-------------------------------------------------------|------------------|

| Other Pins to GND                                     | 0.3V to 6V       |

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul> |                  |

| WDFN-10L 3x3                                          | - 1.667W         |

| Package Thermal Resistance ( <u>Note 3</u> )          |                  |

| WDFN-10L 3x3, θJA                                     | - 60°C/W         |

| WDFN-10L 3x3, θJC                                     | - 8.2°C/W        |

| Lead Temperature (Soldering, 10 sec.)                 | - 260°C          |

| Storage Temperature Range                             | - −65°C to 150°C |

| ESD Susceptibility ( <u>Note 4</u> )                  |                  |

| HBM (Human Body Model)                                | - 2kV            |

- Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3.  $\theta_{JA}$  is measured under natural convection (still air) at T<sub>A</sub> = 25°C with the component mounted on a low effectivethermal-conductivity single-layer test board on a JEDEC 51-3 thermal measurement standard.

- Note 4. Devices are ESD sensitive. Handling precautions are recommended.

### 11 Recommended Operating Conditions

#### (Note 5)

| ٠ | Supply Input Voltage, VDD  | 2.6V to 5.5V   |

|---|----------------------------|----------------|

| • | Junction Temperature Range | –40°C to 125°C |

| • | Ambient Temperature Range  | –40°C to 85°C  |

Note 5. The device is not guaranteed to function outside its operating conditions.

### 12 Electrical Characteristics

(V<sub>DD</sub> = 3.3V, T<sub>A</sub> =  $25^{\circ}C$ , unless otherwise specified.)

| Parameter                                | Symbol                             | Test Conditions              | Min | Тур | Мах | Unit |  |  |  |

|------------------------------------------|------------------------------------|------------------------------|-----|-----|-----|------|--|--|--|

| Supply Current                           |                                    |                              |     |     |     |      |  |  |  |

| Input Voltage Denge                      | \/                                 | V <sub>AVDD</sub> < 18V      | 2.6 |     | 5.5 | v    |  |  |  |

| Input Voltage Range Output Voltage Range | VDD                                | 18V < VAVDD < 24V            | 4   |     | 5.5 |      |  |  |  |

| Output Voltage Range                     | VAVDD                              |                              | Vdd |     | 24  | V    |  |  |  |

| Undervoltage-Lockout                     | VUVLO                              | V <sub>DD</sub> rising       |     | 2.4 |     | V    |  |  |  |

| Threshold                                | ervoltage-Lockout VUVLO VDD rising | Hysteresis                   |     | 50  |     | mV   |  |  |  |

| Quieseent Current                        |                                    | VFB = 1.3V, SW not switching |     | 0.5 |     |      |  |  |  |

| Quiescent Current                        | lQ                                 | VFB = 1V, SW switching       |     | 4   |     | mA   |  |  |  |

| Shutdown Current                         | ISHDN                              | EN = GND                     |     | 0.1 | 10  | μA   |  |  |  |

**RICHTEK** is a registered trademark of Richtek Technology Corporation. Copyright © 2024 Richtek Technology Corporation. All rights reserved. DS9297-04 November 2024

| Parameter                            | Symbol       | Test Conditions                         | Min          | Тур                      | Мах          | Unit |

|--------------------------------------|--------------|-----------------------------------------|--------------|--------------------------|--------------|------|

| Oscillator                           |              |                                         |              |                          |              | •    |

|                                      |              | FREQ = GND                              | 500          | 640                      | 750          |      |

| Oscillator Frequency                 | fsw          | FREQ = VIN                              | 1000         | 1240                     | 1500         | kHz  |

| Maximum Duty Cycle                   | Dмах         |                                         |              | 90                       |              | %    |

| Error Amplifier                      | ·            |                                         |              |                          |              | •    |

| Feedback Regulation<br>Voltage       | Vfb          |                                         | 1.22         | 1.24                     | 1.26         | V    |

| Feedback Input Bias<br>Current       | Ifb          |                                         |              | 125                      | 250          | nA   |

| Feedback Line<br>Regulation          | VLINE_REG_FB |                                         |              | 0.05                     | 0.2          | %∕∨  |

| Transconductance                     | gm           | $\Delta I = \pm 2.5 \mu A$ at COMP = 1V |              | 135                      |              | μAV  |

| Voltage Gain                         | Av           | FB to COMP                              |              | 700                      |              | V/V  |

| N-MOSFET                             |              |                                         |              |                          |              |      |

| Current Limit                        | ILIM         |                                         | 3            | 3.8                      | 5            | А    |

| On-Resistance                        | RDSON        |                                         |              | 125                      | 250          | mΩ   |

| Leakage Current                      | Ilk          | Vsw = 24V                               |              | 30                       | 45           | μA   |

| Current-Sense<br>Transresistance     | Rcs          |                                         |              | 0.25                     |              | V/A  |

| Soft-Start                           |              |                                         |              |                          |              |      |

| Charge Current                       | lss          |                                         |              | 4                        |              | μA   |

| Control Inputs                       |              |                                         |              |                          |              |      |

| EN, FREQ Input Voltage<br>Logic-Low  | VIL          |                                         |              |                          | 0.3 x<br>Vdd | V    |

| EN, FREQ Input Voltage<br>Logic-High | Vih          |                                         | 0.7 x<br>Vdd |                          |              | V    |

| EN, FREQ Input Voltage<br>Hysteresis | VIN_HYS      |                                         |              | 0.1 x<br>V <sub>DD</sub> |              | V    |

| FREQ Pull-Down Current               | IPD          |                                         |              | 6                        |              | μA   |

| EN Input Current                     | IEN          | EN = GND                                |              | 0.001                    | 1            | μA   |

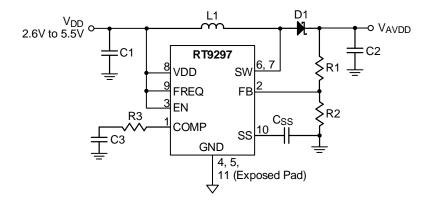

## **13 Typical Application Circuit**

7

www.richtek.com

IAVDD = 0mA

IAVDD = 100mA

I<sub>AVDD</sub> = 200mA

IAVDD = 300mA

I<sub>AVDD</sub> = 400mA

5

4.5

f = 640kHz

5.5

**RT9297**

Copyright © 2024 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

## **15 Application Information**

#### (<u>Note 6</u>)

The RT9297 is a high-performance boost converter designed to generate the voltage required by the panel source driver ICs. Detailed descriptions and component selection information follow.

#### 15.1 Boost Converter

The boost converter features a high-efficiency, current-mode PWM architecture that operates at frequencies of either 640kHz or 1.2MHz. It is designed for fast transient responses, enabling it to generate the necessary power supplies for the source drivers of TFT LCD displays. The high operating frequency permits the use of smaller components, which helps to reduce the overall thickness of the LCD panel. The output voltage can be set by configuring a resistive voltage-divider connected to the FB (feedback) pin. The error amplifier adjusts the COMP (compensation) voltage in response to the voltage sensed at the FB pin, thereby regulating the output voltage. To enhance stability, a slope compensation signal is added to the current-sense signal. This combined signal is then compared with the COMP voltage to determine the current trip point and duty cycle.

#### 15.2 Soft-Start Function

The RT9297 features a soft-start function designed to minimize inrush current during power-up. Upon powering on, an internal constant current source charges an external capacitor. This process limits the rate of voltage rise on the COMP pin during the charging period, which concurrently restricts the peak current in the inductor. When the power is turned off, the external capacitor is discharged, preparing it for the next soft-start cycle.

The soft-start function is facilitated by an external capacitor that is charged with a  $4\mu A$  (microampere) constant current. To ensure proper output voltage regulation, the capacitor must have a sufficient capacitance. A typical value for the soft-start capacitor is 33nF, with an acceptable range from 10nF to 100nF.

#### 15.3 Output Voltage Setting

The regulated output voltage is shown in the following equation:

$$V_{AVDD} = 1.24V x \left( 1 + \frac{R_1}{R_2} \right)$$

The recommended value for R2 should be up to  $10k\Omega$  without any sacrifice in performance. Placing the resistor divider as close as possible to the chip can help reduce noise sensitivity.

#### 15.4 Loop Compensation

The voltage feedback loop can be compensated with an external compensation network consisting of RCOMP and CCOMP. Choose RCOMP to set the high-frequency integrator gain for a fast transient response, and select CCOMP to set the integrator zero to maintain loop stability. For a typical application with VDD = 3.3V, VAVDD = 13.6V, C4 =  $4.7\mu$ F x 3, and L =  $3.6\mu$ H, the recommended values for compensation are as follows: RCOMP =  $56k\Omega$  and CCOMP = 330pF.

#### 15.5 Overcurrent Protection

The RT9297 boost converter features overcurrent protection to limit the peak current in the inductor, preventing potential damage to the inductor and diode. During the ON-time, if the inductor current exceeds the preset current limit, the internal SW switch turns off immediately, effectively shortening the duty cycle. As a result, the output voltage may drop if an overcurrent condition occurs. It is important to note that the current limit is also influenced by the input voltage, duty cycle, and the value of the inductor.

10

#### **Over-Temperature Protection** 15.6

The RT9297 boost converter is equipped with over-temperature protection function to prevent the chip from overheating. When the junction temperature exceeds 155°C, the device will shut down to protect itself. Once the temperature has decreased by approximately 30°C, the device will resume normal operation. To ensure continuous operation, it is recommended not to exceed the maximum junction temperature rating of 125°C.

#### 15.7 Inductor Selection

The inductance value is determined based on the maximum input current. A general rule of thumb is that the inductor current ripple should be between 20% and 40% of the maximum input current. Assuming we choose 40% as the criterion, then the calculation for the inductance will proceed accordingly.

$$I_{VDD(MAX)} = \frac{V_{AVDD} \times I_{AVDD(MAX)}}{\eta \times V_{DD}}$$

$IRIPPLE = 0.4 \times IVDD(MAX)$

where  $\eta$  is the efficiency, IVDD(MAX) is the maximum input current, IRIPPLE is the inductor current ripple.

Additionally, the peak input current is the sum of the maximum input current and half of the inductor current ripple.  $I_{PEAK} = 1.2 \times I_{VDD(MAX)}$

Note that the saturation current of the inductor must exceed the peak current (IPEAK). The inductance value can ultimately be determined using the following equation:

$$L = \frac{\eta x (V_{DD})^2 x (V_{AVDD} - V_{DD})}{0.4 x (V_{AVDD})^2 x I_{AVDD(MAX)} x f_{SW}}$$

where fsw represents the switching frequency of the system. To optimize system performance and minimize electromagnetic interference (EMI) issues, the use of a shielded inductor is recommended.

#### **Diode Selection** 15.8

A Schottky diode is an excellent choice for an asynchronous boost converter due to its low forward voltage drop. However, when selecting a Schottky diode, it is crucial to consider power dissipation, reverse voltage rating, and pulsating peak current as important parameters. It is advisable to select a diode with a reverse voltage rating that exceeds the maximum output voltage to ensure reliable operation.

#### 15.9 **Capacitor Selection**

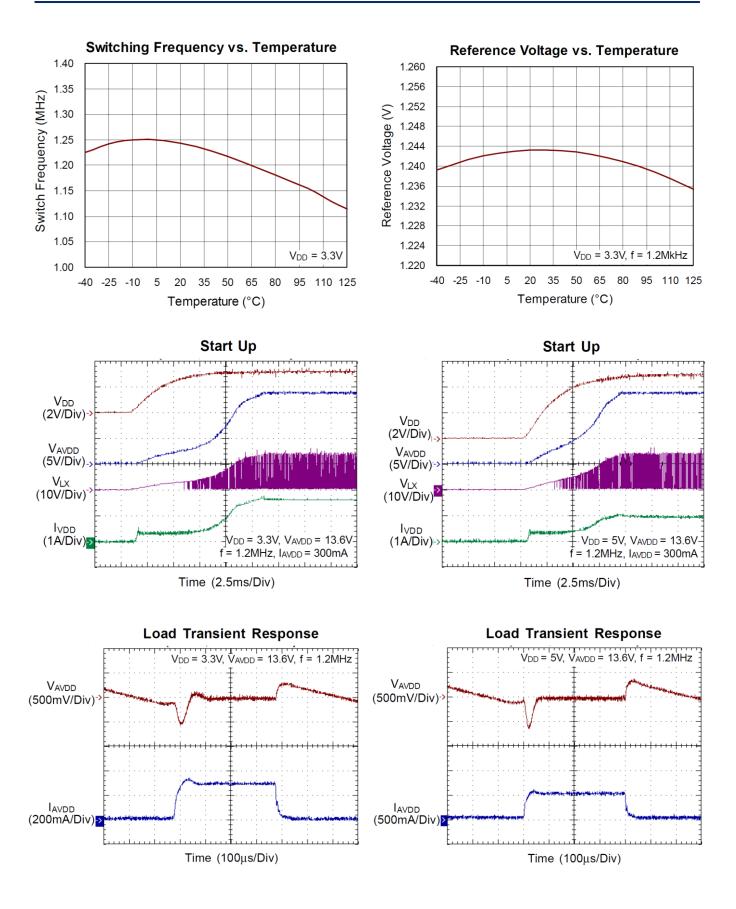

Output ripple voltage is an important metric for assessing performance. It comprises two components: one is the product of the input current and the Equivalent Series Resistance (ESR) of the output capacitor; the other is created by the charging and discharging cycles of the output capacitor. As shown in Figure 1,  $\Delta V_{OUT1}$  can be evaluated using the principle of ideal energy equalization. Based on the definition of charge (Q), the Q value can be calculated using the following equation:

$$Q = \frac{1}{2} \times \left[ \left( I_{IN} + \frac{1}{2} \Delta I_L - I_{OUT} \right) + \left( I_{IN} - \frac{1}{2} \Delta I_L - I_{OUT} \right) \right] \times \frac{V_{IN}}{V_{OUT}} \times \frac{1}{f_{SW}} = C_{OUT} \times \Delta V_{OUT1}$$

where fsw is the switching frequency, and  $\Delta I_L$  represents the inductor ripple current. To estimate the value of  $\Delta$ VOUT1, move COUT to the left side of the equation as shown below:

$$\Delta V_{OUT1} = \frac{D \times I_{OUT}}{\eta \times C_{OUT} \times f_{SW}}$$

**RICHTEK** is a registered trademark of Richtek Technology Corporation. Copyright © 2024 Richtek Technology Corporation. All rights reserved. DS9297-04 November 2024 www.richtek.com Finally, by incorporating the Equivalent Series Resistance (ESR) into the calculation, the total output ripple voltage can be determined using the following equation:

$$\Delta V_{OUT} = I_{IN} \times ESR + \frac{D \times I_{OUT}}{\eta \times C_{OUT} \times f_{SW}}$$

Figure 1. The Output Ripple Voltage without the Contribution of ESR

#### 15.10 Input Capacitor Selection

Low ESR ceramic capacitors are recommended for input capacitor applications. A low ESR effectively reduces the input voltage ripple caused by the switching operation. A capacitance of  $10\mu$ F is sufficient for most applications. However, this value can be reduced for applications with lower output current requirements. Another important consideration is that the voltage rating of the input capacitor must exceed the maximum input voltage.

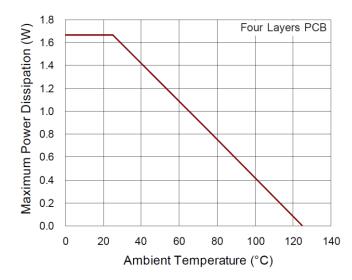

#### 15.11 Thermal Considerations

The junction temperature should never exceed the absolute maximum junction temperature T<sub>J(MAX)</sub>, listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

#### $\mathsf{P}\mathsf{D}(\mathsf{M}\mathsf{A}\mathsf{X}) = \big(\mathsf{T}\mathsf{J}(\mathsf{M}\mathsf{A}\mathsf{X}) - \mathsf{T}\mathsf{A}\big) \; / \; \theta \mathsf{J}\mathsf{A}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WDFN-10L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 60°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at TA = 25°C can be calculated as below:

$\mathsf{P}\mathsf{D}(\mathsf{MAX})$  = (125°C - 25°C) / (60°C/W) = 1.667W for a WDFN-10L 3x3 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curve in <u>Figure 2</u> allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 2. Derating Curve of Maximum Power Dissipation

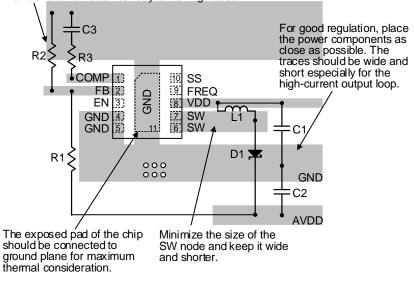

#### 15.12 Layout Considerations

For high-frequency switching power supplies, PCB layout plays a crucial role in achieving good regulation, high efficiency, and stability. The guidelines provided below are intended to assist in optimizing the PCB layout.

- For optimal regulation, position the power components as close together as possible. Ensure that the traces are both wide and short, particularly for the high-current output loop.

- Place the feedback voltage divider resistors close to the feedback pin. Keep the trace connecting to the center of the divider short and ensure it is isolated from any switching nodes to prevent noise interference.

- The compensation circuit should be placed at a distance from the power loops and shielded with a ground trace to avoid noise coupling.

- Minimize the area of the SW node and ensure that it is wide and short. Additionally, maintain a distance between the SW node and the FB pin to prevent interference.

- Connect the exposed pad of the chip to a robust ground plane to ensure optimal thermal management.

The feedback voltage divider resistors must be near the feedback pin. The divider center trace and compensation components must be shorter and avoid the trace near any switching nodes.

Figure 3. PCB Layout Guide

Note 6. The information provided in this section is for reference only. The customer is solely responsible for designing, validating, and testing any applications incorporating Richtek's product(s). The customer is also responsible for applicable standards and any safety, security, or other requirements.

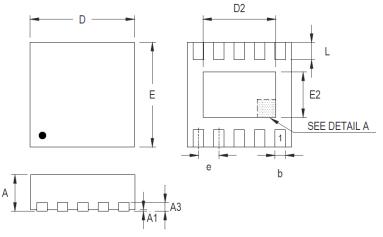

### **16 Outline Dimension**

DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | n Millimeters | <b>Dimensions In Inches</b> |       |  |  |

|--------|--------------|---------------|-----------------------------|-------|--|--|

| Symbol | Min          | Max           | Min                         | Max   |  |  |

| А      | 0.700        | 0.800         | 0.028                       | 0.031 |  |  |

| A1     | 0.000        | 0.050         | 0.000                       | 0.002 |  |  |

| A3     | 0.175        | 0.250         | 0.007                       | 0.010 |  |  |

| b      | 0.180        | 0.300         | 0.007                       | 0.012 |  |  |

| D      | 2.950        | 3.050         | 0.116                       | 0.120 |  |  |

| D2     | 2.300        | 2.650         | 0.091                       | 0.104 |  |  |

| E      | 2.950        | 3.050         | 0.116                       | 0.120 |  |  |

| E2     | 1.500        | 1.750         | 0.059                       | 0.069 |  |  |

| е      | 0.5          | 500           | 0.020                       |       |  |  |

| L      | 0.350        | 0.450         | 0.014                       | 0.018 |  |  |

W-Type 10L DFN 3x3 Package

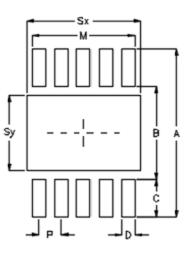

## **17 Footprint Information**

| Dookogo            | Number of | Footprint Dimension (mm) |      |      |      |      |      |      |      | Talaranaa |

|--------------------|-----------|--------------------------|------|------|------|------|------|------|------|-----------|

| Package            | Pin       | Р                        | А    | В    | С    | D    | Sx   | Sy   | М    | Tolerance |

| V/W/U/X/ZDFN3*3-10 | 10        | 0.50                     | 3.80 | 2.10 | 0.85 | 0.30 | 2.55 | 1.70 | 2.30 | ±0.05     |

### **18 Packing Information**

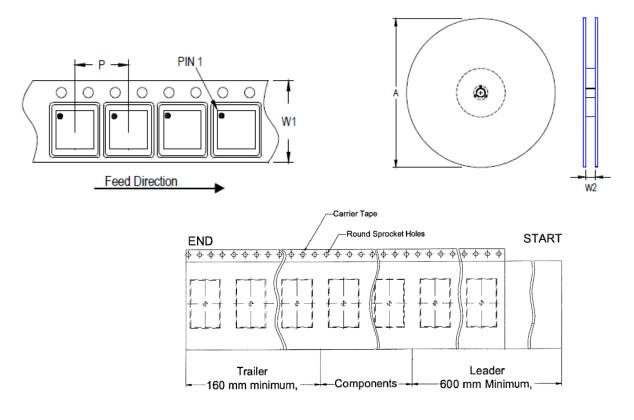

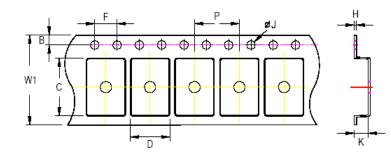

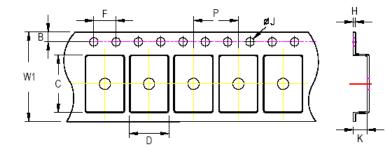

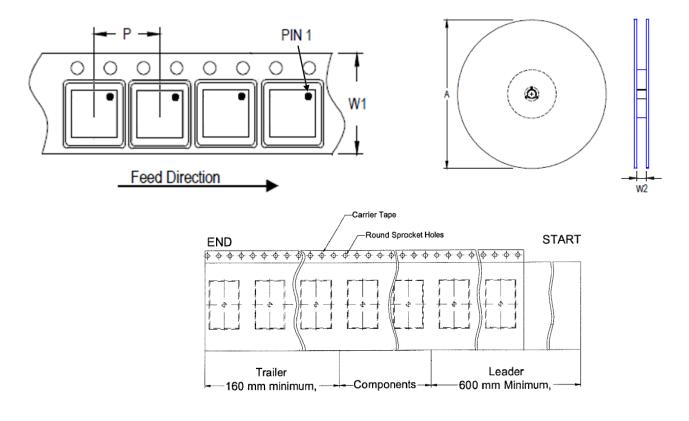

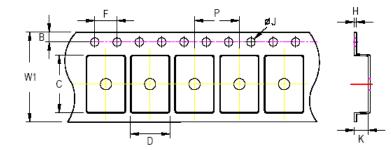

- 18.1 **Tape and Reel Data**

- Pin 1 at Quadrant 1 for 7" 18.1.1

| Package Type             | Tape Size | Pocket Pitch | Reel Size (A) |   | Units    | Trailer | Leader | Reel Width (W2) |

|--------------------------|-----------|--------------|---------------|---|----------|---------|--------|-----------------|

|                          | (W1) (mm) | (P) (mm)     | (mm) (in)     |   | per Reel | (mm)    | (mm)   | Min./Max. (mm)  |

| (V, W)<br>QFN/DFN<br>3x3 | 12        | 8            | 180           | 7 | 1,500    | 160     | 600    | 12.4/14.4       |

C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | Р     |       | В      |        | F     |       | ØJ    |       | К     |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

|           | Max    | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.3mm | 0.6mm |

18.1.2 Pin 1 at Quadrant 1 for 13"

| Package Type          | Tape Size | Pocket Pitch | Reel Size (A) |      | Units    | Trailer<br>(mm) | Leader<br>(mm) | Reel Width (W2) |  |

|-----------------------|-----------|--------------|---------------|------|----------|-----------------|----------------|-----------------|--|

|                       | (W1) (mm) | (P) (mm)     | (mm)          | (in) | per Reel | ()              | ()             | Min./Max. (mm)  |  |

| (V, W)<br>QFN/DFN 3x3 | 12        | 8            | 330           | 13   | 2,500    | 160             | 600            | 12.4/14.4       |  |

C, D, and K are determined by component size.

The clearance between the components and the cavity is as follows:

For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | Р     |       | В      |        | F     |       | ØJ    |       | К     |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max    | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.3mm | 0.6mm |

**RT9297**

#### 18.1.3 Pin 1 at Quadrant 2 for 7"

| Package Type             | Tape Size | Pocket Pitch | Reel Si | ze (A) | Units    | Trailer | Leader | Reel Width (W2) |  |

|--------------------------|-----------|--------------|---------|--------|----------|---------|--------|-----------------|--|

| r dokage rype            | (W1) (mm) | (P) (mm)     | (mm)    | (in)   | per Reel | (mm)    | (mm)   | Min./Max. (mm)  |  |

| (V, W)<br>QFN/DFN<br>3x3 | 12        | 8            | 180     | 7      | 1,500    | 160     | 600    | 12.4/14.4       |  |

C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | Р     |       | В      |        | F     |       | ØJ    |       | К     |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max    | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.3mm | 0.6mm |

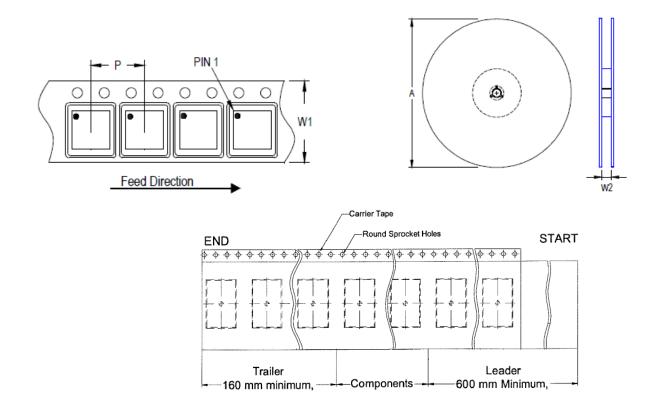

#### 18.2 **Tape and Reel Packing**

#### Pin 1 at Quadrant 1 for 7" 18.2.1

| Step | Photo/Description                      | Step | Photo/Description                  |

|------|----------------------------------------|------|------------------------------------|

| 1    | Reel 7"                                | 4    | 3 reels per inner box <b>Box A</b> |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box       |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                 |

| Container   | Reel |       |       | Box   |       | Carton   |                     |        |  |

|-------------|------|-------|-------|-------|-------|----------|---------------------|--------|--|

| Package     | Size | Units | Item  | Reels | Units | Item     | Boxes               | Unit   |  |

| (V, W)      |      | 4 500 | Box A | 3     | 4,500 | Carton A | 12                  | 54,000 |  |

| QFN/DFN 3x3 | 1    | 1,500 | Box E | 1     | 1,500 | For Co   | mbined or Partial I | Reel.  |  |

#### 18.2.2 Pin 1 at Quadrant 1 for 13"

| Step | Photo/Description                      | Step | Photo/Description                 |

|------|----------------------------------------|------|-----------------------------------|

| 1    | Reel 13"                               | 4    | 1 reel per inner box <b>Box G</b> |

| 2    | HIC & Desiccant (2 Unit) inside        | 5    | 6 inner boxes per outer box       |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                |

| Container              | R    | eel   |       | Box   |       | Carton   |       |        |  |

|------------------------|------|-------|-------|-------|-------|----------|-------|--------|--|

| Package                | Size | Units | Item  | Reels | Units | Item     | Boxes | Units  |  |

| (V, W) QFN and DFN 3x3 | 13"  | 2,500 | Box G | 1     | 2,500 | Carton A | 6     | 15,000 |  |

#### 18.2.3 Pin 1 at Quadrant 2 for 7"

| Step | Photo/Description                      | Step | Photo/Description                  |

|------|----------------------------------------|------|------------------------------------|

| 1    |                                        | 4    |                                    |

|      | Reel 7"                                |      | 3 reels per inner box <b>Box A</b> |

| 2    |                                        | 5    |                                    |

|      | HIC & Desiccant (1 Unit) inside        |      | 12 inner boxes per outer box       |

| 3    |                                        | 6    |                                    |

|      | Caution label is on backside of Al bag |      | Outer box Carton A                 |

| Container   | Reel |       |       | Box   |       | Carton   |                     |        |  |

|-------------|------|-------|-------|-------|-------|----------|---------------------|--------|--|

| Package     | Size | Units | Item  | Reels | Units | Item     | Boxes               | Unit   |  |

| (V, W)      |      | 4 500 | Box A | 3     | 4,500 | Carton A | 12                  | 54,000 |  |

| QFN/DFN 3x3 | 1    | 1,500 | Box E | 1     | 1,500 | For C    | combined or Partial | Reel.  |  |

#### 18.3 Packing Material Anti-ESD Property

| Surface<br>Resistance | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|-----------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega/cm^2$         | 10 <sup>4</sup> to 10 <sup>11</sup> |

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

### **19 Datasheet Revision History**

| Version | Date       | Description | Item                                                                                                                                                                                                                                                                                                |

|---------|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04      | 2024/11/28 | Modify      | Changed the names of pin 6 and pin 7 to SW.<br>General Description on page 1<br>-Added Temperature range<br>Ordering Information on page 1<br>-Added note<br>Footprint Information on page 16<br>-Added footprint information<br>Packing Information on page 17 to 23<br>-Added packing information |

www.richtek.com