# **RT9080**

# 2μA IQ, 600mA Low-Dropout Linear Voltage Regulator

# 1 General Description

The RT9080 series is a low-dropout (LDO) linear voltage regulator featuring an enable function, operating over a wide input voltage range from 1.2V to 5.5V. The RT9080 delivers a maximum output current of 600mA and is designed for low-power operation, all within a compact package.

The features of low quiescent current, as low as  $2\mu A$ , and almost zero disable current, are ideal for powering battery equipment for a longer service life. The RT9080 series is stable with the ceramic output capacitor over its wide input range from 1.2V to 5.5V and the entire range of output load current (0mA to 600mA). The recommended junction temperature range is  $-40^{\circ} C$  to  $125^{\circ} C$ , and the ambient temperature range is  $-40^{\circ} C$  to  $85^{\circ} C$ .

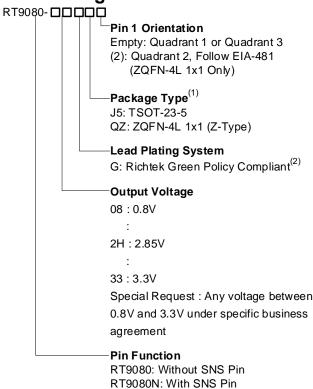

# 2 Ordering Information

#### Note 1.

DS9080-09

- Marked with <sup>(1)</sup> indicated: Compatible with the current requirements of IPC/JEDEC J-STD-020.

- Marked with <sup>(2)</sup> indicated: Richtek products are Richtek Green Policy compliant.

### 3 Features

- 2μA Quiescent Current at No Load

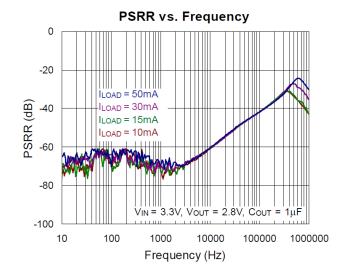

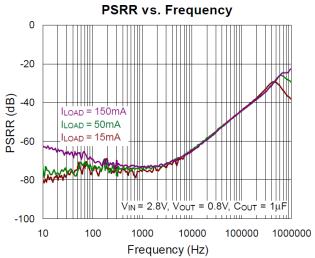

- PSRR = 75dB at 1kHz

- Adjustable Output Voltage Available for Specific Applications

- ±2% Output Accuracy

- 600mA (V<sub>IN</sub> ≥ 2.3V) Output Current

- Low (0.1μA) Disable Current

- Operating Input Voltage: 1.2V to 5.5V

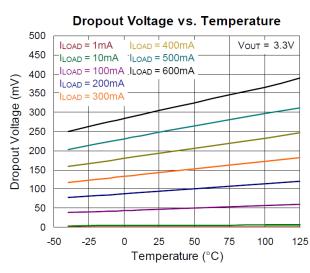

- Dropout Voltage: 0.31V at 600mA when VouT ≥ 3V

- Support Fixed Output Voltage: 0.8V to 3.3V

- Stable with Ceramic or Tantalum Capacitor

- Current-Limit Protection

- Over-Temperature Protection

- Available in TSOT-23-5 and ZQFN-4L 1x1 (ZDFN-4L 1x1) Packages

## 4 Applications

- · Portable, Battery Powered Equipment

- Ultra Low Power Microcontrollers

- Notebook Computers

# 5 Marking Information

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

RICHTEK

December 2024

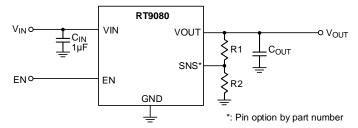

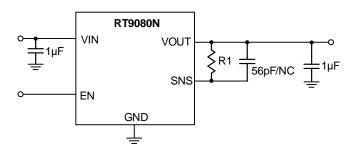

# 6 Simplified Application Circuit

# **Table of Contents**

| 1  |       | ral Description                |   |

|----|-------|--------------------------------|---|

| 2  | Order | ing Information 1              | ı |

| 3  |       | res                            |   |

| 4  |       | cations 1                      |   |

| 5  |       | ng Information1                |   |

| 6  |       | ified Application Circuit2     |   |

| 7  |       | onfiguration 4                 |   |

| 8  | Funct | ional Pin Description          | ļ |

| 9  | Funct | ional Block Diagram            | ļ |

| 10 | Abso  | ute Maximum Ratings 5          | 5 |

| 11 |       | Ratings 5                      |   |

| 12 |       | nmended Operating Conditions 5 |   |

| 13 |       | nal Information 5              |   |

| 14 |       | rical Characteristics6         |   |

| 15 | Typic | al Application Circuit7        | 7 |

| 16 |       | al Operating Characteristics   |   |

| 17 | Opera | ition12                        |   |

|    | 17.1  | Basic Operation12              |   |

|    | 17.2  | Pass Transistor12              |   |

|    | 17.3  | Error Amplifier12              |   |

|    | 17.4  | Chip Enable and Shutdown12     |   |

|    | 17.5  | Current-Limit Protection12     |   |

|    | 17.6  | Over-Temperature Protection12  | 2 |

|    | 17.7  | Output Active Discharge12      | 2 |

| 18 | Appli  | cation Information                 | 13 |

|----|--------|------------------------------------|----|

|    | 18.1   | Enable                             | 13 |

|    | 18.2   | Adjustable Output Voltage Setting  | 13 |

|    | 18.3   | Current Limit                      |    |

|    | 18.4   | Thermal Considerations             | 14 |

|    | 18.5   | Layout Considerations              | 15 |

| 19 | Outlir | ne Dimension                       | 17 |

|    | 19.1   | TSOT-23-5                          | 17 |

|    | 19.2   | ZQFN-4L 1x1 Package                |    |

| 20 | Footp  | rint Information                   | 19 |

|    | 20.1   | TSOT-23-5 Package                  | 19 |

|    | 20.2   | ZQFN-4L 1x1 Package                | 20 |

| 21 | Packi  | ng Information                     |    |

|    | 21.1   | Tape and Reel Data                 | 21 |

|    | 21.2   | Tape and Reel Packing              | 24 |

|    | 21.3   | Packing Material Anti-ESD Property | 27 |

| 22 | Datas  | heet Revision History              | 28 |

|    |        |                                    |    |

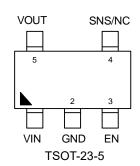

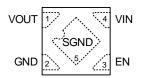

# 7 Pin Configuration

(TOP VIEW)

ZQFN-4L 1x1 (ZDFN-4L 1x1)

# 8 Functional Pin Description

| Pir       | No.                          |          |                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TSOT-23-5 | ZQFN-4L 1x1<br>(ZDFN-4L 1x1) | Pin Name | Pin Function                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 1         | 4                            | VIN      | Supply input. A general $1\mu F$ ceramic capacitor should be placed as close as possible to this pin for better noise rejection.                                                                                                                         |  |  |  |  |  |  |

| 2         | 2                            | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                              |  |  |  |  |  |  |

| 3         | 3                            | 1EN      | Enable control input. Connect this pin to logic-high to enable the regulator. Pull this pin below 0.4V to turn the regulator off, reducing the quiescent current to a fraction of its operating value.                                                   |  |  |  |  |  |  |

|           |                              | SNS      | Output voltage sense pin for RT9080N only. This pin is used to set the desired output voltage via an external resistive divider. The SNS pin voltage is 0.8V typically.                                                                                  |  |  |  |  |  |  |

| 4         | ł                            | NC       | No internal connection. Leaving this pin floating does not affect the functionality of the device. By connecting this pin to GND, design engineers can extend the GND copper coverage on the PCB top layer to enhance the thermal convection.            |  |  |  |  |  |  |

| 5         | 1                            | VOUT     | LDO output pin. A $1\mu F$ or larger ceramic capacitor ( $0.7\mu F$ or greater effective capacitance) is required for stability. Place the output capacitor as close to the device as possible and minimize the impedance between the VOUT pin and load. |  |  |  |  |  |  |

|           | 5 (Exposed Pad)              | SGND     | Substrate of the IC. Connect to the GND plane for maximum thermal dissipation.                                                                                                                                                                           |  |  |  |  |  |  |

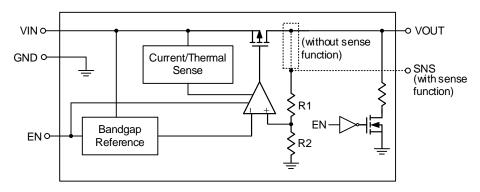

# 9 Functional Block Diagram

DS9080-09

## 10 Absolute Maximum Ratings

#### (Note 2)

| • VIN, VOUT, SNS, EN to GND           | -0.3V to 6.5V  |

|---------------------------------------|----------------|

| • VOUT to VIN                         | -6.5V to 0.3V  |

| Lead Temperature (Soldering, 10 sec.) | 260°C          |

| Junction Temperature                  | 150°C          |

| Storage Temperature Range             | -65°C to 150°C |

**Note 2.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

## 11 ESD Ratings

#### (Note 3)

ESD Susceptibility

HBM (Human Body Model)------ 2kV

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

# 12 Recommended Operating Conditions

### (Note 4)

Note 4. The device is not guaranteed to function outside its operating conditions.

### 13 Thermal Information

#### (Note 5 and Note 6)

|                     | Thermal Parameter                                       | TSOT-23-5 | ZQFN-4L 1x1<br>(ZDFN-4L 1x1) | Unit |

|---------------------|---------------------------------------------------------|-----------|------------------------------|------|

| θЈА                 | Junction-to-ambient thermal resistance (JEDEC standard) | 189.4     | 291.4                        | °C/W |

| θJC(Top)            | Junction-to-case (top) thermal resistance               | 75.9      | 163                          | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 55.8      | 90.7                         | °C/W |

| $\theta$ JA(EVB)    | Junction-to-ambient thermal resistance (specific EVB)   | 100.7     | 236                          | °C/W |

| ΨJC(Top)            | Junction-to-top characterization parameter              | 21.6      | 52.3                         | °C/W |

| ΨЈВ                 | Junction-to-board characterization parameter            | 67.2      | 189.1                        | °C/W |

**Note 5.** For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

Note 6.  $\theta_{JA \, (EVB)}$ ,  $\Psi_{JC (Top)}$ , and  $\Psi_{JB}$  are measured on a high effective-thermal-conductivity four-layer test board which is in size of 70mm x 50mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

Copyright © 2024 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# 14 Electrical Characteristics

(VVOUT + 1 <  $V_{IN}$  < 5.5V,  $T_A$  = 25 $^{\circ}$ C, unless otherwise specified.)

| Parameter                                            | Symbol             | Test                               | Condi                     | tions                           | Min | Тур  | Max  | Unit  |  |

|------------------------------------------------------|--------------------|------------------------------------|---------------------------|---------------------------------|-----|------|------|-------|--|

| Output Voltage                                       | Vvout              |                                    |                           |                                 | 0.8 |      | 3.3  | V     |  |

| Output Voltage Accuracy                              | Vvout_acc          | ILOAD = 1mA                        |                           |                                 | -2  |      | 2    | %     |  |

| SNS Reference Voltage<br>(for RT9080N-08GJ5<br>only) | VREF               | ILOAD = 1mA                        |                           |                                 |     | 0.8  |      | V     |  |

|                                                      |                    | $0.8V \leq V_{VOUT} <$             | 1.05V                     | (TSOT-23-5)                     |     | 1.05 | 1.33 |       |  |

|                                                      |                    | $0.8V \le VVOUT <$                 | 1.05V                     | (ZQFN-4L 1x1)                   |     | 1.05 | 1.63 |       |  |

|                                                      |                    | 1.05V ≤ VVOUT <                    | < 1.2V                    |                                 |     | 8.0  | 1.13 |       |  |

| Dropout Voltage                                      |                    | 1.2V ≤ V <sub>V</sub> OUT <        | 1.5V                      |                                 |     | 0.71 | 1.03 |       |  |

| (ILOAD = 600mA)                                      | VDROP              | 1.5V ≤ VVOUT <                     | 1.8V                      |                                 |     | 0.57 | 0.93 | V     |  |

| ( <u>Note 7</u> )                                    |                    | $1.8V \le VVOUT <$                 | 2.1V                      |                                 |     | 0.57 | 0.83 |       |  |

|                                                      |                    | 2.1V ≤ V <sub>V</sub> OUT <        | 2.5V                      |                                 |     | 0.41 | 0.73 |       |  |

|                                                      |                    | 2.5V ≤ VVOUT <                     | 3V                        |                                 |     | 0.36 | 0.63 |       |  |

|                                                      |                    | 3V ≤ VVOUT                         |                           |                                 |     | 0.31 | 0.53 |       |  |

| Quiescent Current                                    | lq                 | ILOAD = 0mA, V\<br>VVIN ≥ VVOUT +  |                           | 2                               | 4   | μА   |      |       |  |

| Shutdown GND Current                                 |                    | VEN = 0V                           |                           |                                 |     | 0.1  | 0.5  | μΑ    |  |

| ( <u>Note 8</u> )                                    | ISHDN              | VEN = 0V, VVOU                     |                           | 0.1                             | 0.5 | μΑ   |      |       |  |

| EN Input Current                                     | len                | VEN = 5.5V                         |                           |                                 |     |      | 0.1  | μА    |  |

| ·                                                    | VLINE_REG          |                                    | 1.2V                      | ≤ VVIN < 1.5V                   |     | 0.3  | 0.6  |       |  |

| Line Regulation                                      |                    | I <sub>LOAD</sub> = 1mA            | $1.5V \le V_{VIN} < 1.8V$ |                                 |     | 0.15 | 0.3  | %     |  |

|                                                      |                    |                                    | 1.8V                      | $1.8V \leq V \text{VIN} < 5.5V$ |     | 0.13 | 0.35 |       |  |

| Load Regulation                                      | VLOAD_REG          | 1mA < ILOAD < 6                    | 00mA                      |                                 |     | 0.5  | 1    | %     |  |

| Power Supply Rejection<br>Ratio                      | PSRR               | VVIN = 3V, ILOAE<br>COUT = 1μF, VV |                           |                                 |     | 75   |      | dB    |  |

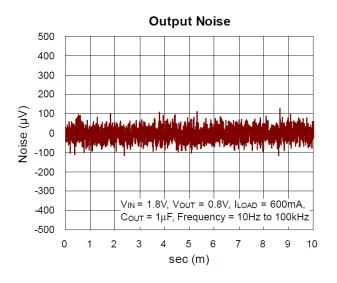

|                                                      |                    | C <sub>OUT</sub> = 1μF,            |                           | VVOUT = 0.8V                    |     | 26   |      |       |  |

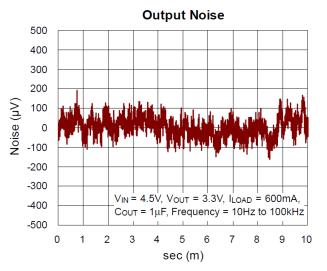

| Output Voltage Naise                                 |                    | ILOAD = 150mA,                     |                           | VVOUT = 1.2V                    |     | 37   |      | μVRMS |  |

| Output Voltage Noise                                 | Vn                 | BW = 10Hz to<br>100kHz,            |                           | VVOUT = 1.8V                    |     | 39   |      |       |  |

|                                                      |                    | VVIN = VVOUT +                     | 1V                        | V <sub>VOUT</sub> = 3.3V        |     | 42   |      |       |  |

| Current Limit                                        | ILIM               | VVOUT = 90%VC                      | OUT(Nor                   | mal)                            | 610 | 1100 |      | mA    |  |

| EN Input Voltage Rising Threshold                    | VEN_R              | VVIN = 5V                          |                           |                                 | 0.9 |      |      | V     |  |

| EN Input Voltage Falling Threshold                   | V <sub>EN_</sub> F | V <sub>VIN</sub> = 5V              |                           |                                 |     | 0.4  | V    |       |  |

| Over-Temperature<br>Protection Threshold             | Тотр               | ILOAD = 30mA, \                    | /VIN ≥                    | 1.5V                            |     | 150  | 1    | °C    |  |

| Over-Temperature<br>Protection Hysteresis            | TOTP_HYS           |                                    |                           |                                 |     | 20   |      | °C    |  |

| Discharge Resistor                                   | RDISCHG            | EN = 0V, Vvout                     | = 0.1                     | V                               |     | 80   | -    | Ω     |  |

Note 7. The dropout voltage is defined as  $V_{VIN} - V_{VOUT}$  when  $V_{VOUT}$  is 98% of the normal value of  $V_{VOUT}$ .

Note 8. The specification is tested at wafer stage and guaranteed by design after assembly.

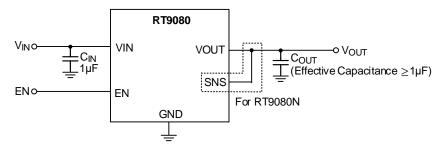

# 15 Typical Application Circuit

Figure 1. Application with Sense Function (RT9080) / without Sense Function (RT9080N)

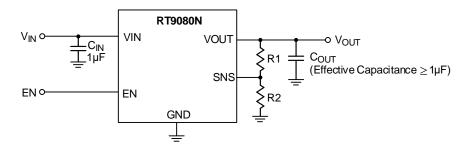

Figure 2. Adjustable Output Voltage Application Circuit

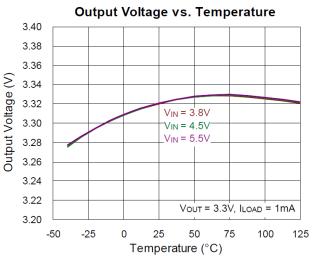

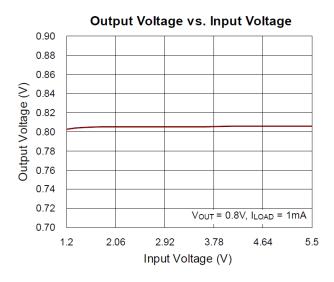

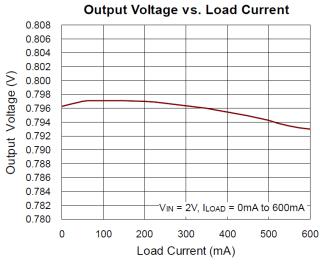

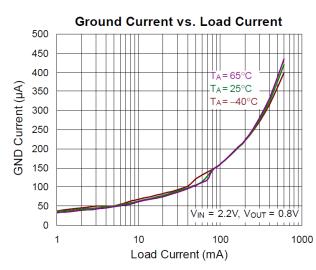

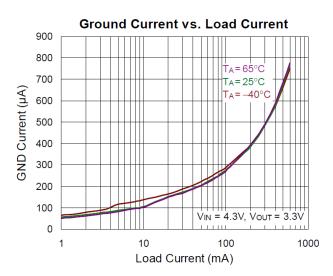

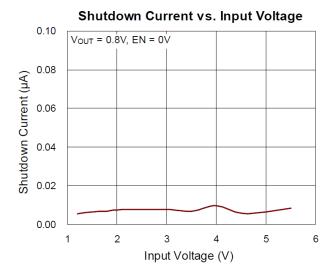

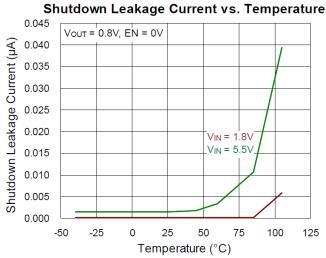

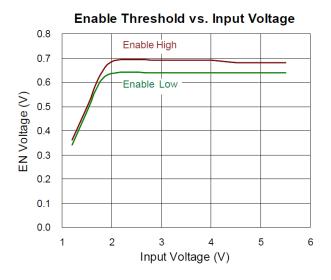

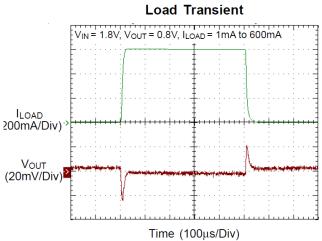

# 16 Typical Operating Characteristics

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9080-09

www.richtek.com

2024

DS9080-09

## 17 Operation

#### 17.1 Basic Operation

The RT9080 series is a low quiescent current linear voltage regulator designed especially for systems with few external components. The input voltage range is from 1.2V to 5.5V. The minimum output capacitance required for stable operation is  $1\mu$ F, considering the temperature and voltage coefficient of the capacitor.

#### 17.2 Pass Transistor

The RT9080 series builds in a P-MOSFET output transistor, which provides low switch-on resistance for low dropout voltage applications.

#### 17.3 Error Amplifier

The Error Amplifier compares the internal reference voltage with the output feedback voltage from the internal divider, and controls the Gate voltage of the P-MOSFET to support good line regulation and load regulation at the output voltage.

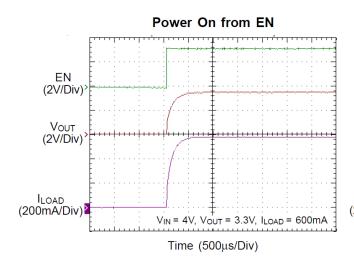

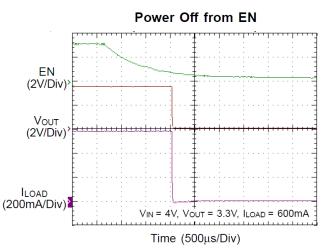

#### 17.4 Chip Enable and Shutdown

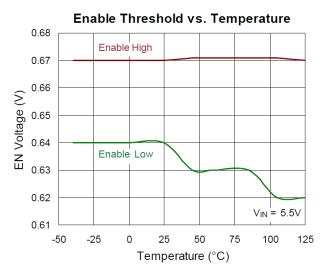

The RT9080 series provides an EN pin, which serves as an external chip enable control, to enable or disable the device. A VEN below 0.4V turns the regulator off and enters shutdown mode, while a VEN above 0.9V turns the regulator on. When the regulator is in shutdown mode, the ground current is reduced to a maximum of  $0.5\mu$ A.

#### 17.5 Current-Limit Protection

The RT9080 series provides a current-limit function to prevent the device from being damaged during overload or short-circuit conditions. This current is detected by an internal sensing transistor.

#### 17.6 Over-Temperature Protection

The over-temperature protection function will turn off the P-MOSFET when the junction temperature exceeds 150°C (typical), and the output current exceeds 30mA. Once the junction temperature cools down by approximately 20°C, the regulator will automatically resume operation.

#### 17.7 Output Active Discharge

When the RT9080 series is operating in shutdown mode, the device has an internal active pull-down circuit that connects the output to GND through a resistor for discharging purpose.

## 18 Application Information

#### (Note 9)

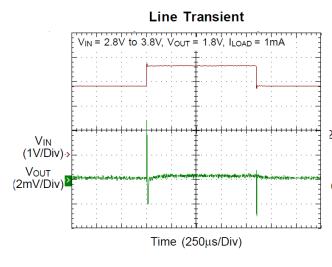

Like any low dropout linear voltage regulator, the RT9080's external input and output capacitors must be properly selected for stability and performance. Use a  $1\mu F$  or larger input capacitor and place it close to the IC's VIN and GND pins. Any output capacitor meeting the minimum  $1m\Omega$  ESR (Equivalent Series Resistance) requirement and having a capacitance larger than  $1\mu F$  may be used. Place the output capacitor close to the IC's VOUT and GND pins. Increasing capacitance and decreasing ESR can improve the circuit's PSRR and line transient response.

#### 18.1 Enable

The RT9080 series has an EN pin to turn on or turn off the regulator. When the EN pin is in logic-high, the regulator will be turned on. The shutdown current is almost 0µA typical. The EN pin may be directly tied to VIN to keep the part on. The Enable input is CMOS logic and should not be left floating.

#### 18.2 Adjustable Output Voltage Setting

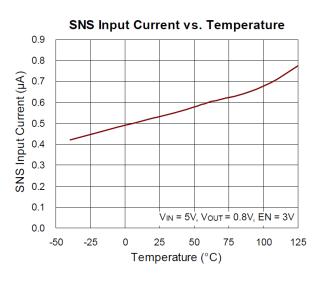

Because of the small input current at the SNS pin, the RT9080N with the SNS pin can also work as an adjustable output voltage LDO. <u>Figure 2</u> gives the connections for the adjustable output voltage application. The resistor divider from VOUT to SNS sets the output voltage when in regulation.

The voltage on the SNS pin sets the output voltage and is determined by the values of R1 and R2. To maintain a good temperature coefficient of the output voltage, the values of R1 and R2 should be selected with consideration for the temperature coefficient of the input current at the SNS pin. A current greater than  $50\mu$ A in the resistor divider is recommended to meet the above requirement. The adjustable output voltage can be calculated using the formula provided in Equation 1:

$$V_{OUT} = \frac{R1 + R2}{R2} \times V_{SNS} \tag{1}$$

where VSNS is determined by the output voltage options listed in the ordering information for the RT9080N. The maximum adjustable output voltage can be as high as the input voltage minus the dropout voltage.

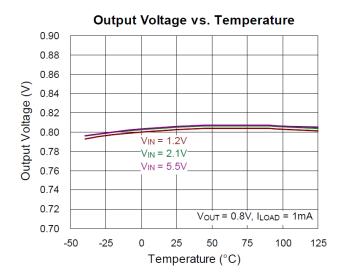

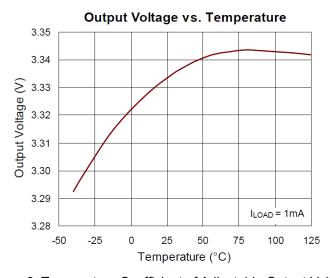

When we choose  $51k\Omega$  and  $16k\Omega$  as R1 and R2, respectively, and select a 0.8V output at the SNS pin, the adjustable output voltage will be approximately 3.35V. The temperature coefficient, as shown in <u>Figure 4</u>, remains excellent for this type of application.

Figure 3. Temperature Coefficient of Adjustable Output Voltage

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

The minimum recommended current of  $50\mu A$  in the resistor divider makes the application no longer an ultra-low quiescent LDO. Figure 4 presents another fine adjustable output voltage application that allow the LDO to continue operating with low power consumption. The fine-tuning range is recommended to be less than 50mV (R1  $\leq$   $91k\Omega$ ) to maintain a good temperature coefficient of the output voltage.

Figure 4. Fine Adjustable Output Voltage Application Circuit

There is no additional current consumption in the above application. However, the temperature coefficient of the output voltage will be degraded by the input current at the SNS pin. If the tuning range is larger than 50mV, a compensation capacitor (56pF) is required to maintain the stability of the output voltage. The fine adjustable output voltage can be calculated using the formula provided in Equation 2:

$$V_{OUT} = V_{SNS} + I_{SNS} \times R1$$

(2)

where Isns is the input current at the SNS pin (typically 550nA at room temperature) and Vsns is determined by the output voltage options listed in the ordering information for the RT9080N.

#### 18.3 Current Limit

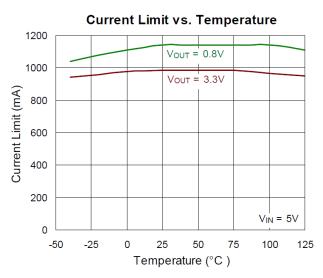

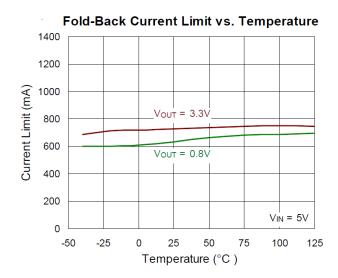

The RT9080 series features an independent current limiter that monitors and controls the gate voltage of the pass transistor, limiting the output current to 1.1A (typical). When the output voltage decreases further, the current limiting level is reduced to around 0.6A, which is named fold-back current limit. This allows the output to be shorted to ground indefinitely without damaging the device.

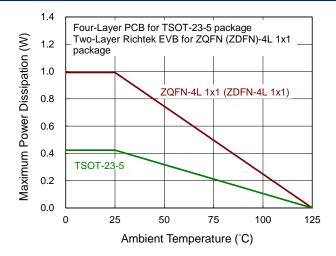

#### 18.4 Thermal Considerations

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$PD(MAX) = (TJ(MAX) - TA) / \theta JA$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C and TA is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA(EVB)}$ , is highly package dependent. For TSOT-23-5 package, the thermal resistance,  $\theta_{JA(EVB)}$ , is 100.7°C/W on a standard JEDEC 51-7 four-layer thermal test board. For ZQFN-4L 1x1 (ZDFN-4L 1x1) package, the thermal resistance,  $\theta_{JA(EVB)}$ , is 236°C/W on a two-layer Richtek evaluation board. The maximum power dissipation at TA = 25°C can be calculated by the following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (100.7^{\circ}C/W) = 0.99W$$

for TSOT-23-5 package

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (236^{\circ}C/W) = 0.42W$$

for ZQFN-4L 1x1 (ZDFN-4L 1x1) package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA(EVB)}$ . The derating curves in <u>Figure 5</u> allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 5. Derating Curves of Maximum Power Dissipation

## 18.5 Layout Considerations

For best performance of the RT9080 series, the PCB layout suggestions below are highly recommended:

- Input capacitor must be placed as close as possible to the IC to minimize the power loop area.

- Minimize the power trace length and avoid using vias for the input and output capacitors connections.

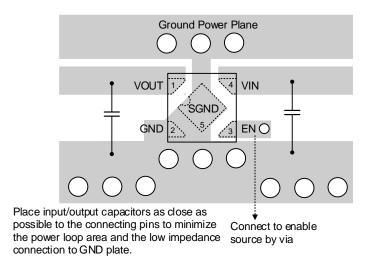

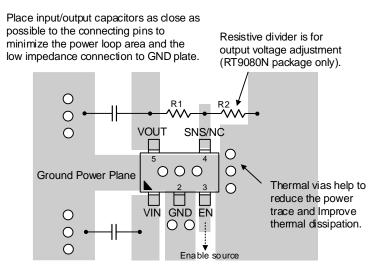

Figure 6 and Figure 7 show the layout examples that help minimize inductive parasitic components, reduce load transients, and ensure good circuit stability.

Figure 6. PCB Layout Guide for ZQFN-4L 1x1 Package

Figure 7. PCB Layout Guide for TSOT-23-5 Package

Note 9. The information provided in this section is for reference only. The customer is solely responsible for the designing, validating, and testing your product incorporating Richtek's product and ensure such product meets applicable standards and any safety, security, or other requirements.

DS9080-09

# **19 Outline Dimension**

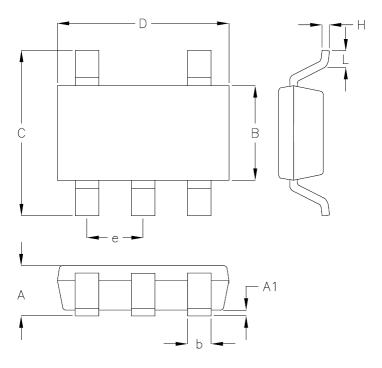

### 19.1 TSOT-23-5

| Sumbal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |  |  |

|--------|--------------|---------------|----------------------|-------|--|--|--|

| Symbol | Min          | Max           | Min                  | Max   |  |  |  |

| А      | 0.700        | 1.000         | 0.028                | 0.039 |  |  |  |

| A1     | 0.000        | 0.100         | 0.000                | 0.004 |  |  |  |

| В      | 1.397        | 1.803         | 0.055                | 0.071 |  |  |  |

| b      | 0.300        | 0.559         | 0.012                | 0.022 |  |  |  |

| С      | 2.591        | 3.000         | 0.102                | 0.118 |  |  |  |

| D      | 2.692        | 3.099         | 0.106                | 0.122 |  |  |  |

| е      | 0.838        | 1.041         | 0.033                | 0.041 |  |  |  |

| Н      | 0.080        | 0.254         | 0.003                | 0.010 |  |  |  |

| L      | L 0.300      |               | 0.012                | 0.024 |  |  |  |

**TSOT-23-5 Surface Mount Package**

## 19.2 ZQFN-4L 1x1 Package

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | n Millimeters | Dimension | s In Inches |

|--------|--------------|---------------|-----------|-------------|

|        | Min          | Max           | Min       | Max         |

| А      | 0.300        | 0.400         | 0.012     | 0.016       |

| A1     | 0.000        | 0.050         | 0.000     | 0.002       |

| А3     | 0.117        | 0.162         | 0.005     | 0.006       |

| b      | 0.175        | 0.275         | 0.007     | 0.011       |

| D      | 0.900        | 1.100         | 0.035     | 0.043       |

| D2     | 0.450        | 0.550         | 0.018     | 0.022       |

| Е      | 0.900        | 1.100         | 0.035     | 0.043       |

| E2     | 0.450        | 0.550         | 0.018     | 0.022       |

| е      | 0.625        |               | 0.025     |             |

| L      | 0.200        | 0.300         | 0.008     | 0.012       |

| Н      | 0.039        |               | 0.002     |             |

| H1     | 0.064        |               | 0.003     |             |

Z-Type 4L QFN 1x1 Package

December 2024

# 20 Footprint Information

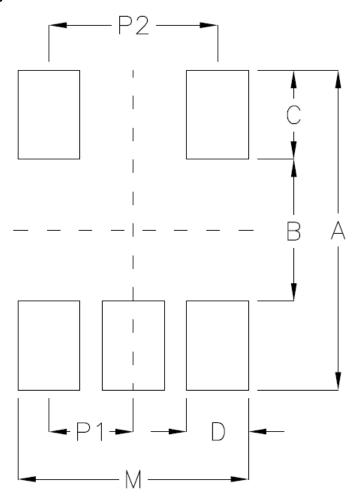

## 20.1 TSOT-23-5 Package

| Dockogo                    | Number |      | Toloropoo |      |      |      |      |      |           |

|----------------------------|--------|------|-----------|------|------|------|------|------|-----------|

| Package                    | of Pin | P1   | P2        | Α    | В    | С    | D    | М    | Tolerance |

| TSOT-25/TSOT-25(FC)/SOT-25 | 5      | 0.95 | 1.90      | 3.60 | 1.60 | 1.00 | 0.70 | 2.60 | ±0.10     |

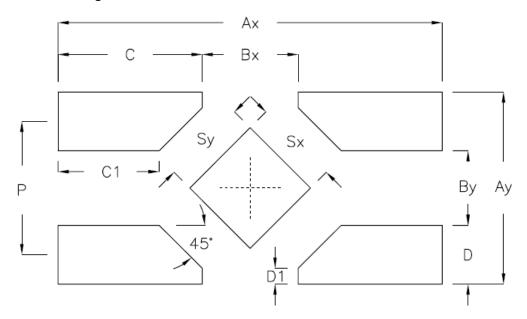

# 20.2 ZQFN-4L 1x1 Package

| Package       | Number |       | Footprint Dimension (mm) |       |       |       |       |       |       |       |       |       | Tolerance |

|---------------|--------|-------|--------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|

| rackage       | of Pin | Р     | Ax                       | Ау    | Вх    | Ву    | С     | C1    | D     | D1    | Sx    | Sy    | Tolerance |

| U/X/ZQFN1x1-4 | 4      | 0.625 | 1.800                    | 0.900 | 0.450 | 0.350 | 0.675 | 0.474 | 0.275 | 0.074 | 0.400 | 0.400 | ±0.050    |

# 21 Packing Information

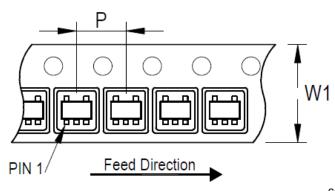

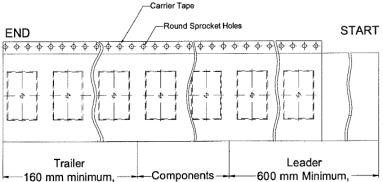

### 21.1 Tape and Reel Data

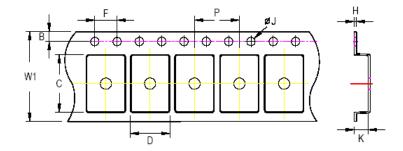

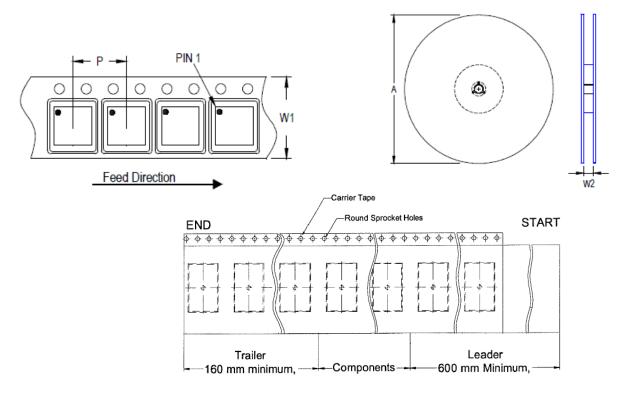

#### 21.1.1 TSOT-23-5

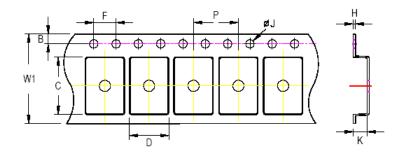

## SOT/TSOT-23-5

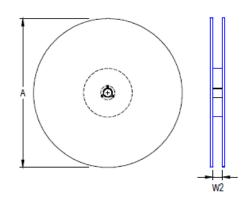

| Deales es Temp | Tape Size | Pocket Pitch | Reel Size (A) |      | Units    | Trailer | Leader | Reel Width (W2) |  |

|----------------|-----------|--------------|---------------|------|----------|---------|--------|-----------------|--|

| Package Type   | (W1) (mm) | (P) (mm)     | (mm)          | (in) | per Reel | (mm)    | (mm)   | Min/Max (mm)    |  |

| TSOT-23-5      | 8         | 4            | 180           | 7    | 3,000    | 160     | 600    | 8.4/9.9         |  |

- C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 8mm carrier tape: 0.5mm max.

| Tona Cina | W1    | F     | )     | Е      | 3      | F     | -     | Q     | J     | ŀ     | <b>`</b> | Н     |

|-----------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|----------|-------|

| Tape Size | Max   | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max      | Max   |

| 8mm       | 8.3mm | 3.9mm | 4.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.2mm    | 0.6mm |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

DS9080-09 December 2024

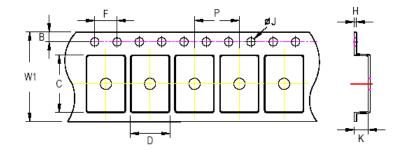

#### 21.1.2 ZQFN-4L 1x1

#### 21.1.2.1 Quadrant 1

| 5                  | Tape Size | Pocket Pitch | Reel Size (A) |      | Units    | Trailer | Leader | Reel Width (W2) |  |

|--------------------|-----------|--------------|---------------|------|----------|---------|--------|-----------------|--|

| Package Type       | (W1) (mm) | (P) (mm)     | (mm)          | (in) | per Reel | (mm)    | (mm)   | Min/Max (mm)    |  |

| (Z) QFN/DFN<br>1x1 | 8         | 4            | 180           | 7    | 2,500    | 160     | 600    | 8.4/9.9         |  |

C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 8mm carrier tape: 0.5mm max.

| Tono Cizo | W1    | F     | )     | E      | 3      | F     | =     | Q     | ðJ    | ŀ     | <     | Н     |

|-----------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max   | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 8mm       | 8.3mm | 3.9mm | 4.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.5mm | 0.6mm | 0.6mm |

DS9080-09

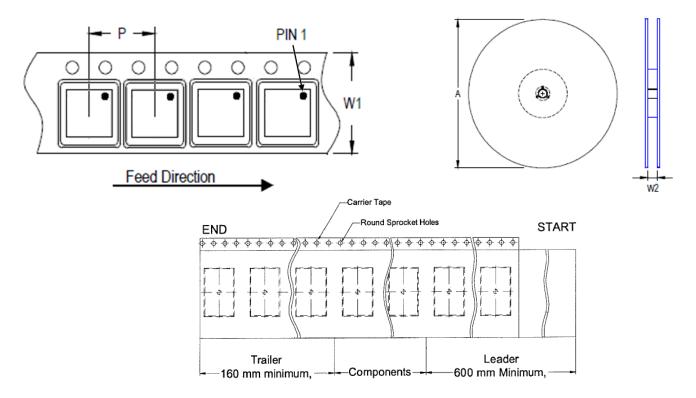

#### 21.1.2.2 Quadrant 2

| Davis and Too      | Tape Size | Pocket Pitch | Reel Size (A) |      | Units    | Trailer | Leader | Reel Width (W2) |  |

|--------------------|-----------|--------------|---------------|------|----------|---------|--------|-----------------|--|

| Package Type       | (W1) (mm) | (P) (mm)     | (mm)          | (in) | per Reel | (mm)    | (mm)   | Min/Max (mm)    |  |

| (Z) QFN/DFN<br>1x1 | 8         | 4            | 180           | 7    | 2,500    | 160     | 600    | 8.4/9.9         |  |

- C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 8mm carrier tape: 0.5mm max.

| Tono Cizo | W1    | F     | )     | Е      | 3      | F     | =     | Q     | ðЈ    | ŀ     | (     | Н     |

|-----------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max   | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 8mm       | 8.3mm | 3.9mm | 4.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.5mm | 0.6mm | 0.6mm |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

# 21.2 Tape and Reel Packing

#### 21.2.1 TSOT-23-5

| Step | Photo/Description                      | Step | Photo/Description            |

|------|----------------------------------------|------|------------------------------|

| 1    | Reel 7"                                | 4    | 3 reels per inner box Box A  |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A           |

| Container | R    | teel  |       | Вох   |       | Carton   |                    |         |  |

|-----------|------|-------|-------|-------|-------|----------|--------------------|---------|--|

| Package   | Size | Units | Item  | Reels | Units | Item     | Boxes              | Unit    |  |

| T00T 00 5 | 7"   | 3,000 | Box A | 3     | 9,000 | Carton A | 12                 | 108,000 |  |

| TSOT-23-5 |      | ,     | Box E | 1     | 3,000 | For C    | ombined or Partial | Reel.   |  |

#### 21.2.2 ZQFN-4L 1x1

### 21.2.2.1 Quadrant 1

| Step | Photo/Description                      | Step | Photo/Description            |

|------|----------------------------------------|------|------------------------------|

| 1    | Reel 7"                                | 4    | 3 reels per inner box Box A  |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A           |

| Container       | R    | teel  |       | Вох   |       | Carton   |                     |        |  |

|-----------------|------|-------|-------|-------|-------|----------|---------------------|--------|--|

| Package         | Size | Units | Item  | Reels | Units | Item     | Boxes               | Unit   |  |

| (7) OFN/DEN 44  | 7"   | 2,500 | Box A | 3     | 7,500 | Carton A | 12                  | 90,000 |  |

| (Z) QFN/DFN 1x1 |      | ŕ     | Box E | 1     | 2,500 | For C    | combined or Partial | Reel.  |  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

DS9080-09 December 2024 www.richtek.com

#### 21.2.2.2 Quadrant 2

| Step | Photo/Description                      | Step | Photo/Description            |

|------|----------------------------------------|------|------------------------------|

| 1    | Reel 7"                                | 4    | 3 reels per inner box Box A  |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A           |

| Container       | R    | teel  |       | Вох   |       | Carton   |                     |        |  |

|-----------------|------|-------|-------|-------|-------|----------|---------------------|--------|--|

| Package         | Size | Units | Item  | Reels | Units | Item     | Boxes               | Unit   |  |

| (Z) OFN/DEN 4 4 | 7"   | 2,500 | Box A | 3     | 7,500 | Carton A | 12                  | 90,000 |  |

| (Z) QFN/DFN 1x1 |      |       | Box E | 1     | 2,500 | For C    | combined or Partial | Reel.  |  |

## 21.3 Packing Material Anti-ESD Property

| Surface<br>Resistance | Aluminum Bag                        | Reel                                | Cover Tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|-----------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega/\text{cm}^2$  | 10 <sup>4</sup> to 10 <sup>11</sup> |

# **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1st Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patients or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

DS9080-09 December 2024 www.richtek.com

# 22 Datasheet Revision History

| Version | Date       | Description | Item                                                                                                                                                                                                                                                               |  |  |  |  |

|---------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 08      | 2024/3/22  | Modify      | Rewrite                                                                                                                                                                                                                                                            |  |  |  |  |

| 09      | 2024/11/11 | Modify      | General Description on page 1 Features on page 1 Ordering Information on page 1 Electrical Characteristics on page 6 Typical Application Circuit on page 7 Application Information on page 13, 16 Packing Information on page 20 to 26 - Added packing information |  |  |  |  |