# Multi-Phase PWM Controller with PWM-VID Reference

# **General Description**

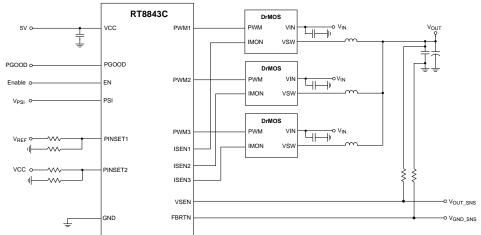

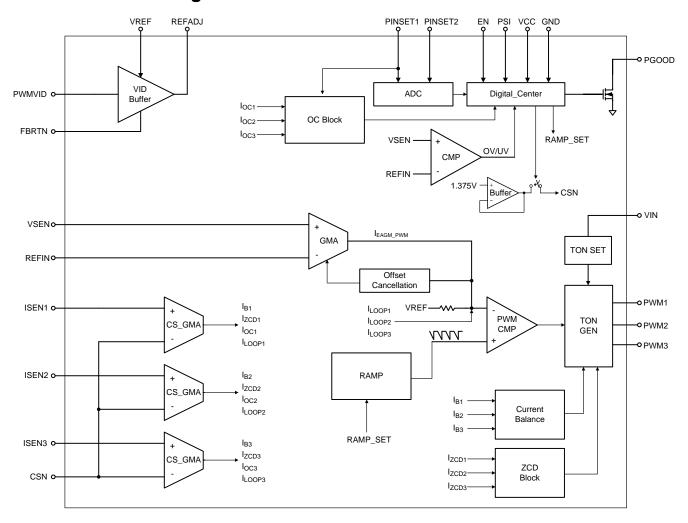

The RT8843C is a 3/2/1 multi-phase synchronous Buck controller optimized for high performance graphic microprocessor, and it support nVidia OVR3i+ spec with PWM-VID interface. It can support both DrMOS with current output and DCR current sensing. The RT8843C adopts AC G-NAVP<sup>TM</sup> (Green Native AVP), which is Richtek's proprietary topology derived from finite DC gain of internal GM amplifier with current mode control. By utilizing the AC G-NAVP<sup>TM</sup> topology, the operating frequency of the RT8843C varies with VID, load and input voltage to further enhance the efficiency even in CCM. Moreover, the AC G-NAVP<sup>TM</sup> with CCRCOT (Constant Current Ripple COT) technology provides superior output voltage ripple over the entire input/output range.

The RT8843C features external reference input and PWM-VID dynamic output voltage control, in which the output voltage is regulated and tracks external input reference voltage. The RT8843C can set internal RAMP amplitude through PINSETx pin, which optimizes stability and load transient performance. The RT8843C also provides complete fault protection functions including Overvoltage Protection (OVP), Undervoltage Protection (UVP), Overcurrent Limit (OCL) and Over-Temperature Protection (OTP).

## **Features**

- Multi-Phase PWM Controller

- PWM-VID Dynamic Voltage Control

- Support 1.8V PWM-VID Interface

- Power State Indicator

- ▶ 1-Phase-DEM/Full-Phase-DEM/ Full-Phase -CCM

- External Reference Input Control

- 3/2/1 Phase Hardware Setting

- · Adjustable Soft-Start time

- Adjustable Current-Limit Threshold

- Adjustable Switching Frequency

- UVP/OVP/OTP Protection

- Power Good Indicator

# **Applications**

• GPU Core Power for OVR3i+ Spec

# **Simplified Application Circuit**

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

# **Ordering Information**

## Note:

Richtek products are Richtek Green Policy compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

# **Marking Information**

VY=: Product Code YMDNN: Date Code

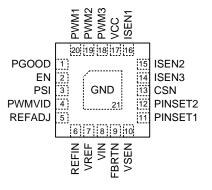

# **Pin Configuration**

WQFN-20L 3x3

# **Functional Pin Description**

| Pin No.          | Pin Name  | Pin Function                                                                                                                          |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1                | PGOOD     | Power good indicator output. Active high open-drain output. A 10k pull high resistor is needed.                                       |

| 2                | EN        | Enable control input. Active high input.                                                                                              |

| 3                | PSI       | Controller power state setting input. H: full-phase CCM. MID: full-phase DEM. L:1-phase DEM                                           |

| 4                | PWMVID    | Programming output voltage control input. Refer to PWM-VID dynamic voltage control.                                                   |

| 5                | REFADJ    | Reference adjustment output. Refer to PWM-VID dynamic voltage control.                                                                |

| 6                | REFIN     | External reference input                                                                                                              |

| 7                | VREF      | Reference voltage output. This is a high precision voltage reference (2V) from the VREF pin to FBRTN pin.                             |

| 8                | VIN       | Connect a RTON resistor from this pin to input voltage to set frequency. A decoupling capacitor cannot be placed on this pin.         |

| 9                | FBRTN     | Return ground. This pin is the negative input of output voltage differential remote sense.                                            |

| 10               | VSEN      | Voltage sense input. This pin is connected to the terminal of output voltage.                                                         |

| 11               | PINSET1   | Soft-start, internal ramp, and OCSET setting input. A decoupling capacitor cannot be placed on this pin.                              |

| 12               | PINSET2   | DrMOS IMON function, Auto-ZCD function, and Internal compensation setting input. A decoupling capacitor cannot be placed on this pin. |

| 13               | CSN       | Output 1.36V when enable DrMOS IMON function.                                                                                         |

| 14, 15, 16       | ISEN[3:1] | Current sense inputs of phase1, 2 and 3.                                                                                              |

| 17               | VCC       | Supply voltage input. Connect this pin to a 5V bias supply. Place a high quality bypass capacitor from this pin to GND.               |

| 18, 19, 20       | PWM[3:1]  | PWM outputs.                                                                                                                          |

| 21 (Exposed Pad) | GND       | Ground. The Exposed pad should be soldered to a large PCB and connected to GND for maximum thermal dissipation.                       |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

# **Functional Block Diagram**

**Absolute Maximum Ratings**

#

(Note 1)

# **Recommended Operating Conditions** (Note 4)

• Input Voltage, VIN ------ 2.7 to 25V

HBM ------ 2kV

- Supply Voltage, Vvcc ----- 4.5 to 5.5V

# **Electrical Characteristics**

ESD Susceptibility

(VVCC = 5V, typical values are referenced to TA =TJ =  $25^{\circ}$ C, Min and Max values are referenced to TA = TJ from  $-10^{\circ}$ C to  $105^{\circ}$ C, unless other noted.)

| Parameter                          | Symbol    | Test Conditions          | Min  | Тур   | Max  | Unit |

|------------------------------------|-----------|--------------------------|------|-------|------|------|

| PWM Controller                     |           |                          |      |       |      |      |

| VCC Supply Voltage                 | Vvcc      |                          | 4.5  | 5     | 5.5  | V    |

| VCC Supply Current                 | Ivcc      | EN = high, not switching |      | 6     | 1    | mA   |

| VCC Shutdown Current               | ISHDN     | EN = 0V                  |      |       | 10   | μΑ   |

| VCC POR Threshold                  |           | VCC rising voltage       |      | 4.3   |      | V    |

| VCC UVLO Threshold                 |           | VCC falling voltage      |      | 4.1   |      | V    |

| POR Hysteresis                     |           |                          |      | 200   |      | mV   |

| Reference Voltage                  |           |                          |      |       |      |      |

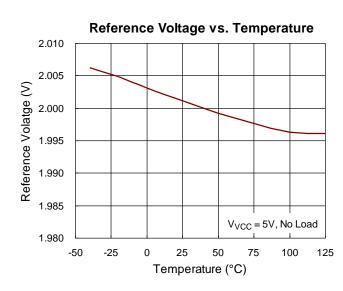

| Reference Voltage                  | VREF      |                          | 1.98 | 2     | 2.02 | V    |

| CSN Output Voltage                 | VCSN_OUT  |                          | 1.3  | 1.375 | 1.45 | V    |

| PWMVID Input Voltage               |           |                          |      |       |      |      |

| PWMVID Input Voltage<br>Logic-High | VPWMVID_H |                          | 1.2  |       |      | V    |

| PWMVID Input Voltage<br>Logic-Low  | VPWMVID_L |                          |      |       | 0.6  | V    |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

| Parameter                                     | Symbol            | Test Conditions                                        | Min   | Тур | Max   | Unit |

|-----------------------------------------------|-------------------|--------------------------------------------------------|-------|-----|-------|------|

| Soft-Start                                    |                   |                                                        |       |     |       |      |

| Soft-Start Ramp Up Slew<br>Rate               |                   | Slew rate set to 1mV/μs                                | 0.9   | 1   | 1.1   | mVμs |

| PGOOD Blanking Time                           | tpgood            | From EN go high to PGOOD go high                       |       |     | 2     | ms   |

| EN and Logic Input                            |                   |                                                        |       |     |       |      |

| EN Threshold                                  | VEN_H             |                                                        | 0.7   |     |       | V    |

| ENTITIESTICIO                                 | V <sub>EN_L</sub> |                                                        | 1     |     | 0.3   | V    |

| Leakage Current of EN, PGOOD, PSI             |                   |                                                        | -1    |     | 1     | μΑ   |

| PSI Input Voltage                             |                   |                                                        |       |     |       |      |

| PSI Logic High Threshold                      | Vpsi_ih           |                                                        | 1.6   |     |       | V    |

| PSI Logic Tri-State<br>Threshold              | VPSI_HIZ          |                                                        | 0.8   |     | 1.2   | V    |

| PSI Logic Low Threshold                       | VPSI_IL           |                                                        |       |     | 0.4   | V    |

| TON Setting                                   |                   |                                                        |       |     | •     |      |

| ON-Time Setting                               | ton               | ITON = 40μA, VREFIN = 1V                               | 190   | 210 | 230   | ns   |

| IPINSET                                       |                   |                                                        |       |     |       |      |

| PIN SET Current                               | IPINSET           | VPINSET = 1V                                           | 79.2  | 80  | 80.8  | μΑ   |

| EA/GM Amplifier                               |                   |                                                        |       |     |       |      |

| Input Offset                                  | VEAOFS            |                                                        | -3    |     | 3     | mV   |

| CS Amplifier                                  |                   |                                                        |       |     |       |      |

| Input Offset                                  | VEAOFS            |                                                        | -0.6  |     | 0.6   | mV   |

| Protection Function                           |                   |                                                        |       |     |       |      |

| Relative Overvoltage<br>Protection Threshold  | VROVP             | VREFIN ≥ 1.33V                                         | 142.5 | 150 | 157.5 | %    |

| Absolute Overvoltage Protection Threshold     | VABOVP            | VREFIN < 1.33V,                                        | 1.9   | 2   | 2.1   | ٧    |

| OV Fault Delay                                |                   | FB forced above OV threshold                           |       | 5   |       | μS   |

| Relative Undervoltage<br>Protection Threshold | VRUVP             |                                                        | 35    | 40  | 45    | %    |

| UV Fault Delay                                |                   | FB forced above UV threshold                           | 1     | 3   |       | μS   |

| Thermal Shutdown<br>Threshold                 | T <sub>SD</sub>   |                                                        |       | 150 |       | °C   |

| Par phase OC Current                          | Voor              | VOCSET = 800mV, ISNEx – CSN, for DCR DRMOS Application | 21    | 25  | 29    | mV   |

| Per-phase OC Current                          | VOCP              | VOCSET = 800mV, ISENx – CSN, for SPS DRMOS Application | 70    | 77  | 84    | mV   |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

| Parameter              | Symbol   | Test Conditions   | Min  | Тур  | Max | Unit |

|------------------------|----------|-------------------|------|------|-----|------|

| PWM Driving Capability |          |                   |      |      |     |      |

| PWM Source Resistance  | RPWM_SRC |                   |      | 30   |     | Ω    |

| PWM Sink Resistance    | RPWM_SNK |                   |      | 10   |     | Ω    |

| PWM Tri-state Voltage  | VPWM_Tri | Vcc = 5V (Note 5) | 1.65 | 1.95 | 2.2 | V    |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}\text{C}$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precautions are recommended.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- Note 5. Pull PWM to HIZ voltage 200ns when PWM enters HIZ.

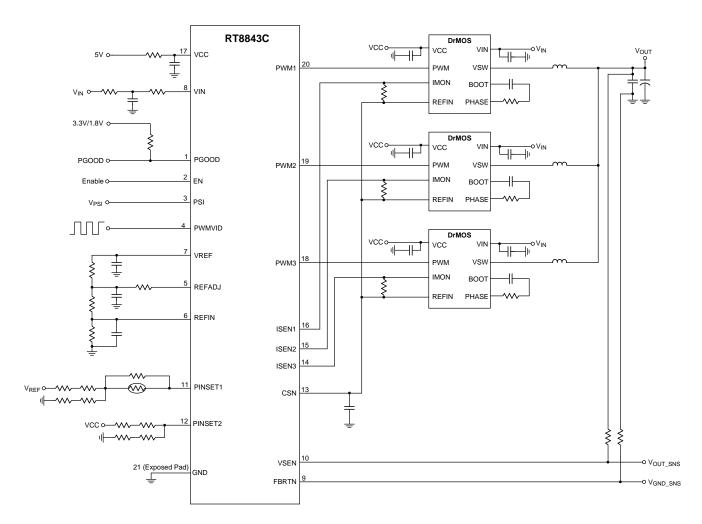

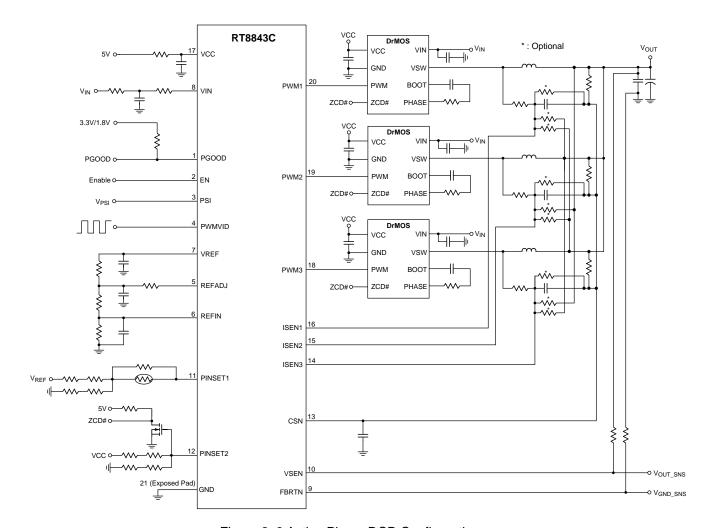

# **Typical Application Circuit**

Figure 1. 3 Active Phase IMON Configuration

Figure 2. 3 Active Phase DCR Configuration

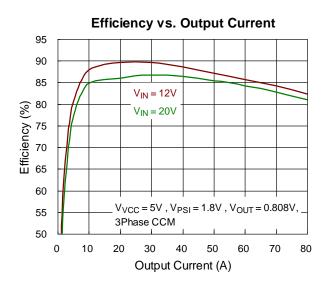

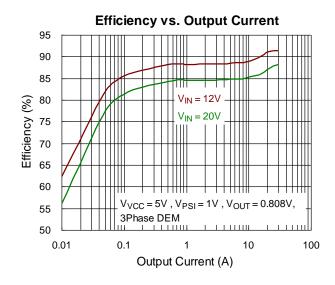

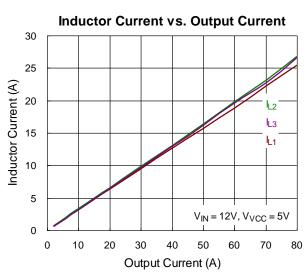

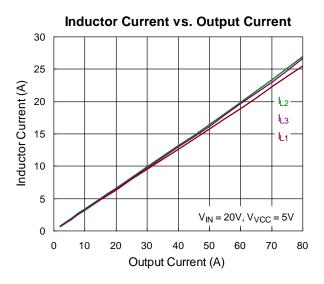

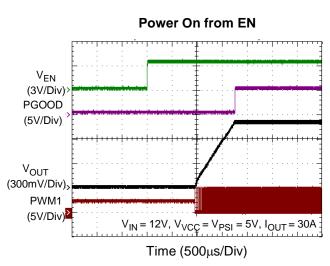

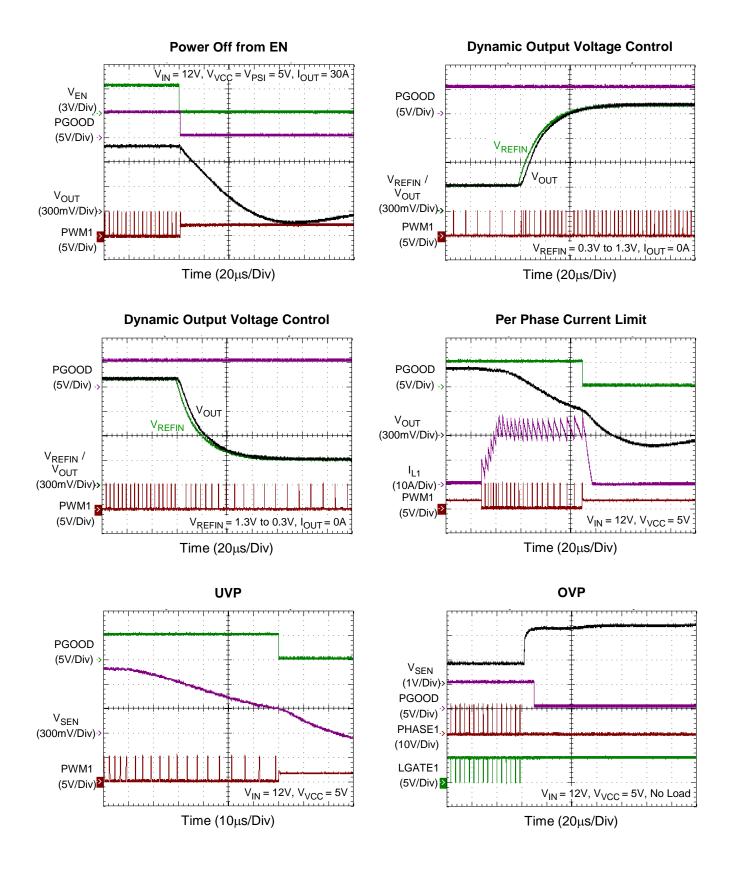

# **Typical Operating Characteristics**

Time (20µs/Div)

Time (20µs/Div)

# **Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and reserve suitable design margin to ensure the functional suitability of their components and systems.

The RT8843C is a three-phase synchronous Buck controller optimized for high performance graphic microprocessor and computer applications.

The RT8843C adopts AC G-NAVPTM (Green Native Adaptive Voltage Positioning), which is Richtek's proprietary topology derived from finite DC gain of internal GM amplifier with current mode control. By utilizing the AC G-NAVPTM topology, the operating frequency of the RT8843C varies with VID, load and input voltage to further enhance the efficiency even in CCM. Moreover, the AC G-NAVPTM with CCRCOT (Constant Current Ripple COT) technology provides superior output voltage ripple over the entire input/output range.

The RT8843C features external reference input and PWM-VID dynamic output voltage control, in which the output voltage is regulated by tracking external input reference voltage. In addition, the RT8843C integrates multiple functions including Internal-Ramp-Setting, AI Gain Selection, Soft-Start Time Setting, SPS Current Auto-Zero-Current Sensing, Detection, and Overcurrent Limiting. These functions can be achieved through PINSET voltage setting. The RT8843C also comprehensive protection, provides not only Overcurrent Limiting (OCL), but also Overvoltage Protection (OVP), Undervoltage Protection (UVP) and Over-Temperature Protection (OTP).

## Power-On Reset (POR), UVLO

Power-On Reset (POR) occurs as VVCC rises above to approximately 4.3V (typical), and the RT8843C resets the fault latch circuit and prepares for PWM operation.

When the VVCC is lower than 4.1V (typical), PWMx signal is kept low to inhibit any switching through Undervoltage Lockout (UVLO).

#### **Enable and Disable**

The EN pin is a high impedance input that allows power sequencing between the controller bias voltage and another voltage rail. The RT8843C remains in shutdown if the EN pin is lower than 300mV. When the EN voltage rises above the 700mV high level threshold, the RT8843C begins a new initialization and soft-start cycle. EN timing must be later than VCC POR in order to ensure that the PINSET function can be set normally.

# **Power Good Indicator (PGOOD)**

The PGOOD pin is an open-drain output, and requires a pull-up resistor. During soft-start time period, the PGOOD remains low. When the output voltage reaches to REFIN voltage, PGOOD is pulled high and latched. If OVP/UVP is triggered or EN goes low during operation, the PGOOD will be pulled low immediately.

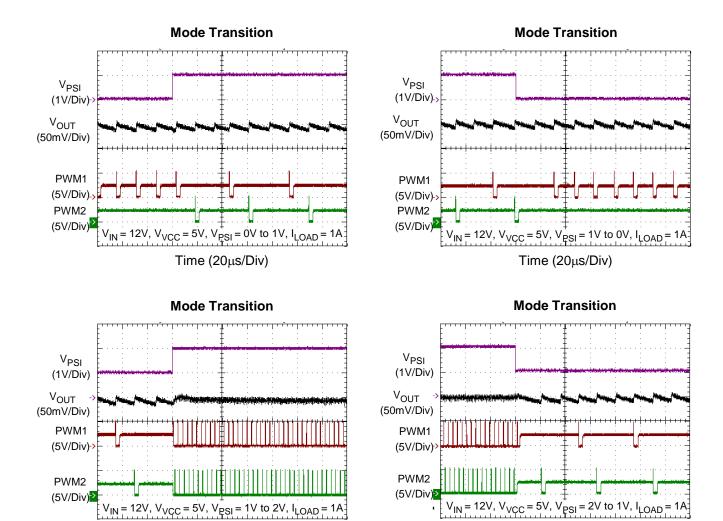

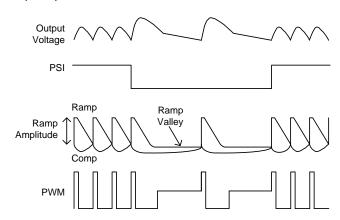

# **Operation Mode Setting**

The RT8843C provides three operation modes, 1-Phase with DEM, multi-Phase with DEM and multi-Phase with CCM. In DEM operation, the RT8843C automatically reduces the operation frequency at light load conditions for saving power loss. The operating mode can be set by the voltage of the PSI pin as listed in Table 1. Moreover, the PSI pin is valid after POR of VR.

Table 1.

| Operation Mode         | PSI Voltage Setting |

|------------------------|---------------------|

| 1-Phase with DEM       | 0V to 0.4V          |

| Multi-Phase with DEM*1 | 0.8V to 1.2V        |

| Multi-Phase with CCM*1 | 1.6V to 5.5V        |

<sup>\*1:</sup> multi-phase number by hardware setting

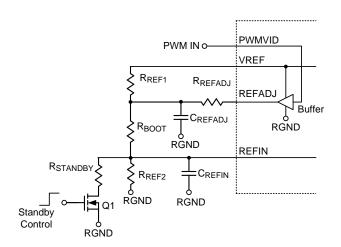

## **PWM VID and Dynamic Output Voltage Control**

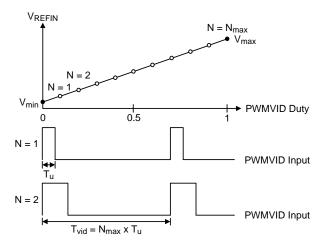

The RT8843C features a PWM VID input for dynamic output voltage control as shown in Figure 3, which reduces the number of device pin and enables a wide

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

dynamic voltage range. The output voltage is determined by the applied voltage on the REFIN pin and duty cycle of PWMVID.

Figure 3. PWM VID Analog Circuit Diagram

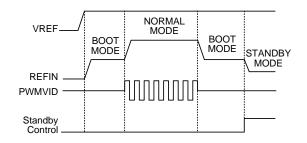

Through utilizing the external circuit and VID control signal, the controller provides three operation modes as shown in Figure 4.

Figure 4. PWM VID Time Diagram

## **BOOT Mode**

When the PWMVID is not driven, the buffer output is in tri-state. At this time, PWM-VID circuit is working in BOOT mode and Q1 is turned off. Further, REFIN is connected to a resistor divider as shown in Figure 3. The following equation expresses VBOOT equation from REFIN and divider resistors.

$$VBOOT = VVREF \times \left(\frac{RREF2}{RREF1 + RREF2 + RBOOT}\right)$$

where VVREF = 2V (typ.)

Choose RREF2 to be approximately  $10k\Omega$ , and the RREF1 and RBOOT can be calculated by the following equations:

$$RREF1 + RBOOT = \frac{RREF2 \times (VVREF - VBOOT)}{VBOOT}$$

$$RREF1 = \frac{RREF2 \times (VVREF - VBOOT)}{VBOOT} - RBOOT$$

$$RBOOT = \frac{RREF2 \times (VVERF - VBOOT)}{VBOOT} - RREF1$$

## **Standby Mode**

When the PWMVID control is to enter the standby mode, the standby voltage can be set via RSTANDBY and Q1 as shown in Figure 3. The standby voltage is set by a voltage that is lower than the PWMVID operating range. Assuming the PWMVID operating range is 0.3V to 1.3V, then the standby voltage will be set below than 0.3V. However, as the REFIN voltage is lower than 0.2V, the controller will pull the PWM into tri-state. Therefore, the standby voltage setting range is recommended from 0.2V to the lowest voltage of PWMVID operation voltage.

The following conditions must be met when entering standby mode. 1. PWMVID pin is floating, 2. Q1 is enabled. Further, the desired value can be set by the following equation:

$$Vstandby = Vvref \times \frac{Rref2//Rstandby}{Rref1 + Rboot + (Rref2//Rstandby)}$$

By choosing RREF1, RREF2, and RBOOT, the RSTANDBY can be calculated by the following equation:

RSTANDBY=

$$\frac{ Vstandby \times Rref2 \times \left( Rref1 + Rboot \right)}{ Vvref \times Rref2 - Vstandby \times \left( Rref1 + Rref2 + Rboot \right)}$$

#### **Normal Mode**

If the PWMVID pin is driven by a PWM signal and switch Q1 is disabled as shown in Figure 3. The VREFIN can be adjusted from Vmin to Vmax, where Vmin is the voltage at zero percent PWM duty cycle and Vmax is the voltage at one hundred percent PWM duty cycle. The Vmin and Vmax can be set by the following equations:

$$V_{min} = V_{VREF} \times \frac{R_{REF2}}{R_{REF2} + R_{BOOT}}$$

$$\times \frac{R_{REFADJ} / (R_{BOOT} + R_{REF2})}{R_{REF1} + \left[ \left( R_{REFADJ} / (R_{BOOT} + R_{REF2}) \right) \right]}$$

$$V_{max} = V_{VREF} \times \frac{R_{REF2}}{\left( R_{REF1} / R_{REFADJ} \right) + R_{BOOT} + R_{REF2}}$$

By choosing RREF1, RREF2, and RBOOT, the RREFADJ can be calculated by the following equation:

$$RREFADJ = \frac{RREF1 \times Vmin}{Vmax - Vmin}$$

The relationship between PWMVID duty and VREFIN is shown in Figure 5, and VOUT can be set according to the following equation.

$VOUT = Vmin + N \times VSTEP$

where the VSTEP is the resolution of each voltage step:

$$VSTEP = \frac{V_{max} - V_{min}}{N_{max}}$$

where Nmax is the number of total available voltage steps and N is the number of steps at a specific Vout. The dynamic voltage VID period (Tvid = Tu x Nmax) is determined by the unit pulse width (Tu), and the available step number (Nmax). The recommended Tu is 27ns.

Figure 5. PWM VID Analog Output

## **VID Slew Rate Control**

In the RT8843C, the VREFIN slew rate is proportional to PWM VID duty and, the rising time and falling time are the same. In normal mode, the VREFIN slew rate SR can be estimated by CREFADJ as expressed in the following equation:

$$\begin{split} SR &= \frac{\left(V\text{REFIN\_Final} - V\text{REFIN\_Initial}\right) \times 80\%}{2.2 \times R\text{SR} \times C\text{REFADJ}} \\ RSR &= \left[\left(R\text{REF1} / / R\text{REFADJ}\right)\right] / / \left(R\text{BOOT} + R\text{REF2}\right) \end{split}$$

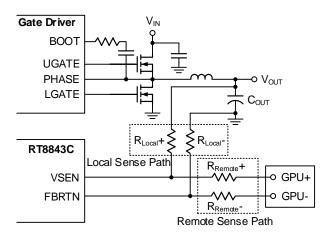

# **Remote Sense Setting**

In order to allow the load voltage to be accurately detected to avoid the voltage drop from output to load, the RT8843C uses a high-accuracy differential amplifier to directly detect the voltage at the end of GPU through the VSEN and FBRTN pins. The VOUT sensing network from controller to the load and output needs to be specially designed according to different load conditions. The output voltage detection circuit has two loops, the remote sense path (from the controller to the load end of GPU) and the local sense path (from the controller to the output capacitor) as shown in Figure 6. When the load is GPU, in order to make the GPU voltage consistent with REFIN, the R<sub>Remote</sub> must be set to  $0\Omega$ . At this time, the purpose of local sense path is to avoid the output overvoltage caused by the GPU open. Therefore, the R<sub>Local</sub> must be placed a  $10\Omega$  to  $100\Omega$  resistor. If the GPU is not used and load from the end of Vout, the RLocal must be set to  $0\Omega$  to avoid PWM jitter caused by delayed output voltage signal. Considering the components placement, it is recommended to place all the detecting resistors on the controller side. This setting can minimize the path of local sense, and make the system debug easier as any noise coupling occurs on the sensing path.

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

Figure 6. Output Voltage Sensing

## **Multi-Function Pin Setting**

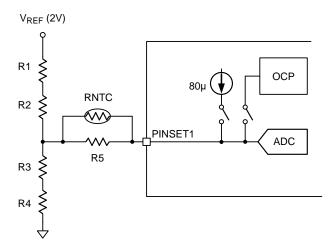

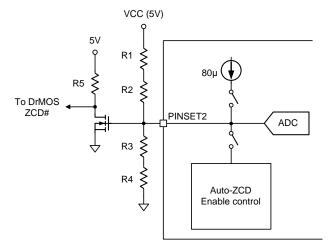

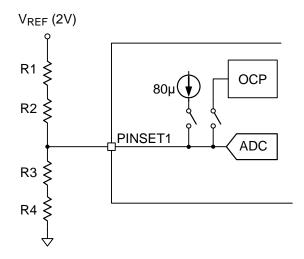

For reducing total pin number of the package, PINSET1 and PINSET2 pins adopt the multi-function pin setting mechanism in the RT8843C. Table 2 summarizes the overall pin setting function. Figure 7 shows the Pin Setting Circuit. The voltage divider of each PINSET pin is used to set desired function. The setting voltage of each PINSET pin can be represented as

$$\begin{split} V_{PINSET1} &= V_{REF}(2V) \times \frac{R3 + R4}{R1 + R2 + R3 + R4} \\ V_{PINSET2\_V} &= V_{VCC}(5V) \times \frac{R3 + R4}{R1 + R2 + R3 + R4} \\ V_{PINSET2\_I} &= 80\mu \times \frac{(R1 + R2) \times (R3 + R4)}{R1 + R2 + R3 + R4} \end{split}$$

Table 3, Table 4 and Table 5 show the pin setting function table. The ramp example for a typical 300kHz application is also shown on Table 6.

Figure 7. Multi-Function Pin Setting Circuit

# **Table 2. Pin Set Table**

|         | Function1            | Function2            | Function2                 | Function3                  | Function4 |

|---------|----------------------|----------------------|---------------------------|----------------------------|-----------|

| PINSET1 | Soft-Start Slew Rate | Ramp Amplitude <2:0> | N/A                       | N/A                        | N/A       |

| PINSET2 | Ramp Valley          | Ramp Amplitude <3>   | Dr.IMON<br>Enable/Disable | Auto-ZCD<br>Enable/Disable | Al Gain   |

Table 3. PINSET1 Pin Setting for Soft-Start Slew Rate and Ramp Amplitude

|                         | RAMP                    | Amplitude <2: | :0> (mV)    | $V_{PINSET1} = V_{REF}(2V) \times \frac{R3 + R4}{R1 + R2 + R3 + R}$ |         |         | R4      |

|-------------------------|-------------------------|---------------|-------------|---------------------------------------------------------------------|---------|---------|---------|

| SS Slew Rate<br>(mV/µs) | V <sub>RAMP_AMP</sub> = | 30000×(16-    | RAMP <3:0>) |                                                                     |         |         | R3 + R4 |

| (πνημο)                 | *KAIVIP_AIVIP           | 1             | fs          | Min                                                                 | Тур     | Max     | Unit    |

|                         | 0                       | 0             | 0           | 0                                                                   | 15.625  | 18.125  | mV      |

|                         | 0                       | 0             | 1           | 44.375                                                              | 46.875  | 49.375  | mV      |

|                         | 0                       | 1             | 0           | 75.625                                                              | 78.125  | 80.625  | mV      |

| 1                       | 0                       | 1             | 1           | 106.875                                                             | 109.375 | 111.875 | mV      |

| 1                       | 1                       | 0             | 0           | 138.125                                                             | 140.625 | 143.125 | mV      |

|                         | 1                       | 0             | 1           | 169.375                                                             | 171.875 | 174.375 | mV      |

|                         | 1                       | 1             | 0           | 200.625                                                             | 203.125 | 205.625 | mV      |

|                         | 1                       | 1             | 1           | 231.875                                                             | 234.375 | 236.875 | mV      |

|                         | 0                       | 0             | 0           | 263.125                                                             | 265.625 | 268.125 | mV      |

|                         | 0                       | 0             | 1           | 294.375                                                             | 296.875 | 299.375 | mV      |

|                         | 0                       | 1             | 0           | 325.625                                                             | 328.125 | 330.625 | mV      |

| 2                       | 0                       | 1             | 1           | 356.875                                                             | 359.375 | 361.875 | mV      |

| 2                       | 1                       | 0             | 0           | 388.125                                                             | 390.625 | 393.125 | mV      |

|                         | 1                       | 0             | 1           | 419.375                                                             | 421.875 | 424.375 | mV      |

|                         | 1                       | 1             | 0           | 450.625                                                             | 453.125 | 455.625 | mV      |

|                         | 1                       | 1             | 1           | 481.875                                                             | 484.375 | 486.875 | mV      |

|                         | 0                       | 0             | 0           | 513.125                                                             | 515.625 | 518.125 | mV      |

|                         | 0                       | 0             | 1           | 544.375                                                             | 546.875 | 549.375 | mV      |

|                         | 0                       | 1             | 0           | 575.625                                                             | 578.125 | 580.625 | mV      |

| 6                       | 0                       | 1             | 1           | 606.875                                                             | 609.375 | 611.875 | mV      |

| 6                       | 1                       | 0             | 0           | 638.125                                                             | 640.625 | 643.125 | mV      |

|                         | 1                       | 0             | 1           | 669.375                                                             | 671.875 | 674.375 | mV      |

|                         | 1                       | 1             | 0           | 700.625                                                             | 703.125 | 705.625 | mV      |

|                         | 1                       | 1             | 1           | 731.875                                                             | 734.375 | 736.875 | mV      |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

Table 4. PINSET2\_V Pin Setting for Ramp Amplitude and Ramp Valley

| RAMP Valley (mV) | RAMP Amplitude <3> (mV) 30000×(16-RAMP <3:0>)                            |        |      | $/) \times \frac{R3}{R1 + R2}$ | + R4<br>+ R3 + R4 |

|------------------|--------------------------------------------------------------------------|--------|------|--------------------------------|-------------------|

|                  | $V_{RAMP\_AMP} = \frac{second(10^{\circ} 14^{\circ} 40^{\circ})}{f_{S}}$ | Min    | Тур  | Max                            | Unit              |

| 100              | 0                                                                        | 0      | 25   | 27.5                           | mV                |

| 100              | 1                                                                        | 72.5   | 75   | 77.5                           | mV                |

| 150              | 0                                                                        | 122.5  | 125  | 127.5                          | mV                |

| 150              | 1                                                                        | 172.5  | 175  | 177.5                          | mV                |

| 200              | 0                                                                        | 222.5  | 225  | 227.5                          | mV                |

| 200              | 1                                                                        | 272.5  | 275  | 277.5                          | mV                |

| 250              | 0                                                                        | 322.5  | 325  | 327.5                          | mV                |

| 250              | 1                                                                        | 372.5  | 375  | 377.5                          | mV                |

| 300              | 0                                                                        | 422.5  | 425  | 427.5                          | mV                |

| 300              | 1                                                                        | 472.5  | 475  | 477.5                          | mV                |

| 350              | 0                                                                        | 522.5  | 525  | 527.5                          | mV                |

| 350              | 1                                                                        | 572.5  | 575  | 577.5                          | mV                |

| 400              | 0                                                                        | 622.5  | 625  | 627.5                          | mV                |

| 400              | 1                                                                        | 672.5  | 675  | 677.5                          | mV                |

| 450              | 0                                                                        | 722.5  | 725  | 727.5                          | mV                |

| 450              | 1                                                                        | 772.5  | 775  | 777.5                          | mV                |

| 500              | 0                                                                        | 822.5  | 825  | 827.5                          | mV                |

| 500              | 1                                                                        | 872.5  | 875  | 877.5                          | mV                |

| 550              | 0                                                                        | 922.5  | 925  | 927.5                          | mV                |

| 550              | 1                                                                        | 972.5  | 975  | 977.5                          | mV                |

| 600              | 0                                                                        | 1022.5 | 1025 | 1027.5                         | mV                |

| 600              | 1                                                                        | 1072.5 | 1075 | 1077.5                         | mV                |

| 650              | 0                                                                        | 1122.5 | 1125 | 1127.5                         | mV                |

| 650              | 1                                                                        | 1172.5 | 1175 | 1177.5                         | mV                |

| 700              | 0                                                                        | 1222.5 | 1225 | 1227.5                         | mV                |

| 700              | 1                                                                        | 1272.5 | 1275 | 1277.5                         | mV                |

| 750              | 0                                                                        | 1322.5 | 1325 | 1327.5                         | mV                |

| 750              | 1                                                                        | 1372.5 | 1375 | 1377.5                         | mV                |

| 800              | 0                                                                        | 1422.5 | 1425 | 1427.5                         | mV                |

| 800              | 1                                                                        | 1472.5 | 1475 | 1477.5                         | mV                |

| 850              | 0                                                                        | 1522.5 | 1525 | 1527.5                         | mV                |

| 850              | 1                                                                        | 1572.5 | 1575 | 1577.5                         | mV                |

# Table 5. PINSET2\_I Pin Setting for Enable Dr.IMON, Enable Auto-ZCD and Al Gain Selection

| Dr.IMON Auto_ZCD# |         | ZCD# Al Gain $V_{PINSET2\_I} = 80\mu \times \frac{(R1 + R2) \times (R3 + R4)}{R1 + R2 + R3 + R4}$ |      |      |      | R4)<br>R4 |

|-------------------|---------|---------------------------------------------------------------------------------------------------|------|------|------|-----------|

|                   |         |                                                                                                   | Min  | Тур  | Max  | Unit      |

|                   |         | Disable                                                                                           | 0    | 50   | 55   | mV        |

| Diaghla           | Diaghla | 1X                                                                                                | 145  | 150  | 155  | mV        |

| Disable           | Disable | 2X                                                                                                | 245  | 250  | 255  | mV        |

|                   |         | 4X                                                                                                | 345  | 350  | 355  | mV        |

|                   |         | Disable                                                                                           | 445  | 450  | 455  | mV        |

| Diaghla           | Enable  | 1X                                                                                                | 545  | 550  | 555  | mV        |

| Disable           |         | 2X                                                                                                | 645  | 650  | 655  | mV        |

|                   |         | 4X                                                                                                | 745  | 750  | 755  | mV        |

|                   |         | Disable                                                                                           | 845  | 850  | 855  | mV        |

| Fnoble            | Diochlo | 1X                                                                                                | 945  | 950  | 955  | mV        |

| Enable            | Disable | 2X                                                                                                | 1045 | 1050 | 1055 | mV        |

|                   |         | 4X                                                                                                | 1145 | 1150 | 1155 | mV        |

|                   |         | Disable                                                                                           | 1245 | 1250 | 1255 | mV        |

| Fnoble            | Fnoble  | 1X                                                                                                | 1345 | 1350 | 1355 | mV        |

| Enable            | Enable  | 2X                                                                                                | 1445 | 1450 | 1455 | mV        |

|                   |         | 4X                                                                                                | 1545 | 1550 | 1555 | mV        |

Table 6. Ramp Amplitude Example for 300kHz Frequency

|             | Code <3:0> |   |   |     |                     |  |

|-------------|------------|---|---|-----|---------------------|--|

| 3 (PINSET2) | 2          | 1 | 0 | DEC | Ramp Amplitude (mV) |  |

| 0           | 0          | 0 | 0 | 0   | 1600                |  |

| 0           | 0          | 0 | 1 | 1   | 1500                |  |

| 0           | 0          | 1 | 0 | 2   | 1400                |  |

| 0           | 0          | 1 | 1 | 3   | 1300                |  |

| 0           | 1          | 0 | 0 | 4   | 1200                |  |

| 0           | 1          | 0 | 1 | 5   | 1100                |  |

| 0           | 1          | 1 | 0 | 6   | 1000                |  |

| 0           | 1          | 1 | 1 | 7   | 900                 |  |

| 1           | 0          | 0 | 0 | 8   | 800                 |  |

| 1           | 0          | 0 | 1 | 9   | 700                 |  |

| 1           | 0          | 1 | 0 | 10  | 600                 |  |

| 1           | 0          | 1 | 1 | 11  | 500                 |  |

| 1           | 1          | 0 | 0 | 12  | 400                 |  |

| 1           | 1          | 0 | 1 | 13  | 300                 |  |

| 1           | 1          | 1 | 0 | 14  | 200                 |  |

| 1           | 1          | 1 | 1 | 15  | 100                 |  |

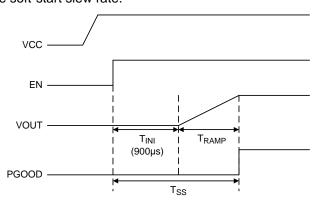

## **Soft-Start**

The RT8843C provides the soft-start function to prevent large inrush current and output voltage overshoot while the converter is being powered up. The soft-start sequence is shown in Figure 8. When EN goes high, the RT8843C enters the internal circuit initialization and pinset function setting. The soft-start circuit starts after the IC initialization is completed. During soft-start period, the output voltage follows the internal soft-start ramp up. The soft-start slew rate has 3 stages that can be adjusted through PINSET1 pin as shown in Table 3. And the soft-start time can be calculated as:

$$TSS = 900\mu S + \frac{VOUT}{SR}$$

where the Vout is the target output voltage and SR is the soft-start slew rate.

Figure 8. Soft-Start Sequence

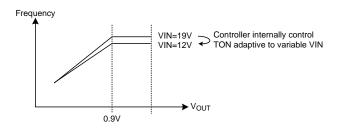

# **Switching Frequency Setting**

Connect a resistor RTON between input terminal and VIN pin to set the on-time width. The RTON can be calculated according to the following formula:

$$\begin{split} &\mathsf{RTON} = \frac{\mathsf{VIN}\text{-}0.9}{8.8 \times 10^{\text{-}12} \times \mathsf{VIN} \times \mathsf{fS}} \quad \big(\mathsf{VOUT} > 0.9\mathsf{V}\big) \\ &\mathsf{RTON} = \frac{\mathsf{VOUT}}{\mathsf{VIN}} \times \frac{\mathsf{VIN}\text{-}\mathsf{VOUT}}{7.9 \times 10^{\text{-}12} \times \mathsf{fS}} \quad \big(0.9\mathsf{V} < \mathsf{VOUT} < 0.5\mathsf{V}\big) \\ &\mathsf{RTON} = \frac{\mathsf{VOUT}}{\mathsf{VIN}} \times \frac{\mathsf{VIN}\text{-}0.5}{7.9 \times 10^{\text{-}12} \times \mathsf{fS}} \quad \big(\mathsf{VOUT} < 0.5\mathsf{V}\big) \end{split}$$

When load increases, on-time keeps constant. The offtime width will be reduced so that input terminal can provide more power to output to regulate output voltage. Hence, the higher load current will result in higher switching frequency.

Higher switching frequency operation can reduce power components' size and PCB space, but the high switching frequency will increase the switching loss, so the frequency setting must be balanced between the component size and overall efficiency.

The recommended frequency setting range is 150kHz to 1.5MHz. And the minimum ToN cannot be less than 70ns, otherwise the frequency will be less than the desired value.

Figure 9. Switching Frequency with Different Vout

## Ramp Setting

The RT8843C provides an internal ramp that effectively suppresses PWM signal jitter in small output ripple applications. The ramp amplitude and valley can be set through PINSET1 and PINSET2 pins as shown in Table 3 and Table 4. The ramp amplitude can be set in total 16 steps. Further, the value according to different switching frequency can be calculated by the following formula:

$$VRAMP\_AMP = \frac{30000 \times (16-RAMP\langle 3:0\rangle)}{fs}$$

Table 6 is a calculation example of a ramp amplitude with a switching frequency of 300kHz. Higher amplitude has better suppression of jitter, but it will reflect poor load transient performance. Therefore, the design of the ramp amplitude needs to be balanced between stability and transient performance. To ensure that the PWM jitter rate is below 15% and load transient response can meet Vout -10%/ +20% of system specifications, the default setting of ramp amplitude is recommended to choose approximately 300mV. In

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

addition, in order to ensure the stability at DEM (the multi-pulse phenomenon does not occur), the ramp valley is recommended to choose 50mV larger than ramp amplitude.

Figure 10. Mode Transition Behavior

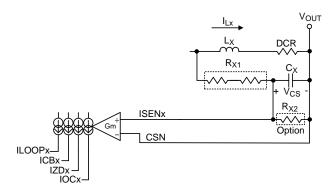

# **Current Sensing**

The RT8843C provides per-phase current sensing amplifier for different current sensing topology including DCR current sensing and SPS current sensing. This current signal is used for loop control, zero current detection, current balance and per-phase current limit.

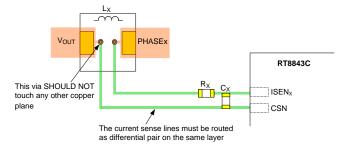

## **DCR Current Sensing**

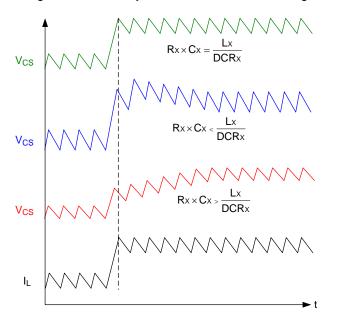

The RT8843C can support inductor DCR current sensing to get each phase current signal, as illustrated in Figure 11. An external low-pass filter Rx1 and Cx reconstruct the current signal. The low-pass filter time constant Rx1 x Cx should match time constant L/DCR of Inductance and DCR. The Rx and Cx can be fine-tuned for transient performance. If RC network time constant is smaller than inductor time constant L/DCR, Vcs current signal leads the inductor current signal, and early trigger per-phase current limit during load transient. If RC network time constant is larger than inductor time constant L/DCR, Vcs current signal has a sluggish rise and delay trigger per-phase current limit during load transient. If RC network time constant matches inductor time constant L/DCR, the trigger level of per-phase current limit will meet desired value. Rx1 is highly recommended to be as two 0603 size resistors in series to enhance the current signal accuracy. X7R type capacitor is suggested for  $C_X$  in the application. Rx2 is optional for preventing Vcs exceeding current sense amplifier input range (-10mV to 90mV). The time constant of (Rx1 // Rx2) x Cx should be match L/DCR.

The current sense lines must be routed as differential pair from the inductor to the controller on the same layer. When the DCR current sensing circuit is selected, the DrIMON enable/disable of PINSET2 function must be set to Disable.

Figure 11. Inductor DCR Current Sensing Method

Figure 12. PCB Layout of DCR Current Sensing

Figure 13. All Kinds of RC Network Time Constant

**Table 7. Pin Setting of DrIMON**

| DrIMON [0] | Enable/Disable |

|------------|----------------|

| 0          | Disable        |

| 1          | Enable         |

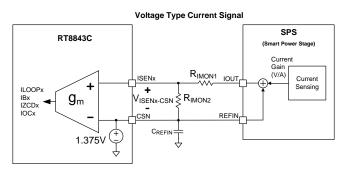

## **SPS Current Sensing**

The RT8843C current sensing circuit can also support SPS current sensing. SPS (Smart Power Stage) can accurately detect the internal MOSFET current for a reference of PWM controller. In addition, SPS current sensing circuit simplifies the quantity of components on the external circuit and provides a more accurate current signal unlike DCR detection circuit. SPS has two kinds of current signal, current output and voltage output. Figure 14 shows the current reporting circuit of different current signals respectively. When the SPS current sensing is used, the DrIMON enable/disable of PINSET2 function must be set to enable. After DrIMON enable is set, the inverting input of the current-sense amplifier generates a 1.375V reference voltage for SPS current sensing circuit. The current is reported to the controller as a differential voltage between the ISENx and CSN pins with a conversion gain to represent the inductor current IL, as shown in below equations.

$VISENx-CSN = gain(A/A) \times IL \times RIMON$

...(Current Type Signal)

$$VISENx\text{-}CSN = gain(V/A) \times IL \times \frac{RIMON2}{RIMON1 + RIMON2}$$

## ...(Voltage Type Signal)

For larger current sense gain as voltage type, it is recommended to place a voltage divider resistor between IOUT and REFIN pins to avoid the controller's current amplifier input voltage range exceeding –10mV to 90mV.

# Current Type Current Signal RT8843C RT8843C SPS (Smart Power Stage) Current Gain (A/A) Current Sensing VISENX-CSN REFIN 1.375V CREFIN

Figure 14. SPS Current Sensing

# **Auto-Zero Crossing Detection (Auto-ZCD)**

The RT8843C can support the system to use ZCD threshold of DrMOS at light load condition. The ZCD function of DrMOS can be enabled by pulled down the ZCD# pin of DrMOS. When using the Auto-ZCD function, the Auto-ZCD# function of PINSET2 must be set to enable. Once the Auto-ZCD function is enabled, PINSET2 turns on the external NMOS and pulls the ZCD# voltage of DrMOS low as shown in Figure 7. The Auto-ZCD function only works at the status of ZCD# = L, PWM = L and GH = L. At this status, if the inductor current  $I_L > 0A$ , then  $G_L = H$ . Conversely, if the inductor current  $I_L < 0A$ , then  $G_L = L$ . In addition, once Auto-ZCD is enabled, the controller only operates in FCCM regardless of PSI setting voltage.

## **Current Balance**

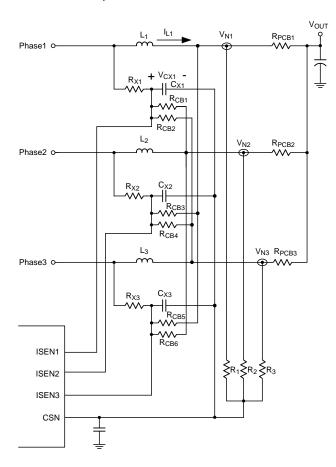

The Per-phase current sense signal of the RT8843C is compared with sensed average current. The comparison result adjusts each phase PWM width to optimize current and thermal balance. When the PCB layout makes the parasitic impedance inconsistent from the inductor to the output, that will affect the performance of the current balance. Figure 15 shows a method to eliminate the parasitic impedance. Place two RCB resistors in each phase of the DCR sensing circuit to cancel the RPCB effect and improve current balance.

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

The R<sub>CBx</sub> value can be calculated by following equation.

$$R_{CBx} = R_{Xx} \times N$$

Where N is the phase number.

Figure 15. Current Balance Improving

## **Per-phase Current Limit**

The RT8843C incorporates per-phase current limit mechanism to prevent overcurrent event. The per-phase current limit circuit employs a unique "valley" current sensing algorithm. If the magnitude of the current sense signal is above the current-limit threshold, the PWM is not allowed to initiate a new cycle. The per-phase current-limit threshold can be set by PINSET1 pin. When the DCR sensing circuit is selected, in order to ensure the accuracy of the current signal over a wide range temperature, it is recommended to use the NTC compensation circuit as shown in Figure 7. The current-limit threshold can be calculated according to the following equation:

= VISENx-CSN

$$\times$$

32 = DCR $\times$ IL\_OC $\times$ 32

Where the IL oc is the desired current-limit threshold.

On the other hand, when the SPS current sensing is selected, as shown in Figure 16, and the current-limit threshold can be calculated as the following equation.

$$Vocset = Vref - \begin{pmatrix} V_{REF} \times \frac{R3 + R4}{R1 + R2 + R3 + R4} + 80\mu \\ \times \left[ (R1 + R2) / (R3 + R4) \right] \end{pmatrix}$$

- = VISENx CSN × 32/3.08

- =  $I_{MON\_SLOPE} \times R_{IMON} \times I_{L\_OC} \times 32/3.08$  (Current Type DRMOS)

- = V<sub>MON\_SLOPE</sub> x R<sub>IMON2</sub>/(R<sub>IMON1</sub>+R<sub>IMON2</sub>)×IL\_OC×32/3.08 (Voltage Type DRMOS)

Richtek provides a Microsoft Excel-based design tool to help design desired per-phase current-limit threshold.

Figure 16. PINSET1 without NTC Network

## **AC Droop**

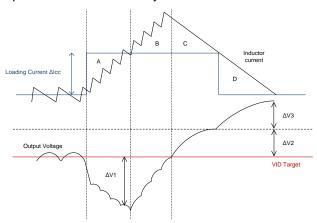

The RT8843C adopts a new feature, i.e. AC-droop, to effectively suppress load transient ring back and to control overshoot well for zero loadline application. Figure 17 shows the condition without AC-droop control. The output voltage without AC-droop control has extra ring back  $\Delta$ V2 due to C area charge.

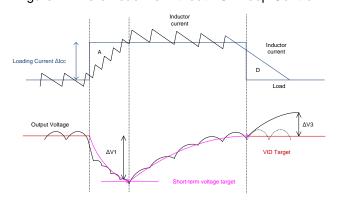

Figure 18 shows the condition with AC-droop control. While loading occurs, the controller temporarily changes VID target to short-term voltage target. Short-term voltage target is related to transient loading current  $\Delta$ Icc and can be represented as the following:

Short\_Term\_Voltage\_Target = Vcs x 9 x AI

Where the Vcs is the current sensing signal from DCR sensing or SPS current sensing. For DCR sensing, the Vcs = Icc\_Max x DCR. The current gain (AI) can be set by Pin Setting of AI Gain. Users can select AI gain according to Table 8 to set desired short term voltage target. The short-term voltage target reverts to VID target slowly after approximately  $100\mu s$ . The short-term voltage target can help inductor current not to exceed loading current too much and then the ring back can be suppressed. Referring to Figure 18, the overshoot amplitude is reduced to only  $\Delta V3$ .

Figure 17. Zero Loadline without AC-Droop Control

Figure 18. Zero Loadline with AC-Droop Control

## **Table 8. Pin Setting of AI Gain**

| Al Gain [1:0] | Gain Value |  |  |  |  |

|---------------|------------|--|--|--|--|

| 00            | Disable    |  |  |  |  |

| 01            | 1/16       |  |  |  |  |

| 10            | 2/16       |  |  |  |  |

| 11            | 4/16       |  |  |  |  |

# **Overvoltage Protection**

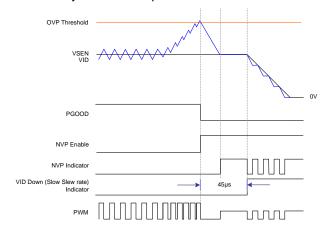

The output voltage can be continuously monitored through VSEN pin for overvoltage protection. If REFIN voltage is lower than 1.33V, the overvoltage threshold follows to absolute overvoltage 2V. If REFIN voltage is higher than 1.33V, the overvoltage threshold follows relative overvoltage 1.5 x VREFIN. The OV protection mechanism is illustrated in Figure 19. When OVP is triggered with 5µs filter time, the controller de-asserts PGOOD and starts NVP function. After NVP is enabled, the controller controls PWM as low when VSEN is higher than VID. When VSEN is lower than VID, PWM is controlled in tri-state to prevent large negative inductor current that may damage MOSFETs or driver. After 45µs from OVP trigger, VID starts to ramp down to 0V with slow slew rate. During the period, PWMx is not allowed to turn on. The controller controls PWMx to be low or tri-state to pull down the output voltage with VID. The OVP is latch mode protection, and it can be released by VCC or EN power-on reset.

Figure 19. Overvoltage Protection Mechanism

The RT8843C reduces the on-time by pulling the PWM low when VSEN is higher than REFIN + 28mV to prevent overcharging of the output capacitor. Therefore, output voltage overshoot is reduced. When zero current (ZC) is detected, the on-time reduction threshold increases to REFIN + 36mV.

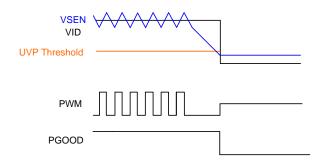

# **Undervoltage Protection**

The output voltage can be continuously monitored through VSEN pin for undervoltage protection. When the output voltage is less than UVP threshold with  $3\mu s$  filter time, the controller de-asserts PGOOD and controls all PWMs to tri-state to turn off high-side and

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

low-side power MOSFETs. During soft-start, the UVP blanking time is equal to PGOOD blanking time.

Figure 20. Undervoltage Protection Mechanism

## **Inductor Selection**

The switching frequency and ripple current determine the inductor value as follows:

$$L(MIN) = \frac{VIN - VOUT}{IRIPPLE(MAX)} \times TON$$

where Ton is the UGATE turn on period.

Higher inductance results in lower ripple current, which means the lower power loss. However, the inductor current rising time increases with inductance value. This means the transient response will be slower. Therefore, the inductor design is a trade-off between performance, size and cost.

The RT8843C supports inductor DCR sensing for loop control, zero-current-detection, current balance and per-phase current limiting. For ensuring the accuracy of DCR sensing signal, the minimum DC resistance of inductor must be greater than  $0.2m\Omega$ . The core must be large enough to prevent inductor saturation at heavy load condition.

## **Output Capacitor Selection**

The selection of Cout is determined by considering to satisfy the voltage ripple, the transient loads and to ensure that control loop is stable. Loop stability can be checked by viewing the load transient response. The peak-to-peak output ripple,  $\Delta$ Vout, is characterized by two components, which are ESR ripple  $\Delta$ VP-P\_ESR and capacitive ripple  $\Delta$ VP-P\_C, can be expressed as below:

$$\Delta VOUT = \Delta VP - P ESR + \Delta VP - P C$$

$$\Delta VP - P_ESR = \Delta IL \times RESR$$

$$\Delta VP - P_C = \frac{\Delta IL}{8 \times COUT \times fSW}$$

Where the  $\Delta IL$  is the peak-to-peak inductor ripple current and RESR is the equivalent series resistance of Cout. The output ripple is highest at maximum input voltage since  $\Delta IL$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements.

Regarding to the transient loads, the VSAG and VSOAR requirement should be taken into consideration for choosing the output capacitance value. The amount of output sag is a function of the maximum duty factor, which can be calculated from the on-time and minimum off-time.

$$ton = \frac{Vout}{Vin \times fsw}$$

$$DMAX = \frac{tON}{tON + tOFF\_MIN}$$

The worst-case output sag voltage can be determined by:

$$\Delta VOUT\_SAG = \frac{L \times (IL\_PEAK)^2}{2 \times COUT \times (VIN \times DMAX - VOUT)}$$

The amount of overshoot due to stored inductor energy when the load is removed can be calculated as:

$$\Delta V_{OUT\_SOAR} = \frac{L \times (I_{L\_PEAK})^2}{2 \times C_{OUT} \times V_{OUT}}$$

Ceramic capacitors have very low equivalent series resistance (ESR) and provide the best ripple performance. Choose X5R and X7R dielectric formulations. These dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size. Be careful to consider the voltage coefficient of ceramic capacitors when choosing the value and case size. Most ceramic capacitors lose 50% or more of their rated value when used near their rated voltage.

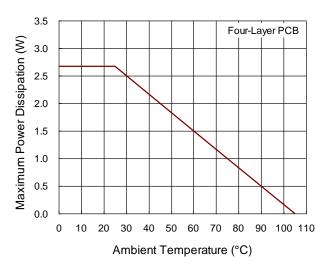

## **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature T<sub>J</sub>(MAX), listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$PD(MAX) = (TJ(MAX) - TA)/\theta JA$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_{A}$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 105°C. The junction-to-

ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WQFN-20L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 30°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated as below:

$P_{D(MAX)} = (105^{\circ}C - 25^{\circ}C)/(30^{\circ}C/W) = 2.67W$  for a WQFN-20L 3x3 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 21 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 21. Derating Curve of Maximum Power Dissipation

# **Layout Considerations**

Careful PCB layout is critical to achieving low switching losses and clean, stable operation. The switching power stage requires particular attention. If possible, mount all of the power components on the top side of the board with their ground terminals flushed against one another. Follow these guidelines for optimum PCB layout:

- ► Keep the high current paths short, especially at the ground terminals.

- ► Keep the power traces and load connections short. This is essential for high efficiency.

- ▶ When trade-offs in trace lengths must be made, it is preferable to allow the inductor charging path to be made longer than the discharging path.

- ▶ Place the current sense components close to the controller. ISENx and CSN connections for current limit and voltage positioning must be made by using Kelvin sense connections to guarantee the current sense accuracy. The PCB trace from the sense nodes should be paralleled back to the controller.

- ► Route high speed switching nodes away from sensitive analog areas (PINSETx, ISENx, Csn, Vsen, FBRTN, etc.)

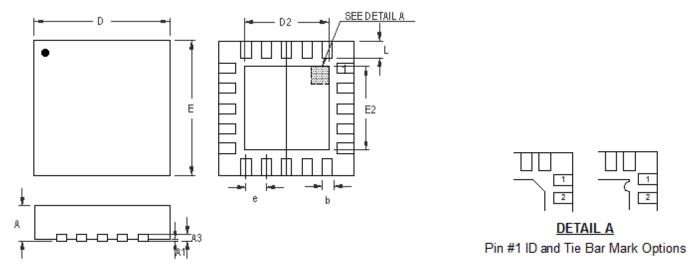

# **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Comple of | Dimensions I | In Millimeters | Dimensions In Inches |       |  |  |

|-----------|--------------|----------------|----------------------|-------|--|--|

| Symbol    | Min          | Max            | Min                  | Max   |  |  |

| А         | 0.700        | 0.800          | 0.028                | 0.031 |  |  |

| A1        | 0.000        | 0.050          | 0.000                | 0.002 |  |  |

| A3        | 0.175        | 0.250          | 0.007                | 0.010 |  |  |

| b         | 0.150        | 0.250          | 0.006                | 0.010 |  |  |

| D         | 2.900        | 3.100          | 0.114                | 0.122 |  |  |

| D2        | 1.650        | 1.750          | 0.065                | 0.069 |  |  |

| Е         | 2.900        | 3.100          | 0.114                | 0.122 |  |  |

| E2        | 1.650        | 1.750          | 0.065                | 0.069 |  |  |

| е         | 0.4          | 100            | 0.0                  | )16   |  |  |

| L         | 0.350        | 0.450          | 0.014                | 0.018 |  |  |

W-Type 20L QFN 3x3 Package

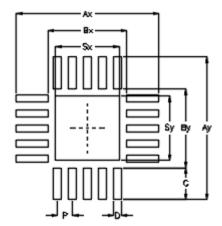

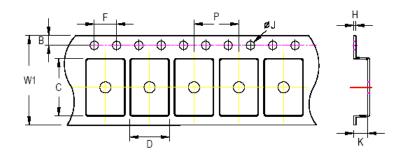

# **Footprint Information**

|                  | Number of | Footprint Dimension (mm) |      |      |      |      |      |      |      | Toloropoo |           |

|------------------|-----------|--------------------------|------|------|------|------|------|------|------|-----------|-----------|

| Package          | Pin       | Р                        | Ax   | Ay   | Вх   | Ву   | С    | D    | Sx   | Sy        | Tolerance |

| V/W/U/XQFN3*3-20 | 20        | 0.40                     | 3.80 | 3.80 | 2.10 | 2.10 | 0.85 | 0.20 | 1.70 | 1.70      | ±0.05     |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

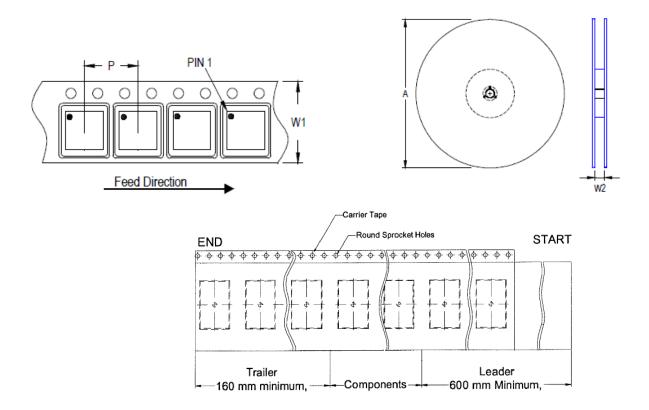

# **Packing Information**

# **Tape and Reel Data**

| Dankana Tura   | Tape Size | Pocket Pitch | Reel Size (A) |      | Units    | Trailer | Leader | Reel Width (W2) |  |

|----------------|-----------|--------------|---------------|------|----------|---------|--------|-----------------|--|

| Package Type   | (W1) (mm) | (P) (mm)     | (mm)          | (in) | per Reel | (mm)    | (mm)   | Min./Max. (mm)  |  |

| QFN/DFN<br>3x3 | 12        | 8            | 180           | 7    | 1,500    | 160     | 600    | 12.4/14.4       |  |

- C, D and K are determined by component size.

The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | Р     |       | В      |        | F     |       | Ø٦    |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|

| Tape Size | Max.   | Min.  | Max.  | Min.   | Max.   | Min.  | Max.  | Min.  | Max.  | Max.  |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.6mm |

# **Tape and Reel Packing**

| Step | Photo/Description                      | Step | Photo/Description            |

|------|----------------------------------------|------|------------------------------|

| 1    | Reel 7"                                | 4    | 3 reels per inner box Box A  |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A           |

| Container     | R                        | teel  | Вох           |               |       |          |                               | Carton   |        |      |

|---------------|--------------------------|-------|---------------|---------------|-------|----------|-------------------------------|----------|--------|------|

| Package       | Size                     | Units | Item          | Size(cm)      | Reels | Units    | Item                          | Size(cm) | Boxes  | Unit |

| OEN 8 DEN 2v2 |                          | Box A | 18.3*18.3*8.0 | 3             | 4,500 | Carton A | 38.3*27.2*38.3                | 12       | 54,000 |      |

| QFN & DFN 3X3 | 'N & DFN 3X3   /   1,500 |       | Box E         | 18.6*18.6*3.5 | 1     | 1,500    | For Combined or Partial Reel. |          |        |      |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation DS8843C-00 July 2023 www.richtek.com

# **Packing Material Anti-ESD Property**

| Surface<br>Resistance     | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|---------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega$ /cm <sup>2</sup> | 10 <sup>4</sup> to 10 <sup>11</sup> |

# **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

# **Datasheet Revision History**

| Version | Date      | Description | ltem |

|---------|-----------|-------------|------|

| 00      | 2023/7/10 | Final       |      |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation DS8843C-00 July 2023