# 5V to 12V Single Synchronous Buck PWM Controller with Reference Input

### **General Description**

The RT8109 is a single-phase synchronous buck PWM DC-DC controller designed to drive two N-MOSFETs. It provides a highly accurate, programmable output voltage precisely regulated to low voltage requirement with an internal  $0.6V \pm 1\%$  reference.

The RT8109 uses a single feedback loop voltage mode PWM control for fast transient response. The high driving capability makes it suitable for large output current applications. An oscillator with fixed frequency 300kHz reduces the component size of the external inductor and capacitor for saving PCB board area and cost.

The RT8109 supports both tracking and stand-alone loop control modes. Standalone mode is simple and tracking mode provides better flexibility. The RT8109 also integrates complete protection functions such as OCP, OVP, UVP into WDFN-10L 3x3 package.

# **Ordering Information**

RT8109

Package Type

QW : WDFN-10L 3x3 (W-Type)

Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

ER= : Product Code YMDNN : Date Code

### Features

- Single IC Supply Voltage (5V to 12V).

- Drive Two N-MOSFETs

- Fixed Operating Frequency at 300kHz

- Voltage Mode PWM Control with External Feedback Loop Compensation

- Over Current Protection by Sensing MOSFET RDS(ON)

- Dual Mode Regulation Control

Standalone Mode (FB regulating to close to internal reference 0.6V)

Tracking Mode (FB following PI input)

- Power Good Indication

- On/Off Control

- Full 0 to 90% Duty Cycle

- RoHS Compliant and Halgen Free

### Applications

- Mother Boards and Desktop Servers

- Graphic Cards

- Switching Power Supply

- Generic DC-DC Power Regulator

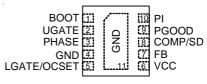

## **Pin Configurations**

(TOP VIEW)

WDFN-10L 3x3

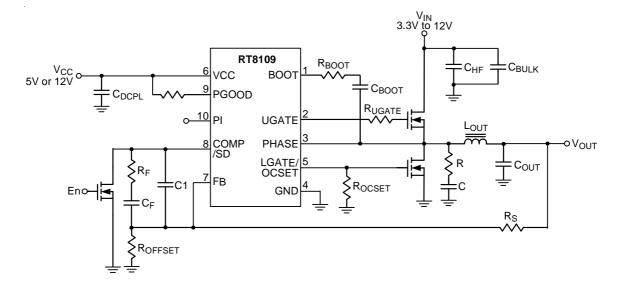

# **Typical Application Circuit**

## **Functional Pin Description**

| Pin No.                | Pin Name    | Pin Function                                                                                                                                                                                                                   |  |  |

|------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                      | воот        | Bootstrap Supply pin for the Upper Gate Driver. Connect the bootstrap capacitor between BOOT and PHASE pins.                                                                                                                   |  |  |

| 2                      | UGATE       | Upper Gate Driver Output. Connect to gate of the high side power N-MOSFET.                                                                                                                                                     |  |  |

| 3                      | PHASE       | Connect this pin to the Source of the Upper MOSFET and the Drain of the Lower MOSFET.                                                                                                                                          |  |  |

| 4,<br>11 (Exposed Pad) | GND         | Signal and Power Ground for the IC. Tie this pin directly to the low-s MOSFET source and ground plane with the lowest impedance. T exposed pad must be soldered to a large PCB and connected to GND maximum power dissipation. |  |  |

| 5                      | LGATE/OCSET | <ul> <li>Low-Side Gate Drive. It also acts as over current setup pin by adjusting th<br/>resistor connecting to GND.</li> </ul>                                                                                                |  |  |

| 6                      | VCC         | Connect this Pin to a Well-Decoupled 5V or 12V Bias Supply. It is also the positive supply for the lower gate driver.                                                                                                          |  |  |

| 7                      | FB          | Feedback of the Output Voltage.                                                                                                                                                                                                |  |  |

| 8                      | COMP/SD     | Feedback Compensation and Enable/Shutdown Control Pin.                                                                                                                                                                         |  |  |

| 9                      | PGOOD       | Open Drain Output. This pin is used to indicate the output is regulated to within power good thresholds.                                                                                                                       |  |  |

| 10                     | PI          | External Reference Input. The RT8109 will regulate FB to close to PI voltage in Tracking Mode.                                                                                                                                 |  |  |

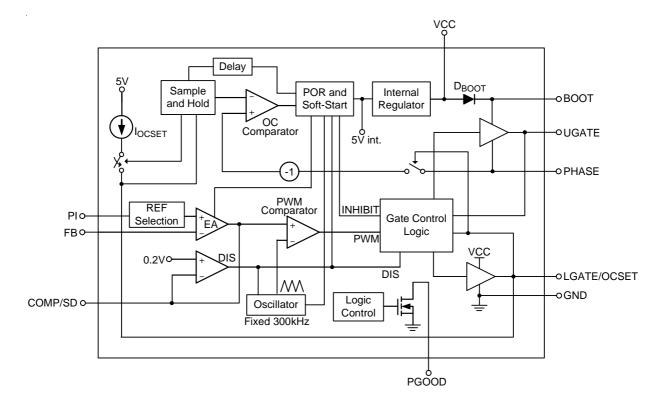

# **Function Block Diagram**

# Absolute Maximum Ratings (Note 1)

| <ul> <li>Supply Input Voltage, V<sub>CC</sub></li> <li>BOOT to PHASE</li> <li>BOOT to GND</li> </ul>                   |                                       |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| DC                                                                                                                     |                                       |

| DC<br><200ns                                                                                                           | 5V to 30V                             |

| <ul> <li>UGATE Voltage</li> <li>&lt;200ns</li> <li>LGATE Voltage</li> </ul>                                            | - $V_{PHASE} - 5V$ to $V_{BOOT} + 5V$ |

| <ul> <li>CGATE voltage</li> <li>&lt;200ns</li> <li>Other Input or Output Voltages</li> </ul>                           | - GND – 5V to $V_{CC}$ + 5V           |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$<br>WDFN-10L 3x3                                                         |                                       |

| <ul> <li>Package Thermal Resistance (Note 2)<br/>WDFN-10L 3x3, θ<sub>JA</sub></li> <li>Junction Temperature</li> </ul> |                                       |

| <ul> <li>Lead Temperature (Soldering, 10 sec.)</li> <li>Storage Temperature Range</li> </ul>                           | - 260°C                               |

| ESD Susceptibility (Note 3)     HBM (Human Body Mode) MM (Machine Mode)                                                |                                       |

## Recommended Operating Conditions (Note 4)

| Supply Input Voltage, V <sub>CC</sub> | $5V\pm5\%,12V\pm10\%$ |

|---------------------------------------|-----------------------|

| Junction Temperature Range            | –40°C to 125°C        |

Ambient Temperature Range ------- -40°C to 85°C

### **Electrical Characteristics**

(V\_CC = 12V, T\_A = 25°C, unless otherwise specified)

| Parameter                 | Symbol              | Test Conditions        | Min  | Тур | Мах  | Unit |  |  |

|---------------------------|---------------------|------------------------|------|-----|------|------|--|--|

| Supply Input              | Supply Input        |                        |      |     |      |      |  |  |

| Supply Input Voltage      | V <sub>CC</sub>     |                        | 4.75 |     | 13.2 | V    |  |  |

| Supply Current            | Icc                 | UGATE, LGATE Open      |      | 2.5 | 10   | mA   |  |  |

| Shutdown Current          | I <sub>SHDN</sub>   | UGATE, LGATE Open      |      | 2   |      | mA   |  |  |

| Power-On Reset            |                     |                        |      |     |      |      |  |  |

| POR Threshold             | V <sub>CC_RTH</sub> | V <sub>CC</sub> Rising | 3.8  | 4   | 4.3  | V    |  |  |

| Power On Reset Hysteresis | V <sub>CC_HYS</sub> |                        |      | 0.4 |      | V    |  |  |

| <b>RT81</b> | 09 |

|-------------|----|

|-------------|----|

| Parameter                             | Symbol               | Test Conditions                       | Min   | Тур | Max   | Unit |

|---------------------------------------|----------------------|---------------------------------------|-------|-----|-------|------|

| Oscillator                            | -                    |                                       |       |     |       |      |

| PWM Frequency                         | Fsw                  |                                       | 250   | 300 | 350   | kHz  |

| Ramp Amplitude                        | ΔVosc                |                                       |       | 1.5 |       | Vp-p |

| Internal Reference (Standalone        | e Mode)              |                                       |       |     |       |      |

| Internal Reference Voltage            | V <sub>REF</sub>     |                                       | 0.594 | 0.6 | 0.606 | V    |

| External Reference (Tracking I        | Mode)                |                                       |       |     |       |      |

| Input Range                           |                      |                                       | 0.4   |     | 3     | V    |

| Input Offset                          |                      |                                       | -10   | 0   | 10    | mV   |

| PWM Controller                        |                      |                                       |       |     |       |      |

| Open Loop DC Gain                     | Ao                   |                                       |       | 88  |       | dB   |

| Gain Bandwidth                        | GBW                  |                                       |       | 15  |       | MHz  |

| Maximum Duty                          | D <sub>MAX</sub>     |                                       |       | 90  |       | %    |

| PWM Controller Gate Driver            |                      |                                       |       |     |       |      |

| Upper Gate Source                     | IUGATEsr             | VBOOT – VPHASE = 12V                  | 1     | 1.2 |       | А    |

| Upper Gate Sink                       | RUGATEsk             | VUGATE – VPHASE = 0.1V, IUG = 50mA    |       | 2   |       | Ω    |

| Lower Gate Source                     | ILGATEsr             | V <sub>CC</sub> = 12V                 | 1     | 1.2 |       | А    |

| Lower Gate Sink                       | R <sub>LGATEsk</sub> | $V_{LGATE} = 0.1V$ , $I_{LG} = 50mA$  |       | 1   |       | Ω    |

| Internal BOOT Switch                  |                      |                                       |       |     |       |      |

| Internal BOOT Switch<br>On-Resistance | R <sub>BOOT</sub>    | VCC to BOOT, 5mA                      |       |     | 80    | Ω    |

| Protection                            |                      |                                       |       |     |       |      |

| Under Voltage Protection (UVP)        | Vfb_uvp              | Sweep V <sub>FB</sub>                 | 68    | 75  | 82    | %    |

| Over Voltage Protection               | V <sub>FB_OVP</sub>  | Sweep V <sub>FB</sub>                 | 115   | 125 | 130   | %    |

| LGATE OC Setting Current              | IOCSET               |                                       | 22    | 25  | 28    | μΑ   |

| Over Temperature Protection           | T <sub>OTP</sub>     |                                       |       | 170 |       | °C   |

| Soft Start Interval                   | Tss                  | PI = 0.6V, Measure FB from 10% to 90% | 1     | 3   | 5     | ms   |

| COMP/SD Shutdown Threshold            | VSD                  |                                       |       | -   | 0.2   | V    |

Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended. The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

- Note 4. The device is not guaranteed to function outside its operating conditions.

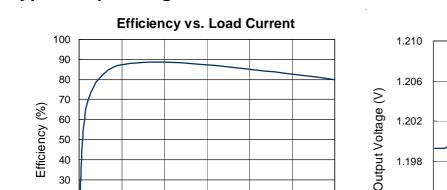

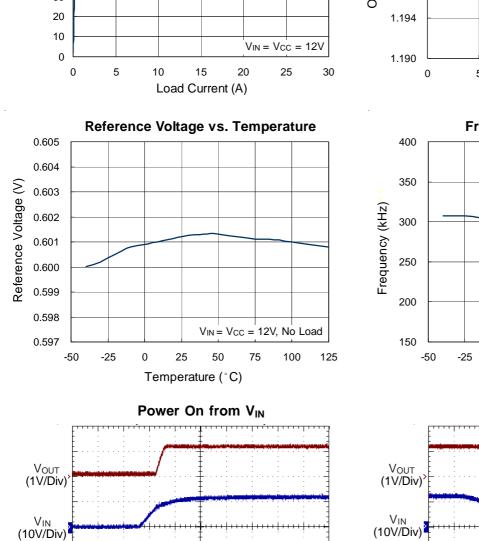

**Output Voltage vs. Load Current**

# **Typical Operating Characteristics**

0

25

Temperature (°C)

50

Copyright ©2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

VIN = VCC = 12V, No Load

Time (4ms/Div)

V<sub>CC</sub> (10V/Div)

UGATE

(20V/Div)

VIN = VCC = 12V, No Load

100

125

75

# **RT8109**

RICHTEK

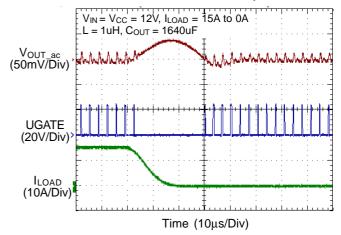

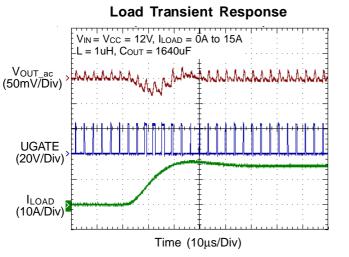

Load Transient Response

**Over Voltage Protection**

### **Application Information**

#### **Function Description**

The RT8109 is a single-phase synchronous buck PWM controllers with embedded MOSFET drivers. The MOSFET drivers are designed with high-current driving capability to support up to 12V+12V bootstrapped voltage for high efficiency power conversion. The RT8109 utilizes voltagemode control scheme, which is implemented with a voltage error amplifier to provide a simple control loop. A fixed 300kHz oscillator is integrated to eliminate external component count. The soft-start function is also integrated to eliminate the external timing capacitor. The RT8109 provides full protection functions to protect the load. The feedback voltage at the FB pin is monitored for over-voltage protection and under-voltage protection. An internal 0.6V reference allows the output voltage to be precisely regulated for low output voltage applications. An elaborately designed control circuit allows the converter to power up with pre-biased output voltage and to avoid negative voltage to damage the load. The RT8109 uses R<sub>DS(ON)</sub> current-sensing technique, which is lossless and cost-effective. Inductor current information is monitored by the voltage across R<sub>DS(ON)</sub> of the low-side MOSFET for over current protection.

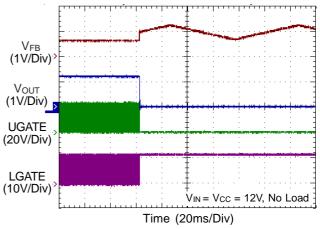

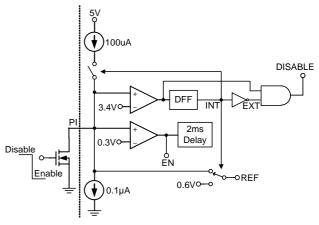

#### **External Reference Input**

The RT8109 supports external reference input to provide more flexible applications. The PI pin is implemented to be external reference input and chip enable function. The mode selection is determined and latched in 2ms delay time after chip enabling. If PI pin is floating, a 100uA current source will pull high the PI pin for chip enable, FB pin will follow the internal reference voltage 0.6V. If an external voltage is applied to PI pin, the RT8109 enters tracking mode and regulates FB to be close to this voltage. The applied voltage must be within the tracking range (typically between 0.4V to 3.3V, see Electrical Characteristics). Once the applied voltage exceeds 3.4V, both UGATE and LGATE will go low to protect the load until the applied voltage is under 3.3V, and then controller will return to tracking mode. If the applied voltage is less than 0.3V, the controller will be shut down.

stage can not well follow it and easy to trigger OVP, UVP or OCP. Applying external voltage to PI pin through a low pass filter could slow down the slew rate and get safety PI transition.

Figure 1. Reference Selection

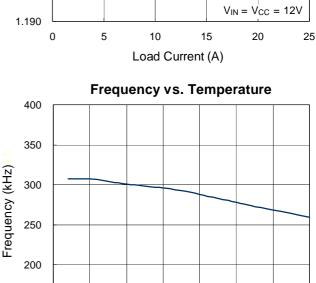

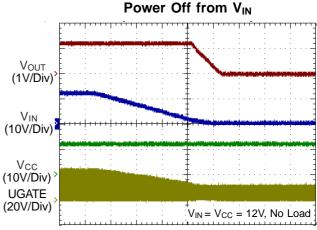

#### Power-up

The power on reset (POR) circuit monitors the supply voltage of the controller (VCC). If VCC exceeds the POR rising threshold voltage, the controller is initiated. The controller sets the over current protection threshold prior to the beginning of soft start. If VCC falls below the POR falling threshold during normal operation, all MOSFETs stop switching and the controller is reset. The POR rising and falling threshold has a hysteresis to prevent noisecaused reset.

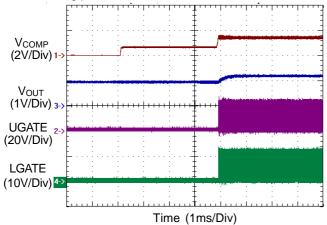

#### Soft-start

The RT8109 provides soft-start function internally. The softstart function is used to prevent the large inrush current while the converter is powered-up. An internal current source charges the internal soft-start capacitor such that the internal soft-start voltage ramps up in a monotone. The FB voltage will track the internal soft-start voltage during the soft-start interval. After the internal soft-start voltage exceeds the reference voltage, the FB voltage no longer tracks the soft-start voltage but follows the reference voltage. Therefore, the duty cycle of the UGATE signal at power up is limited and so does the input current.

#### **Power Good**

Once the output voltage exceeds power good threshold

During PI transition, too fast slew rate will cause the power

level (90% of output voltage), PGOOD pin will be tripped into high impedance state. Normally a pull-up resistor is connected between PGOOD and VCC.

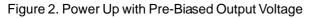

#### Power-Up with Pre-biased Voltage

Generally, if the output voltage is not initially zero at powerup, or the output capacitor is pre-charged, the voltage at FB pin is not equal to zero. The controller will turn on the low-side MOSFET to discharge the output capacitor, forcing the feedback voltage to follow the reference voltage. Large current is then drawn from the output capacitor while discharging. The discharge current depends on the inductance and the output capacitance. Output voltage may oscillate and be negative.

The negative output voltage could damage the load. The RT8109 implements elaborate control circuits to prevent the negative voltage when the converter is powered-up with pre-biased voltage on the output capacitor. Figure 2 shows the waveform that converter is powered-up at no load with pre-biased output voltage. The output voltage rises from its pre-charged initial value during soft-start without being pulled down.

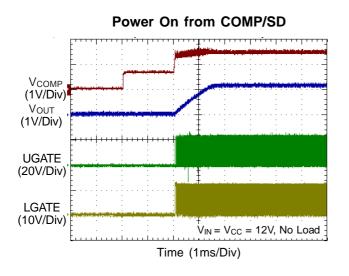

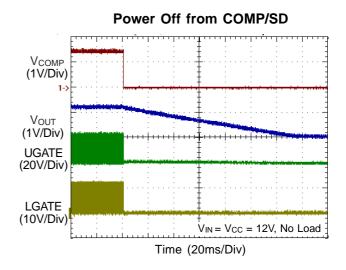

#### **COMP/SD Enable/Disable**

The COMP/SD pin can also be used to enable or to disable the controller. Pull down COMP/SD pin below the shutdown level  $V_{SD}$  can disable the controller. When the controller is disabled, UGATE signal goes low first and then LGATE signal also goes low after a short delay time. In practical applications, connect a small signal MOFSET to COMP/SD pin to pull down the COMP/SD voltage to implement the enable/disable function.

#### **Over Voltage Protection (OVP)**

The output voltage is scaled by the divider resistors and fed back to the FB pin. The voltage on the FB pin will be compared to the internal reference voltage  $V_{REF}$  for voltagerelated protection functions, including over voltage protection and under voltage protection. If the FB voltage is higher than the OVP threshold during operation, OVP will be triggered. When OVP is triggered, UGATE will go low and LGATE will go high to discharge the output capacitor. Once OVP is triggered, controller will be latched unless VCC POR is detected again.

#### **Under Voltage Protection (UVP)**

The voltage on the FB pin is also monitored for under voltage protection. If the FB voltage is lower than the UVP threshold during normal operation, UVP will be triggered. When UVP is triggered, both UGATE and LGATE go low. Unlike OVP, UVP is not a latched protection. The controller will begin soft start again after a specific period of time (40ms). Furthermore, the controller will enter the hiccup mode and always try to restart if UVP situation is not removed. The UVP is reset by detecting VCC POR again. Unlike OVP, the output voltage is monitored for UVP only after soft-start completes.

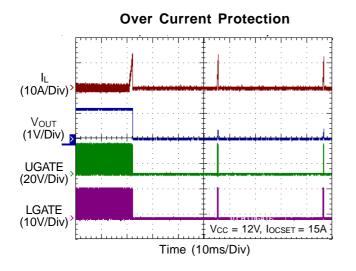

#### **Over Current Protection (OCP)**

The RT8109 senses output current through low-side MOSFET  $R_{DS(ON)}$  for over current protection. When the LGATE is turned on, the controller monitors voltage across the low-side MOSFET. The lossless  $R_{DS(ON)}$  current sensing technique is cost-effective, because no external component is required. The RT8109 utilizes cycle-by-cycle peak current sensing, the voltage across the low-side MOSFET is sampled and held after low-side MOSFET is turned on. This sampled and held voltage represents the inductor peak current and is compared to the user-programmed protection level.

Once the inductor current exceeds the protection level, OCP will be triggered. When the OCP is triggered, both UGATE and LGATE go low to stop the energy transferring to the load. Like UVP, the OCP is a continuing hiccupped protection. The soft start will be initiated again after a specific period of time (4\*Tss, typical). If OCP situation is not removed, controller will always try to restart.

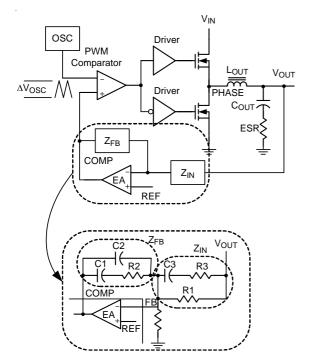

#### **OCP Setting**

The RT8109 employs an elaborate topology for OCP setting, which eliminates controller pin count. Connect a resistor from LGATE to GND to set the OCP level as shown in Figure 3.

Figure 3. OCP Setting

When the V<sub>CC</sub> exceeds the POR threshold at power up, LGATE is internally floating and enters tri-state. An internal current source  $I_{OCSET}$  then flows through  $R_{OCSET}$  to determine the OCP threshold voltage. The voltage across the  $R_{OCSET}$  is stored as the over current level for OCP. After that, the current source is switched off, and LGATE leaves the tri-state and prepared for the soft-start. Therefore, no extra pin is required to set the OCP threshold. The internal current source  $I_{OC}$  is only active for a short period of time after  $V_{CC}$  POR. The  $R_{OCSET}$  can be determined using the following equation.

$\mathsf{R}_{\mathsf{OCSET}} = \frac{\mathsf{R}_{\mathsf{DS}(\mathsf{ON})} \times \mathsf{I}_{\mathsf{MAX}}}{2 \, \mathsf{x} \, \mathsf{I}_{\mathsf{OCSET}}}$

where  $I_{\text{OCSET}}$  is  $25\mu A$  (typical),  $I_{\text{MAX}}$  represents the allowed maximum inductor peak current.

#### **MOSFET Drivers**

The RT8109 integrates high-current gate drivers for MOSFETs to obtain high-efficiency power conversion in synchronous buck topology. A dead time is used to prevent the crossover conduction for the high-side and low-side MOSFETs. Because both the two gate signals are off during the dead time, the inductor current freewheels through the body diode of the low-side MOSFET. The freewheeling current and the forward voltage of the body diode contribute to the power loss. The RT8109 employs a constant dead time control scheme to ensure safe operation without sacrificing efficiency. Furthermore, an elaborate logic circuit is implemented to prevent the crossconduction between MOSFETs.

For high output current applications, two or more power MOSFETs are paralleled to have reduced  $R_{DS(ON)}$ . The gate driver needs to provide more current to switch on/off these paralleled MOSFETs. Gate driver with lower source/ sink current capability results in longer rising/ falling time in gate signals, and therefore the higher switching loss.

RT8109 employs embedded high-current gate drivers to obtain high-efficiency power conversion. The embedded drivers contribute to the majority of the controller's power dissipation. If no gate resistor is used, the power dissipation of the controller can be approximately calculated using the following equation.

$$\label{eq:psw} \begin{split} \mathsf{P}_{SW} = \mathsf{F}_{SW} \; x \; (\mathsf{Q}_{g\_High-Side} \; x \; \mathsf{V}_{\mathsf{BOOT}} + \mathsf{Q}_{g\_Low-Side} \\ & x \; \mathsf{V}_{\mathsf{Drive\_Low-Side}} \; ) \end{split}$$

, where  $V_{\mbox{\scriptsize BOOT}}$  represents the voltage across the bootstrap capacitor.

It is important to ensure the package can dissipate the switching loss and have enough room for safe operation.

#### **Inductor Selection**

Inductor plays an importance role in the buck converter because the energy from the input power rail is stored in it and then released to the load. From the viewpoint of efficiency, the dc resistance (DCR) of inductor should be as small as possible because inductor carries current all the time. Using inductor that has lower DCR can obtain higher efficiency. In addition, because inductor cost most of the board space, its size is also important. Low profile inductors can save board space especially when the height has limitation.

Additionally, larger inductance results in lower ripple current, and therefore the lower power loss. However, the inductor current rising time increases with inductance value. This means the inductor will have a longer charging time before its current reaches the required output current. Since the response time is increased, the transient response performance will be decreased. Therefore, the inductor design is a trade-off between performance, size and cost.

In general, inductance is designed such that the ripple current ranges between 20% to 30% of full load current. The inductance can be calculated using the following equation.

$$L_{MIN} = \frac{V_{IN} - V_{OUT}}{F_{SW} \times k \times I_{OUT}_{Full \ Load}} \times \frac{V_{OUT}}{V_{IN}}$$

where k is 0.2 to 0.3.

#### Input Capacitor Selection

Voltage rating and current rating are the key parameters in selecting input capacitor. The voltage rating must be 1.25 times greater than the maximum input voltage to ensure enough room for safe operation. Generally, input capacitor has a voltage rating of 1.5 times greater than the maximum input voltage is a conservatively safe design.

The input capacitor is used to supply the input RMS current, which can be approximately calculated using the following equation.

$$I_{RMS} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

Refer to the manufacturer's databook for RMS current rating to select proper capacitor. Use more than one capacitor with low equivalent series resistance (ESR) in parallel to form a capacitor bank is popular. Besides, placing ceramic capacitor close to the drain of the high-side MOSFET is helpful in reducing the input voltage ripple at heavy load.

#### **Output Capacitor Selection**

The output capacitor and the inductor form a low-pass filter in the buck topology. The electrolytic capacitor is usually used because it can provide large capacitance value. In steady state condition, the output capacitor supplies only AC ripple current to the load. The ripple current flows into/ out of the capacitor results in ripple voltage, which can be determined using the following equation.

$\Delta V_{OUT\_ESR} = \Delta I_L x ESR$

In addition, the output voltage ripple is also influenced by the switching frequency and the capacitance value.

$$\Delta V_{OUT\_C} = \Delta I_L \times \frac{1}{8 \times C_{OUT} \times F_{SW}}$$

The total output voltage ripple is the sum of  $V_{\text{OUT}\_\text{ESR}}$  and  $V_{\text{OUT}\_\text{C}}.$

If the specification for steady-state output voltage ripple is known, the ESR can be determined using the above equations.

Another parameter that has influence on the output voltage undershoot is the equivalent series inductance (ESL). The rapid change in load current results in di/dt during transient. Therefore, ESL contributes to part of the voltage undershoot. Use capacitor that has low ESL to obtain better transient performance. Generally, use several capacitors connected in parallel can have better transient performance than use single capacitor for the same total ESR.

Unlike the electrolytic capacitor, the ceramic capacitor has relatively low ESR and can reduce the voltage deviation during load transient. However, the ceramic capacitor can only provide low capacitance value. Therefore, use a mixed combination of electrolytic capacitor and ceramic capacitor can also have better transient performance.

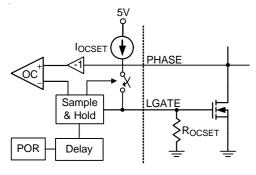

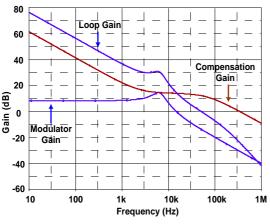

#### Feedback Loop Compensation

Figure 4 shows the voltage mode control loop for a buck converter. The control loop consists of the modulator, output LC filter and the compensator. The modulator is composed of the PWM comparator and power MOSFETs. The PWM comparator compares the error amplifier EA output (COMP) with the oscillator (OSC) sawtooth wave to generate a PWM signal. The MOSFETs is then switched on and off according to the duty cycle of the PWM signal. The voltage presented at PHASE node is a square wave of 0V to Vin.

The PHASE voltage is filtered by the output filter  $L_{OUT}$  and  $C_{OUT}$  to produce output voltage  $V_{OUT}$ , which is fedback to the inverting input of the error amplifier. The output voltage is then regulated according to the reference voltage  $V_{REF}$ .

In order to achieve fast transient response and accurate output regulation, an adequate compensator design is necessary. The goal of the compensation network is to provide adequate phase margin (greater than 45 degrees) and the highest 0dB crossing frequency. It is also recommended to manipulate loop frequency response that its gain crosses over 0dB at a slope of –20dB/dec.

# **RT8109**

Figure 4. Control Loop for Voltage Mode Buck Converter

#### 1) Modulator and Output LC filter

Referring to Figure 4, the modulator gain is the input voltage  $V_{IN}$  divided by the peak to peak oscillator voltage  $V_{OSC}$  as shown as following Equation :

$$\label{eq:ModulatorGain} \begin{split} \text{Modulator}_{\text{Gain}} &= \frac{V_{\text{IN}}}{\Delta V_{\text{OSC}}} \\ \text{where } \Delta V_{\text{OSC}} = 1.5 \text{V} \text{ (typ.)} \end{split}$$

The output LC filter introduces a double pole to the transfer function, creating –40dB/decade gain slope above its corner frequency, with a phase lag of 180 degrees. The frequency at the double-pole of LC filter is expressed as follows.

$$f_{LC} = \frac{1}{2\pi \times \sqrt{L_{OUT} \times C_{OUT}}}$$

In addition, the ESR of the output capacitor introduces a zero to the transfer function, creating a +20dB/dec gain slope with a phase shift of 90 degree. The frequency of the ESR zero is expressed as follows.

$$fESR = \frac{1}{2\pi \times ESR \times COUT}$$

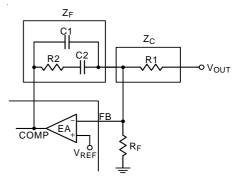

#### 2) Compensator

Fugire 4 illustrates the type II compensator, which consists of the error amplifier and the impedance  $Z_C$  and  $Z_F$ .

Figure 5. Type II Compensator

Type II compensator provides two poles and one zero to the system. The first pole is located at low frequency to increase the dc gain for regulation accuracy. The location of the other pole and the zero is expressed as follows.

$$f_{Z1} = \frac{1}{2\pi \times R2 \times C2}$$

$$f_{P1} = \frac{1}{2\pi \times R2 \times \frac{C1 \times C2}{C1 + C2}}$$

Figure 6 shows the Bode plot for the gain of system. The compensation gain determined by Z<sub>C</sub> and Z<sub>F</sub> should be designed to have high crossover frequency (bandwidth) with sufficient phase margin. In order to make the gain crosses over 0dB at a slope of -20dB/dec, place the zero before the LC double-pole frequency. Empirically, f<sub>z1</sub> is placed at 75% of the LC double-pole frequency. Furthermore, the bandwidth of the system is the factor that affects the converter's transient performance. High bandwidth results in fast transient response, but it often jeopardizes the system stability. The bandwidth should be designed to be less than 1/5 of the switching frequency. Properly adjust R1 and R2 to change the mid-frequency gain to obtain the required bandwidth. The pole at fp1 is usually placed at half of the switching frequency to have sufficient phase margin and attenuation at high frequency.

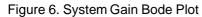

#### Layout Considerations

PCB layout is critical to high-current high-frequency switching converter designs. A good layout can help the controller to function properly and achieve expected performance. On the other hand, PCB without a carefully layout can radiate excessive noise, having more power loss and even malfunction in the controller. In order to avoid the above condition, the following general guidelines must be followed in PCB layout.

- Power stage components should be placed first. Place the input bulk capacitors close to the high-side power MOSFETs, and then locate the output inductor and finally the output capacitors.

- Place the ceramic capacitor physically close to the drain of the high-side MOSFET. This can reduce the input voltage drop when high-side MOSFET is turned on. If more than one MOSFET is paralleled, each should have its own individual ceramic capacitor.

- Keep the high-current loops as short as possible. During high speed switching, the current transition between MOSFETs usually causes di/dt voltage spike due to the parasitic components on PCB trace. Therefore, making the trace length between power MOSFETs and inductors wide and short can reduce the voltage spike and EMI.

- Make MOSFET gate driver path as short as possible. Since the gate driver uses narrow-width high-current pulses to switch on/off the power MOSFET, the driver path must be short to reduce the trace inductance. This is especially important for low-side MOSFET, because this can reduce the possibility of shoot-through.

- Providing enough copper area around the power MOSFETs to help heat dissipation. Using thick copper also reduces the trace resistance and inductance to have better performance.

- The output capacitors should be placed physically close to the load. This can minimize the trace parasitic components and improve transient response.

- All small signal components should be located close to the controller. The small signal components include the feedback voltage divider resistors, compensator, function setting components and high-frequency bypass capacitors. The feedback voltage divider resistor and the compensator must be placed close to FB pin and COMP pin, because these pins are inherently noise-sensitive.

- Voltage feedback path must be keep away from the switching nodes. The noisy switching node is, for example, the interconnection between high-side MOSFET, low-side MOSFET and inductor. The feedback path must be kept away from this kind of noisy node to avoid noise pick-up.

- A multi-layer PCB design is recommended. Make use of one single layer as the ground and have separate layers for power rail or signal that is suitable for PCB design.

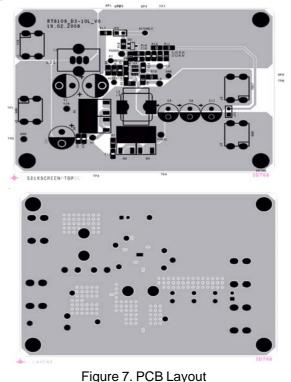

### **Outline Dimension**

#### DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| А      | 0.700      | 0.800          | 0.028                | 0.031 |  |

| A1     | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b      | 0.180      | 0.300          | 0.007                | 0.012 |  |

| D      | 2.950      | 3.050          | 0.116                | 0.120 |  |

| D2     | 2.300      | 2.650          | 0.091                | 0.104 |  |

| E      | 2.950      | 3.050          | 0.116                | 0.120 |  |

| E2     | 1.500      | 1.750          | 0.059                | 0.069 |  |

| е      | 0.500      |                | 0.0                  | )20   |  |

| L      | 0.350      | 0.450          | 0.014                | 0.018 |  |

W-Type 10L DFN 3x3 Package

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

#### RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.