# **RICHTEK**<sup>®</sup>

## RT5744/RT5746

Sample & Buy

## 2.4MHz 4A/6A Step-Down Converter with I<sup>2</sup>C Interface

### **1 General Description**

The RT5744 and RT5746 are step-down converters that deliver a digitally programmable output from an input voltage supply of 2.5V to 5.5V. The output voltage is programmed through an  $I^2C$  interface that can operate up to 3.4MHz.

Using a proprietary architecture with synchronous rectification, the RT5744 and RT5746 are capable of delivering continuous 4A and 6A, maintaining that efficiency at load currents as low as 10mA. The regulator operates at a nominal fixed frequency of 2.4MHz, which reduces the external component counts. Additional output capacitance can be added to improve regulation during load transients without affecting stability.

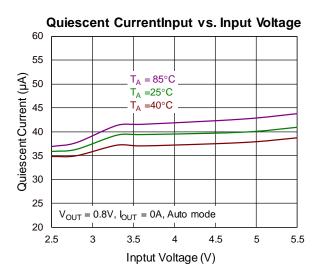

At moderate and light loads, Pulse Frequency Modulation (PFM) is used to operate in power-saving mode with a typical quiescent current of  $45\mu$ A at room temperature. Even with such a low quiescent current, the part exhibits excellent transient response during large load swings. At higher loads, the system automatically switches to fixed frequency control, operating at 2.4MHz. In shutdown mode, the supply current is typically  $0.1\mu$ A, and is excellent in reducing power consumption. The PFM mode can be disabled if the fixed frequency is desired. The RT5744 and RT5746 are available in WL-CSP-14B 1.31x2.02 (BSC) package. The recommended junction temperature range is  $-40^{\circ}$ C to  $125^{\circ}$ C. See <u>Ordering Information</u> for the key features of each part number.

### 2 Features

- Programmable Output Voltage Range from 0.27V to 1.4V, 6.25mV/bit

- Programmable Slew Rate for Voltage Transitions

- Steady 2.4MHz Switching Frequency

- Fast Load Transient

- Continuous Output Current Capability: 4A/6A

- 2.5V to 5.5V Input Voltage Range

- Digitally Programmable Output Voltage

- I<sup>2</sup>C-Compatible Interface up to 3.4Mbps

- PFM Mode for High Efficiency at Light Load

- Quiescent Current in PFM Mode: 45μA (Typical)

- Input Undervoltage-Lockout (UVLO)

- Over-Temperature Protection and Overload

Protection

- Power-Good Indicator

### **3** Applications

- Application, Graphic, and DSP Processors: ARM<sup>TM</sup>, Tegra<sup>TM</sup>, OMAP<sup>TM</sup>, NovaThor<sup>TM</sup>, ARMADA<sup>TM</sup>, Krait<sup>TM</sup>, and more.

- Hard Disk Drives, LPDDR3, LPDDR4, LPDDR5

- Tablets, Netbooks, Ultra-Mobile PCs

- Smart Phones

- Gaming Devices

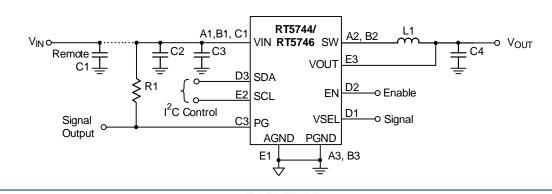

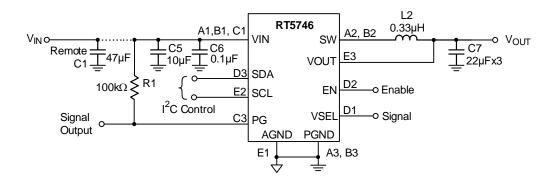

### **4** Simplified Application Circuit

### **5** Ordering Information

| Part No.   | Defaults Output<br>Voltage |       | EN Delay Slave |         | Package Type <sup>(1)</sup>    |  |

|------------|----------------------------|-------|----------------|---------|--------------------------------|--|

|            | VSEL0                      | VSEL1 | Time           | Address |                                |  |

| RT5744AP-A | 0.8V                       | 0.9V  | 0ms            | 0x52    |                                |  |

| RT5744BP-A | 0.8V                       | 0.9V  | 0ms            | 0x51    |                                |  |

| RT5744CP-A | 0.5V                       | 0.6V  | 0ms            | 0x51    | P: WL-CSP-14B 1.31x 2.02 (BSC) |  |

| RT5744DP-A | 0.75V                      | 0.55V | 0ms            | 0x53    |                                |  |

| RT5746AP-A | 1.05V                      | 0.9V  | 0ms            | 0x52    |                                |  |

#### Note 1.

Richtek products are Richtek Green Policy compliant and marked with (1) indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

### 6 Marking Information

RT5744AP-A

**CD: Product Code** YMDAN: Date Code

CG: Product Code YMDAN: Date Code

#### RT5744BP-A

CF: Product Code YMDAN: Date Code

#### RT5744CP-A

EM: Product Code YMDAN: Date Code

RT5744DP-A

**EN: Product Code** YMDAN: Date Code

### **Table of Contents**

| 1  |          | al Description 1                                                           |

|----|----------|----------------------------------------------------------------------------|

| 2  |          | es 1                                                                       |

| 3  |          | ations 1                                                                   |

| 4  |          | fied Application Circuit1                                                  |

| 5  |          | ng Information 2                                                           |

| 6  | Markin   | g Information 2                                                            |

| 7  |          | nfiguration 4                                                              |

| 8  | Function | onal Pin Description4                                                      |

| 9  |          | onal Block Diagram5                                                        |

| 10 | Absolu   | Ite Maximum Ratings 6                                                      |

| 11 |          | atings 6                                                                   |

| 12 |          | mended Operating Conditions6                                               |

| 13 |          | al Information6                                                            |

| 14 | Electri  | cal Characteristics7                                                       |

| 15 | Туріса   | Application Circuit11                                                      |

| 16 | Туріса   | I Operating Characteristics13                                              |

| 17 | Operat   | ion17                                                                      |

|    | 17.1     | PWM Frequency and Adaptive                                                 |

|    |          | On-Time Control17                                                          |

|    | 17.2     | Undervoltage Protection (UVLO)17                                           |

|    | 17.3     | Enable and Soft-Start17                                                    |

|    | 17.4     | Power-Good Indicator18                                                     |

|    | 17.5     | Output Undervoltage Protection (UVP)<br>and Overcurrent Protection (OCP)18 |

|    | 17.6     | Over-Temperature Protection19                                              |

| 18 | Applic | ation Information                       |    |

|----|--------|-----------------------------------------|----|

|    | 18.1   | Inductor Selection                      | 20 |

|    | 18.2   | Input and Output Capacitor Selection    | 20 |

|    | 18.3   | Dynamic Voltage Scaling (DVS) Control - | 21 |

|    | 18.4   | Enable and Shutdown Control             | 21 |

|    | 18.5   | Operation Mode Selection                | 21 |

|    | 18.6   | Low Power Mode Operation                |    |

|    | 18.7   | I2C Time Out Function                   |    |

|    | 18.8   | I2C Interface                           |    |

|    | 18.9   | Thermal Considerations                  | 24 |

|    | 18.10  | Layout Considerations                   |    |

|    | 18.11  | Layout Constraints for Remote Sense     | -  |

|    |        | Applications                            | 27 |

| 19 | Functi | onal Register Description               |    |

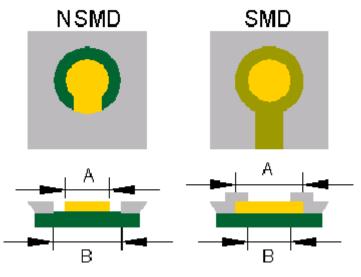

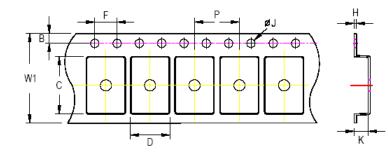

| 20 |        | e Dimension                             |    |

| 21 | Footp  | rint Information                        | 35 |

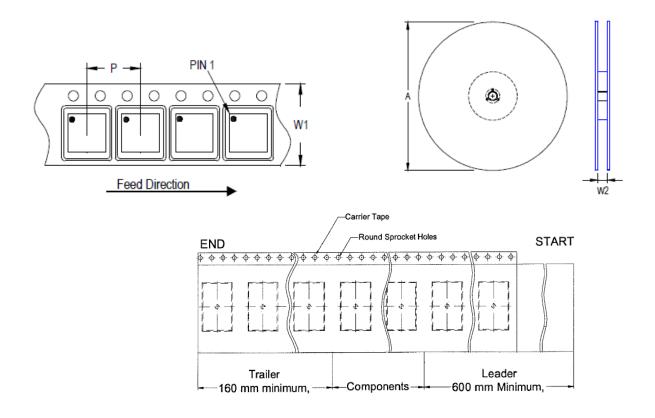

| 22 | Packir | ng Information                          | 36 |

|    | 22.1   | Tape and Reel Data                      |    |

|    | 22.2   | Tape and Reel Packing                   |    |

|    | 22.3   | Packing Material Anti-ESD Property      |    |

| 23 | Datas  | heet Revision History                   |    |

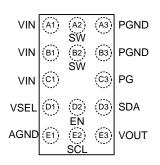

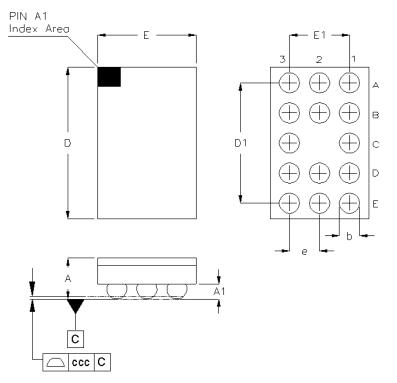

### 7 Pin Configuration

#### (TOP VIEW)

WL-CSP-14B 1.31x 2.02 (BSC)

### 8 Functional Pin Description

| Pin No.    | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1, C1 | VIN      | Power input voltage. Connect to the input power source. Connect to CIN with a minimal path.                                                                                                                                                                                                                                                                                                                                                                     |

| A2, B2     | SW       | Switching node. Connect to the inductor.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A3, B3     | PGND     | Power ground. The low-side MOSFET is referenced to this pin. The CIN and COUT should be returned with a minimal path to these pins.                                                                                                                                                                                                                                                                                                                             |

| C3         | PG       | Power-good indicator. The output of this pin is an open-drain with an external pull-up resistor. After soft startup, PG is pulled up when the FB voltage is within 90% of the reference voltage (typical). The PG status is low while EN is disabled. Note that when VIN is lower than 2.32V (typical), the PG pin will remain low to indicate that the power is not ready.                                                                                     |

| D1         | VSEL     | Output voltage and operation mode selection pin. When this pin is low, VOUT is set by the VSEL0 register. When this pin is high, VOUT is set by the VSEL1 register. Except the output voltage setting, the operation mode can also be configured and selected by the VSEL pin; for example, when 0x02 Bit 1 and Bit 0 are equal to 0, then VSEL0 = Auto PFM/PWM mode, and VSEL1 = Auto PFM/PWM mode. Refer to Functional Register Description for more details. |

| D2         | EN       | Enable control input. A logic-high enables the converter. A logic-low forces the device into shutdown mode, and all registers will reset to default values.                                                                                                                                                                                                                                                                                                     |

| D3         | SDA      | I <sup>2</sup> C serial data.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| E1         | AGND     | Analog ground. All signals are referenced to this pin. Avoid routing high dV/dt AC currents through this pin.                                                                                                                                                                                                                                                                                                                                                   |

| E2         | SCL      | l <sup>2</sup> C serial clock.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E3         | VOUT     | Output feedback sense pin. Output voltage is sensed through this pin.<br>Connect to the output capacitor.                                                                                                                                                                                                                                                                                                                                                       |

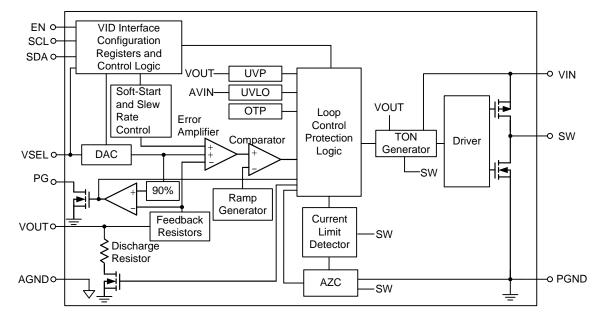

### 9 Functional Block Diagram

### **10 Absolute Maximum Ratings**

#### (<u>Note 2</u>)

| Supply Input Voltage, VIN             | 0.3V to 7V     |

|---------------------------------------|----------------|

| SW Pin Switch Voltage, SW             | -1V to 7.3V    |

| < 10ns                                | -4V to 8.5V    |

| VIN Pin to SW PIN                     | 0.3V to 7V     |

| < 10ns                                | -4V to 8.5V    |

| Other I/O Pin Voltages                | -0.3V to 7V    |

| Lead Temperature (Soldering, 10 sec.) | 260°C          |

| Junction Temperature                  | 150°C          |

| Storage Temperature Range             | –65°C to 150°C |

**Note 2**. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### 11 ESD Ratings

#### (<u>Note 3</u>)

ESD Susceptibility

| HBM (Human Body Model) 2K | Κv |

|---------------------------|----|

|---------------------------|----|

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

### **12 Recommended Operating Conditions**

#### (<u>Note 4</u>)

| ٠ | Supply Input Voltage, VIN  | 2.5V to 5.5V   |

|---|----------------------------|----------------|

| • | Junction Temperature Range | –40°C to 125°C |

Note 4. The device is not guaranteed to function outside its operating conditions.

### **13 Thermal Information**

#### (<u>Note 5</u> and <u>Note 6</u>)

|                                                     | Thermal Parameter                                       | WL-CSP-14B 1.31x2.02 | Unit |

|-----------------------------------------------------|---------------------------------------------------------|----------------------|------|

| θJA                                                 | Junction-to-ambient thermal resistance (JEDEC standard) | 42                   | °C/W |

| θJC(Top)                                            | Junction-to-case (top) thermal resistance               | 0.2                  | °C/W |

| $\theta$ JC(Bottom)                                 | Junction-to-case (bottom) thermal resistance            | 9.5                  | °C/W |

| θJA(EVB)                                            | Junction-to-ambient thermal resistance (specific EVB)   | 49.9                 | °C/W |

| ΨJC(Top) Junction-to-top characterization parameter |                                                         | 1.1                  | °C/W |

| ΨJB                                                 | Junction-to-board characterization parameter            | 27.7                 | °C/W |

- **Note 5.** For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, <u>AN061</u>.

- Note 6. θ<sub>JA(EVB)</sub>, Ψ<sub>JC(TOP)</sub>, and Ψ<sub>JB</sub> are simulated on a high effective-thermal-conductivity four-layer test board which is in size of 70mm x 50mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

### **14 Electrical Characteristics**

| $(V_{IN} = 3.6V, T_A = 25^{\circ}C, unles)$ | s otherwise specified.) |

|---------------------------------------------|-------------------------|

|---------------------------------------------|-------------------------|

| Parameter                                         | Symbol     | Test Conditions                                                                                                                                                | Min | Тур  | Max  | Unit  |

|---------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Operating Quiescent<br>Current PWM                | IQ_PWM     | $I_{LOAD} = 0$ , mode Bit = 1 (Forced PWM) ( <u>Note 7</u> )                                                                                                   |     | 15   |      | mA    |

| Operating Quiescent<br>Current PFM                | IQ_PFM     | Iload = 0A                                                                                                                                                     |     | 45   |      | μA    |

| Operating Low Power Mode<br>Quiescent Current PFM | IQ_PFM_LPM | ILOAD = 0A and Enable LPM<br>( <u>Note 7</u> )                                                                                                                 |     | 36   |      | μA    |

| H/W Shutdown Supply<br>Current                    | ISHDN_H/W  | EN = GND                                                                                                                                                       |     | 0.1  | 3    | μA    |

| S/W Shutdown Supply<br>Current                    | ISHDN_S/W  | $ \begin{array}{l} EN = V_{IN}, \ BUCK\_ENx = 0, \\ 2.5V \leq V_{IN} \leq 5.5V \end{array} $                                                                   |     | 2    | 12   | μA    |

| Undervoltage-Lockout<br>Threshold                 | Vuvlo      | VIN rising                                                                                                                                                     |     | 2.32 | 2.45 | V     |

| Undervoltage-Lockout<br>Hysteresis                | VUVLO_HYS  |                                                                                                                                                                |     | 350  |      | mV    |

| On-Resistance of High-Side MOSFET                 | RDSON_H    | VIN = 5V                                                                                                                                                       |     | 30   |      | mΩ    |

| On-Resistance of Low-Side<br>MOSFET               | RDSON_L    | V <sub>IN</sub> = 5V                                                                                                                                           |     | 17   |      | mΩ    |

| Input Voltage Logic-High                          | Vih        | $2.5V \leq V_{IN} \leq 5.5V$                                                                                                                                   | 1.1 |      |      | v     |

| Input Voltage Logic-Low                           | VIL        | $2.5V \leq V \text{IN} \leq 5.5V$                                                                                                                              |     |      | 0.4  | v     |

| EN Input Bias Current                             | IEN        | EN input tied to GND or VIN                                                                                                                                    |     | 0.01 | 1    | μA    |

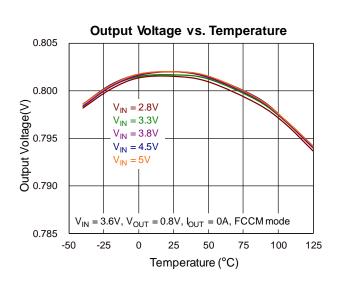

|                                                   | Vout_acc   | $\begin{array}{ll} 2.8V \leq V_{IN} \leq 4.8V, \\ I_{OUT(DC)} = 0 \text{ to } 4A, \ V_{OUT} > 0.6V, \\ Auto \ PFM/PWM & (\underline{Note \ 7}) \end{array}$    | -2  |      | 3    | %     |

| Output Voltage Assuracy                           |            | $\begin{array}{l} 2.8V \leq V_{IN} \leq 4.8V, \\ I_{OUT(DC)} = 0 \text{ to } 4A, \ V_{OUT} \leq 0.6V, \\ Auto \ PFM/PWM  (\underline{Note \ 7}) \end{array}$   | -12 |      | 18   | mV    |

| Output Voltage Accuracy                           |            | $\begin{array}{l} 2.8V \leq V_{IN} \leq 4.8V, \\ I_{OUT(DC)} = 0 \text{ to } 4A, \ V_{OUT} > 0.6V, \\ Forced PWM \qquad (\underline{Note \ 7}) \end{array}$    | -2  |      | 2    | %     |

|                                                   |            | $\begin{array}{l} 2.8V \leq V_{IN} \leq 4.8V, \\ I_{OUT(DC)} = 0 \text{ to } 4A, \ V_{OUT} \leq 0.6V, \\ Forced PWM \qquad (\underline{Note \ 7}) \end{array}$ | -12 |      | 12   | mV    |

|                                                   |            | $\begin{array}{l} \text{IOUT(DC)} = 1 \text{ to } 4\text{A}, \text{ VOUT} > 0.6\text{V}, \\ (\underline{\text{Note 7}}) \end{array}$                           |     | 0.1  |      | - %/A |

| Load Regulation                                   | VLOAD_REG  | $\label{eq:out_def} \begin{array}{l} \text{IOUT(DC)} = 1 \text{ to } 4\text{A}, \ \text{VOUT} \leq 0.6\text{V}, \\ (\underline{\text{Note 7}}) \end{array}$    |     | 0.2  |      |       |

| Parameter                                              | Symbol     | Test Conditions                                                                                                                                                                                               | Min  | Тур      | Max  | Unit    |

|--------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|---------|

| Line Regulation                                        |            | $\begin{array}{l} 2.5V \leq V_{IN} \leq 5.5V, \ V_{OUT} > 0.4V, \\ I_{OUT(DC)} = 2A \qquad (\underline{Note\ 7}) \end{array}$                                                                                 |      | 0.2      |      | 0/ /\ / |

| Line Regulation                                        | VLOAD_REG  | $\begin{array}{l} 2.5V \leq V_{IN} \leq 5.5V, \ V_{OUT} \leq 0.4V, \\ I_{OUT}(DC) = 2A \qquad (\underline{Note \ 7}) \end{array}$                                                                             |      | 0.3      |      | %/V     |

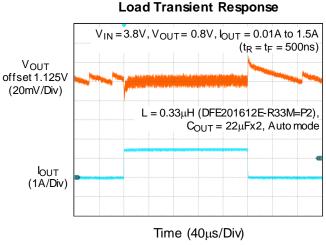

|                                                        |            | ILOAD step 0.01A to 1.5A,<br>tR = tF = 500ns, Vout = 1.125V<br>( <u>Note 7</u> )                                                                                                                              |      | ±45      |      |         |

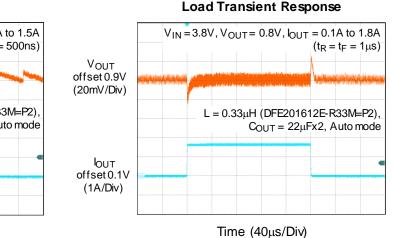

| Load Transient Response                                | VLOAD_TRAN | $  I_{LOAD} \text{ step } 0.1 \text{A to } 1.8 \text{A}, \\ t_{R} = t_{F} = 1 \mu_{S}, \text{ VIN} = 3.8 \text{V}, \\ \text{VOUT} = 0.9 \text{V}  (\underline{\text{Note } 7}) $                              |      | ±56      |      | mV      |

|                                                        |            | $    I_{LOAD} \text{ step } 0.01 \text{A to } 0.8 \text{A}, \\ t_{\text{R}} = t_{\text{F}} = 1 \mu_{\text{S}}, \ L = 0.33 \mu\text{H}, \\ C_{\text{OUT}} = 22 \mu\text{F x } 2  (\underline{\text{Note 7}}) $ |      | 45       |      |         |

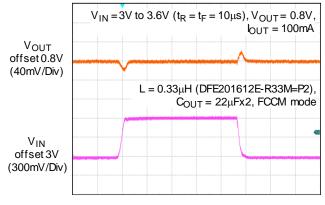

| Line Transient Response                                | VLINE_TRAN |                                                                                                                                                                                                               |      | ±40      |      | mV      |

| High-Side Switch Current                               | Ішм_н      | RT5744                                                                                                                                                                                                        | 5.5  | 6        | 6.5  | А       |

| Limit                                                  |            | RT5746                                                                                                                                                                                                        | 7    | 7.7      | 8.5  | А       |

| Low-Side Switch Current                                |            | RT5744                                                                                                                                                                                                        | 4    | 4.5      | 5    | А       |

| Limit                                                  | ILIM_L     | RT5746                                                                                                                                                                                                        | 6    | 6.5      | 7    | А       |

| Over-Temperature<br>Protection Threshold               | Тотр       |                                                                                                                                                                                                               |      | 150      |      | °C      |

| Over-Temperature<br>Protection Threshold<br>Hysteresis | Totp_hys   |                                                                                                                                                                                                               |      | 15       |      | °C      |

| Input Overvoltage Rising<br>Threshold                  | VIN_OVP_R  | Rising threshold                                                                                                                                                                                              |      | 6.15     |      | V       |

| Input Overvoltage Falling<br>Threshold                 | VIN_OVP_F  | Falling threshold                                                                                                                                                                                             | 5.5  | 5.73     |      | V       |

| Power-Good Voltage<br>Threshold                        | Vpg        |                                                                                                                                                                                                               |      | 90       |      | %       |

| Power-Good Voltage<br>Hysteresis                       | Vpg_hys    |                                                                                                                                                                                                               |      | 10       |      | %       |

| Switching Frequency                                    | fsw        | Vout = Default<br>RT5744A: 0.8V<br>RT5744B: 0.8V<br>RT5744C: 0.5V<br>RT5744D: 0.75V<br>RT5746A: 1.05V<br>(Note 8)                                                                                             | 2100 | 240<br>0 | 2700 | kHz     |

| Minimum Off-Time                                       | toff_min   |                                                                                                                                                                                                               |      | 170      |      | ns      |

| DAC Resolution                                         |            | ( <u>Note 7</u> )                                                                                                                                                                                             |      | 8        |      | bits    |

| DAC Differential<br>Nonlinearity                       |            | ( <u>Note 7</u> )                                                                                                                                                                                             |      |          | 0.5  | LSB     |

| Parameter                                    | Symbol  | Test Conditions                    | Min  | Тур | Мах | Unit |

|----------------------------------------------|---------|------------------------------------|------|-----|-----|------|

| I <sup>2</sup> C Interface ( <u>Note 7</u> ) |         |                                    |      | •   | •   | •    |

|                                              |         | Standard mode                      |      |     | 100 | kHz  |

|                                              |         | Fast mode                          |      |     | 400 | kHz  |

| SCL Clock Rate                               | fscl    | Fast mode Plus                     |      |     | 1   | MHz  |

|                                              |         | High speed mode, load 100pF<br>max |      |     | 3.4 | MHz  |

|                                              |         | Standard mode                      | 4    |     |     |      |

| (Denested) Start Hold Time                   |         | Fast mode                          | 0.6  |     |     |      |

| (Repeated) Start Hold Time                   | thd;sta | Fast mode Plus                     | 0.26 |     |     | μs   |

|                                              |         | High speed mode                    | 0.16 |     |     |      |

|                                              |         | Standard mode                      | 4.7  |     |     |      |

| SCL Clock Low Period                         | ti our  | Fast mode                          | 1.3  |     |     | μs   |

| SUL CIOCK LOW PERIOD                         | tLOW    | Fast mode Plus                     | 0.5  |     |     |      |

|                                              |         | High speed mode                    | 0.16 |     |     |      |

|                                              | tніgн   | Standard mode                      | 4    |     |     | μs   |

| SCL Clock High Period                        |         | Fast mode                          | 0.6  |     |     |      |

| COL Clock right chou                         |         | Fast mode Plus                     | 0.26 |     |     |      |

|                                              |         | High speed mode                    | 0.06 |     |     |      |

|                                              |         | Standard mode                      | 4.7  |     |     | μs   |

| (Repeated) Start Setup                       | tsu;sta | Fast mode                          | 0.6  |     |     |      |

| Time                                         | 130,314 | Fast mode Plus                     | 0.26 |     |     |      |

|                                              |         | High speed mode                    | 0.16 |     |     |      |

|                                              |         | Standard mode                      | 5    |     |     |      |

| CDA Data Liald Time                          |         | Fast mode                          | 0    |     |     |      |

| SDA Data Hold Time                           | thd;dat | Fast mode Plus                     | 0    |     |     | μs   |

|                                              |         | High speed mode                    | 0.01 |     |     |      |

|                                              |         | Standard mode                      | 250  |     |     |      |

|                                              |         | Fast mode                          | 100  |     |     |      |

| SDA Setup Time                               | tsu;dat | Fast mode Plus                     | 50   |     |     | ns   |

|                                              |         | High speed mode                    | 30   |     |     |      |

|                                              |         | Standard mode                      | 4    |     |     |      |

| STOP Condition Setup                         |         | Fast mode                          | 0.6  |     |     |      |

| Time                                         | tsu;sto | Fast mode Plus                     | 0.26 |     |     | μs   |

|                                              |         | High speed mode                    | 0.16 |     |     |      |

|                                              |         | Standard mode                      | 4.7  |     |     |      |

| Bus Free Time between                        | tBUF    | Fast mode                          | 1.3  |     |     | μs   |

| Stop and Start                               |         | Fast mode Plus                     | 0.5  |     |     |      |

|                                              |         |                                    | 0.0  |     |     |      |

9

www.richtek.com

| Parameter                           | Symbol  | Test Conditions                         | Min                | Тур | Мах  | Unit |

|-------------------------------------|---------|-----------------------------------------|--------------------|-----|------|------|

|                                     |         | Standard mode                           |                    |     | 1000 |      |

|                                     |         | Fast mode                               | 20                 |     | 300  |      |

| Rise Time of SDA and SCL            |         | Fast mode Plus                          |                    |     | 120  |      |

| Signals                             | tR      | High speed mode (SDA)<br>load 100pF max | 10                 |     | 80   | ns   |

|                                     |         | High speed mode (SCL)<br>load 100pF max | 10                 |     | 40   |      |

|                                     | tF      | Standard mode                           |                    |     | 300  |      |

|                                     |         | Fast mode                               | 20 x<br>(VDD/5.5V) |     | 300  |      |

| Fall Time of SDA and SCL<br>Signals |         | Fast mode Plus                          | 20 x<br>(VDD/5.5V) |     | 120  | ns   |

| Ŭ                                   |         | High speed mode (SDA)<br>load 100pF max | 10                 |     | 80   |      |

|                                     |         | High speed mode (SCL)<br>load 100pF max | 10                 |     | 40   |      |

| SDA Output Low Sink<br>Current      | IOL_I2C | SDA voltage = 0.4V                      | 2                  |     |      | mA   |

Note 7. Guaranteed by design.

Note 8. Measured switching frequency may not meet the declared range due to different operation modes and output voltages. For operating in PSM, the f<sub>SW</sub> varies according to the operating condition. For V<sub>OUT</sub> < 0.5V, the f<sub>SW</sub> may be reduced if the duty cycle is too small.

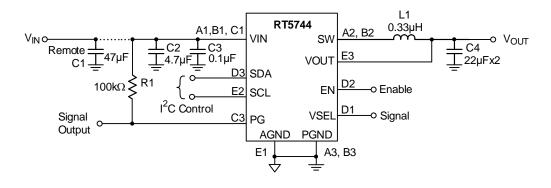

### **15 Typical Application Circuit**

Figure 1. Typical Application Circuit for the RT5744

Figure 2. Typical Application Circuit for the RT5746

| Table 1. Reco | mmended External Com | nponents for 4A/6A M | laximum Load Current |

|---------------|----------------------|----------------------|----------------------|

|               |                      |                      |                      |

| Component            | Description                                                            | Vendor P/N                  |  |  |

|----------------------|------------------------------------------------------------------------|-----------------------------|--|--|

| L1                   | 330nH (I <sub>DC</sub> = 4.8A, I <sub>SAT</sub> = 6.3A, 15m $\Omega$ ) | DFE201612E-R33M=P2 (Murata) |  |  |

|                      | 470nH ( $I_{DC}$ = 4.9A, $I_{SAT}$ = 6.7A, 17mΩ)                       | DFE252012F-R47M=P2 (Murata) |  |  |

| C2                   | 4.7μF, 10V, X5R, 0402                                                  | GRM155R61A475MEAA (Murata)  |  |  |

| C3 ( <u>Note 9</u> ) | 100nF, 6.3V, X5R, 0201                                                 | GRM033R60J104KE19D (Murata) |  |  |

| 64                   |                                                                        | GRM188R60J226MEA0D (Murata) |  |  |

| C4                   | 22μF x 2, 6.3V, X5R, 0603                                              | C1608X5R0J226M080AC (TDK)   |  |  |

|                      | 330nH (I <sub>DC</sub> =12A, I <sub>SAT</sub> =13.5A, 10.8mΩ)          | CMME041B-R33MS (Cyntec)     |  |  |

| L2 ( <u>Note 11</u>  | 220nH (I <sub>DC</sub> =13A, I <sub>SAT</sub> =15.5A, 7.2mΩ)           | CMME041B-R22MS (Cyntec)     |  |  |

| C5                   | 22μF, 6.3V, X5R, 0603                                                  | GRM188R60J226MEA0D (Murata) |  |  |

| C6 ( <u>Note 9</u> ) | 100nF, 6.3V, X5R, 0201                                                 | GRM033R60J104KE19D (Murata) |  |  |

|                      |                                                                        | GRM188R60J226MEA0D (Murata) |  |  |

| C7 ( <u>Note 11</u>  | 22µF x 3, 6.3V, X5R, 0603                                              | C1608X5R0J226M080AC (TDK)   |  |  |

|                      | 47μF x 3, 6.3V, X5R, 0603                                              | GRM188R60J476ME01 (Murata)  |  |  |

**Note 9**. The decouple capacitors C3 and C6 are recommended to reduce any high-frequency component on VIN bus. C3 and C6 are optional and used to filter any high frequency components on the VIN bus.

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

- Note 10. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any de-rating effects, like a DC bias.

- **Note 11**. For general purpose applications, L2 = 330nH and C7 =  $22\mu$ F x 3pcs are recommended. For fast load transient requirements, it is recommended to use L2 = 220nH and C7 =  $47\mu$ F x 3pcs.

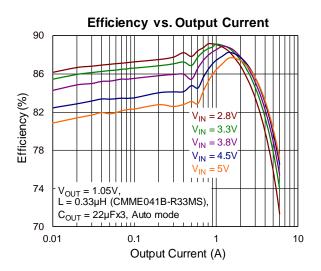

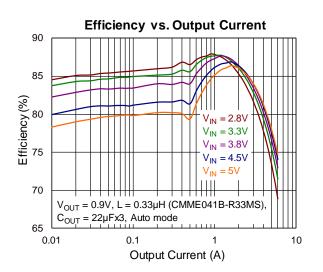

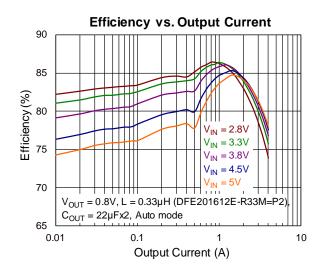

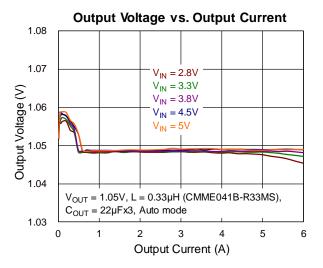

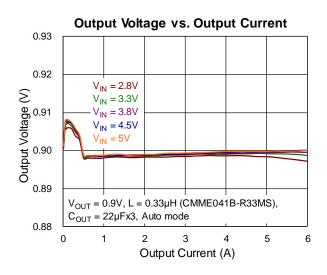

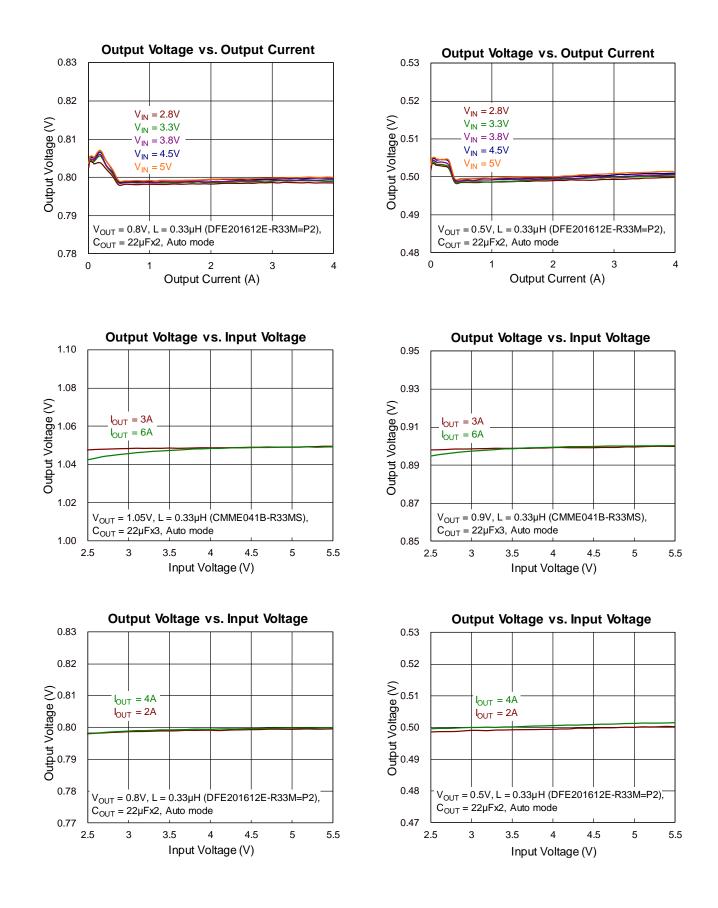

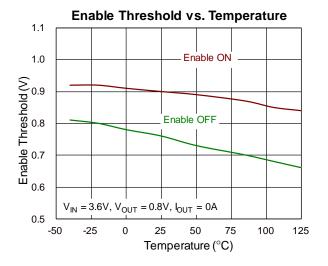

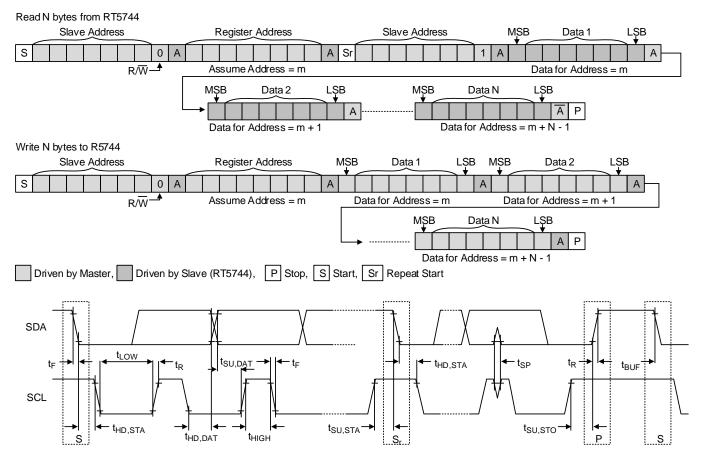

### **16 Typical Operating Characteristics**

Efficiency vs. Output Current 85 80 75 Efficiency (%) V<sub>IN</sub> = 2.8V 70 V<sub>IN</sub> = 3.3V V<sub>IN</sub> = 3.8V 65 V<sub>IN</sub> = 4.5V = 5V Vini 60 55 V<sub>OUT</sub> = 0.5V, L = 0.33µH (DFE201612E-R33M  $C_{OUT} = 22\mu Fx2$ , Auto mode 50 0.01 0.1 1 10 Output Current (A)

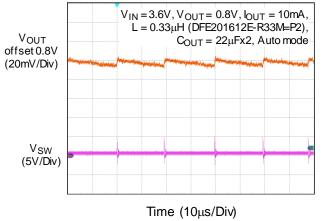

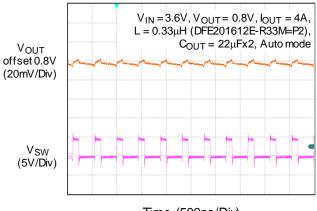

**Output Ripple Voltage**

**Output Ripple Voltage**

Time (500ns/Div)

Load Transient Response

$I_{OUT} = 0.01A$  to 0.8A ( $t_R = t_F = 1\mu s$ ), L = 0.33 $\mu H$

$C_{OUT} = 22\mu Fx2,$

Auto mode

Time (40µs/Div)

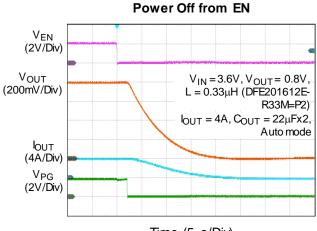

Power On from EN

V<sub>IN</sub> = 3.8V, V<sub>OUT</sub> = 0.8V

(DFE201612E-R33M=P2

Line Transient Response

Time (50µs/Div)

Time (5µs/Div)

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

VOUT

offset 0.8V

(10mV/Div)

ωυт

(400mA/Div)

### 17 Operation

The RT5744 and RT5746 are low-voltage synchronous step-down converters that can support input voltage ranging from 2.5V to 5.5V, and the output current can be up to 4A and 6A, respectively. The RT5744 and RT5746 use ACOT<sup>®</sup> mode control. To achieve good stability with low-ESR ceramic capacitors, the ACOT<sup>®</sup> uses a virtual inductor current ramp generated inside the IC. This internal ramp signal replaces the ESR ramp normally provided by the output capacitor's ESR. The ramp signal and other internal compensations are optimized for low-ESR ceramic output capacitors.

#### 17.1 PWM Frequency and Adaptive On-Time Control

In steady-state operation, the feedback voltage (sensed from VOUT), with the virtual inductor current ramp added, is compared to the reference voltage (set by VSEL). When the combined signal is less than the reference voltage, the on-time one-shot is triggered, provided that the minimum off-time one-shot is cleared and the measured inductor current (through the synchronous rectifier) is below the current limit. The on-time one-shot turns on the high-side switch and the inductor current ramps up linearly. After the on-time period, the high-side switch is turned off, the synchronous rectifier is turned on, and the inductor current ramps down linearly. At the same time, the minimum off-time one-shot is triggered to prevent another immediate on-time during the noisy switching times and to allow the feedback voltage and current sense signals to settle. The minimum off-time is kept short so that rapidly-repeated on-times can raise the inductor current quickly when needed.

The on-time can be roughly estimated using the equation:

$$t_{ON} = \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}}$$

where fsw is nominal 2.4MHz.

#### 17.2 Undervoltage Lockout (UVLO)

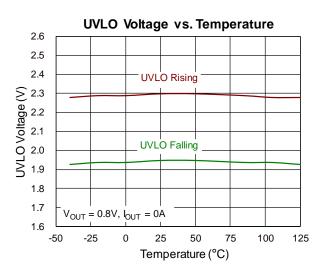

The UVLO continuously monitors the voltage of VIN to make sure the device works properly. When the VIN is high enough to reach the high threshold voltage  $V_{UVLO}$  (typically 2.32V), the step-down converter softly starts or prebiases to its regulated output voltage. When the VIN decreases to its low threshold  $V_{UVLO} - V_{UVLO}$  (350mV hysteresis), the device will shut down.

#### 17.3 Enable and Soft-Start

When the EN pin is Low, the IC is shut down, all internal circuits are off, and the part draws very little current. In this state,  $I^2C$  cannot be written or read until the VIN is above the VUVLO and the VEN is above the VIH (1.1V). The registers will reset when the EN pin is Low or during a Power-On Reset (POR).

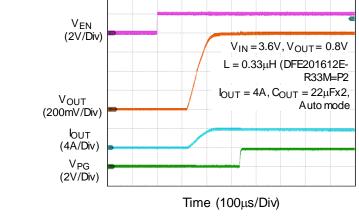

An internal current source charges an internal capacitor to build the soft-start ramp voltage. The typical soft-start time can be programmed by  $I^2C$ . When VIN is above VUVLO and the device is powered on through the EN pin (the EN delay time setting is 0ms), the output voltage will start to rise within 150µs (typical) as soon as the VEN is above the VIH. See Enable and Shutdown Control for more details.

Figure 3. Start-Up Sequence without EN Delay

#### 17.4 Power-Good Indicator

The RT5744 and RT5746 feature an open-drain power-good output (PG) to monitor the output voltage status. The output delay of comparator prevents false flag operation for short excursions in the output voltage, such as during line and load transients. Pull up PG with a resistor to Vout or an external voltage below 5.5V. When VIN voltage rises above VuvLo, the power-good function is activated. After soft-start is finished, the PG pin is controlled by a comparator connected to the feedback signal Vout. If Vout rises above a power-good high threshold (VPG) (typically 90% of the reference voltage), the PG pin will be in high impedance and VPG will be held high. Moreover, when VIN is above UVLO and the device is powered on through the EN pin (EN delay time setting is 0ms), the PG pin will assert high within 500 $\mu$ s (typical) as soon as the VEN is above logic-high threshold.

When Vout falls below the power-good low threshold (VPG – VPG\_HYS) (typically 80% of the reference voltage), the PG pin will be pulled low after a certain delay ( $3\mu$ s, typically). Once being started-up, if any internal protection is triggered, PG will be pulled low to GND. The internal open-drain pull-down device ( $10\Omega$ , typically) will pull the PG pin low. Note that when Vin is lower than 2.32V (VUVLO), the PG pin will keep low to indicate the power is not ready.

#### 17.5 Output Undervoltage Protection (UVP) and Overcurrent Protection (OCP)

When the output voltage of the RT5744 and RT5746 are lower than 59% of the reference voltage after soft-start, the UVP is triggered.

The RT5744 and RT5746 sense the current signal when high-side and low-side MOSFETs turn on. As a result, the OCP is cycle-by-cycle limit. If the OCP occurs, the converter holds off the next pulse and turns on low-side switch until the inductor drops below the valley current limit, and then turns on high-side again to maintain the output voltage and supports the loading current to the output before triggering UVP.

If the OCP condition keeps and the load current is larger than the current that the converter can provide, the output voltage will decrease and drop below the UVP threshold, and the converter will keep switching for 16 consecutive cycles before it enters hiccup operation. The converter latches off 1.7ms when the output voltage is still lower than the UVP threshold, and the soft-start sequence begins again after the latching off time.

Note that, there is sensing propagation delay time before triggering OCP; hence, the OCP may take a few cycles to occur when the inductor current is near the OCP threshold. If the output voltage drops slowly before entering hiccup operation, the converter will extend the high-side switch on-time and turns on the low-side switch for only minimum off-time to provide large load current and catch up with the output voltage before detecting peak current limit OCP.

#### 17.6 Over-Temperature Protection

The RT5744 and RT5746 have over-temperature protection (OTP) mechanism to prevent overheating due to excessive power dissipation. When the junction temperature exceeds the thermal shutdown threshold ToTP (typically 150°C), the device will be shut down immediately. Once its junction temperature is below the recovery threshold ToTP – ToTP\_HYS (15°C hysteresis), the device will resume normal operation with a complete soft-start.

### **18 Application Information**

#### (<u>Note 12</u>)

The basic RT5744 and RT5746 application circuit are shown in <u>Typical Application Circuit</u>. The selection of external components is determined by the maximum load current and begins with the selection of the inductor value, operating frequency, and followed by CIN and COUT.

#### 18.1 Inductor Selection

The inductor value and operating frequency determine the ripple current according to a specific input and output voltage. The ripple current,  $\Delta I_L$ , increases with a higher VIN and decreases with a higher inductance, as shown in the following equation:

$$\Delta I_{L} = \left[ \frac{V_{OUT}}{f \times L} \right] \times \left[ 1 - \frac{V_{OUT}}{V_{IN}} \right]$$

where f is the operating frequency and L is the inductance. A lower ripple current reduces not only ESR losses in the output capacitors, but also the output voltage ripple. A higher operating frequency combined with smaller ripple current is necessary to achieve high efficiency. Thus, a large inductor is required to attain this goal.

The largest ripple current occurs at the highest V<sub>IN</sub>. A reasonable starting point for selecting the ripple current is  $\Delta I_L = 0.3 \text{ x } I_{MAX}$  to 0.4 x I<sub>MAX</sub>. To guarantee that the ripple current stays below a specified maximum, the inductor value should be chosen according to the following equation:

$L = \left[\frac{V_{OUT}}{f \times \Delta I_{L}(MAX)}\right] \times \left[1 - \frac{V_{OUT}}{V_{IN}(MAX)}\right]$

#### 18.2 Input and Output Capacitor Selection

An input capacitor, CIN, is needed to filter out the trapezoidal current at the source of the high-side MOSFET.

To prevent large ripple current, a low ESR input capacitor sized for the maximum RMS current should be used. The RMS current is given by:

$$I_{RMS} = I_{OUT}(MAX) \times \frac{V_{OUT}}{V_{IN}} \times \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}(MAX)/2$ .

This simple worst-case condition is commonly used for design. Choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet the size or height requirements of the design. Ceramic capacitors have high ripple current, high voltage rating and low ESR, which makes them ideal for switching regulator applications.

However, they can also have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can lead to significant ringing. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input, VIN. At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at VIN large enough to damage the part. Thus, care must be taken to select a suitable input capacitor.

The selection of  $C_{OUT}$  is determined by the required ESR to minimize output voltage ripple. Moreover, the amount of bulk capacitance is also a key for  $C_{OUT}$  selection to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response.

The output voltage ripple,  $\Delta VOUT$ , is determined by:

$\Delta V_{OUT} \leq \Delta I_L \left[ \text{ESR} + \frac{1}{8 \times f_{SW} \times C_{OUT}} \right]$

#### 18.3 Dynamic Voltage Scaling (DVS) Control

The RT5744 and RT5746 all series products have programmable output voltage range from 0.27V to 1.4V with 6.25mV/bit resolution. Note that, the output voltage can be set by the NSELx register bit and the output voltages are given by the following equation and example:

VOUT = 0.27V + NSELx x 6.25mVFor example: If NSELx = 0111100 (60 decimal), then VOUT = 0.27 + 60 x 6.25mV

= 0.27 + 0.375 = 0.645V.

The RT5744 and RT5746 also have external VSEL pin to select NSEL1(0x01) or NSEL0(0x00). Pulling VSEL to high is for VSEL1 and pulling VSEL to low is for VSEL0. Upon POR, VSEL0 and VSEL1 are reset to their default voltages.

The RT5744 and RT5746 can also control the DVS speed, regardless of the slew rate of voltage changes within the same NSELx or between VSEL0 and VSEL1. In the CONTROL1 register, the UP\_SR bits control the up-speed. In the CONTROL2 register, DN\_SR can control the down-speed. The default UP\_SR is  $12.5 \text{mV/}\mu\text{s}$  while the default DN\_SR is  $3.125 \text{mV/}\mu\text{s}$ . Refer to the Functional Register Description for more detailed slew rate settings.

#### 18.4 Enable and Shutdown Control

The RT5744 and RT5746 series can power on or off through  $I^2C$  by setting the CONTROL2(0x06) EN\_VSELx bit to High activating the part to begin the soft-start cycle. Moreover, the soft-start slew rate is programmable through the register 0x06[3:2]. The SS\_SR default is 10mV/ $\mu$ s.

The RT5744 and RT5746 series also implements enable control by the external EN pin with enable and shutdown delay times. Note that the enable delay time is the factory setting, and the default value can be read from the CONTROL3 (0x07). As for the shutdown delay time, it can be either factory programmed or set by software, and the default value can be read from the CONTROL4 (0x08).

In the CONTROL1 (0x02) register, set the DISCHG bit to 1 can make VOUT to discharge by an internal resistor when the converter is shut down through  $I^2C$ . If the DISCHG bit is set to 0, VOUT will decrease depending on the load. Note that when the EN pin is set to low, the device will default to turning on the internal 10 $\Omega$  discharge resistor.

#### 18.5 Operation Mode Selection

The default operation mode of the RT5744 and RT5746 series is auto PFM/PWM mode (MODE\_VSEL0 and MODE\_VSEL1). In the CONTROL1 register, MODE\_VSEL0 and MODE\_VSEL1 can decide whether the converter is always at forced PWM mode or enters power saving mode under light load conditions.

In auto PFM/PWM mode, the auto zero current detector circuit senses the SW waveform to adjust the zero current threshold voltage. When the current of low-side MOSFET decreases to the zero current threshold, the low-side MOSFET turns off to prevent negative inductor current. In this way, the zero current threshold can be adjusted for different conditions to get better efficiency.

Note that when output voltage is changing from high to low, the RT5744 and RT5746 will make transition operation to forced PWM mode and the output voltage will decrease quickly.

#### 18.6 Low Power Mode Operation

The RT5744 and RT5746 feature auto PFM/PWM mode to achieve power-saving operation. It generates a single switching pulse to ramp up the inductor current and recharges the output capacitor, followed by a skip pulse or a sleep period to cut down current demand from input source to obtain high efficient under light load conditions. The load current is supported by the output capacitor during this sleep period depending on the load current and the inductor peak current.

To minimize the battery energy consumption, the system requests further quiescent current reduction operation such as shipping mode or suspend operation. The RT5744 and RT5746 feature low power mode (LPM) operation, where several of the internal protection circuits (input OVP, UVP) are shutdown to achieve lowest 36µA operating quiescent current for ultra-light load condition. LPM operation can be enabled by setting LPM control register (0x0A bit 1) to 1 in the CONTROL5 register.

#### I<sup>2</sup>C Time Out Function 18.7

The RT5744 and RT5746 have built-in I<sup>2</sup>C time out function to make the RT5744 and RT5746 resume listening state during communication bus error situations.

When the RT5744 and RT5746 detect whether the SCL pin or SDA pin is pulled down for more than 30ms, the RT5744 and RT5746 will reset its I<sup>2</sup>C interface. The I<sup>2</sup>C time out function can be enabled or disabled by control register (0x0A bit 0). For more detail setting values, please refer to Functional Register Description.

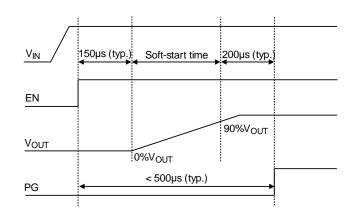

#### 18.8 I<sup>2</sup>C Interface

The entire series of the RT5744 and RT5746 utilizes the I<sup>2</sup>C interface for configuring various settings such as output voltage, Dynamic Voltage Scaling (DVS) slew rate, mode selection, VSEL function setting, and more. The register map provides details on each function's register and how to utilize these functions effectively.

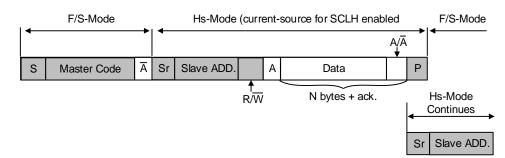

The entire series of the RT5744 and RT5746 supports the fast mode I<sup>2</sup>C interface (bit rate 400kb/s), and each part has its own slave address. The I<sup>2</sup>C slave ID for the entire series of RT5744 and RT5746 is preconfigured by the factory and ranges from 0x50 to 0x57. For example, the default I<sup>2</sup>C slave address of the RT5744A is 7'b1010010. The write or read bit stream (N  $\ge$  1) is shown below:

Figure 4. I<sup>2</sup>C Read and Write Stream and Timing Diagram

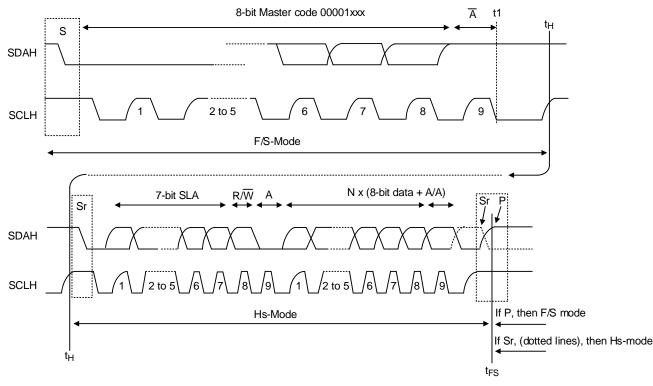

The RT5744 and RT5746 also support high-speed mode (bit rate up to 3.4Mb/s) with access code 08H. <u>Figure 5</u> and <u>Figure 6</u> show detailed transfer format. Hs-mode can only commence after the following conditions (all of which are in F/S-mode):

- START condition (S)

- 8-bit master code (00001xxx)

- Not-acknowledge bit ( A )

Figure 5. Data Transfer Format in HS-Mode

Figure 6. A Complete HS-Mode Transfer

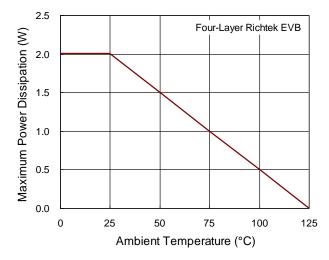

#### 18.9 Thermal Considerations

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

#### $\mathsf{P}\mathsf{D}(\mathsf{M}\mathsf{A}\mathsf{X}) = (\mathsf{T}\mathsf{J}(\mathsf{M}\mathsf{A}\mathsf{X}) - \mathsf{T}\mathsf{A}) \ / \ \theta \mathsf{J}\mathsf{A}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-toambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA(EVB)}$ , is highly package dependent. The thermal resistance,  $\theta_{JA(EVB)}$ , is 49.9°C/W on a high effective-thermal-conductivity four-layer test board. The maximum power dissipation at TA = 25°C can be calculated as follows:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C)/(49.9^{\circ}C/W) = 2W$  for a WL-CSP-14B 1.31x2.02 (BSC) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA(EVB)}$ . The derating curves in Figure 7 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 7. Derating Curve of Maximum Power Dissipation

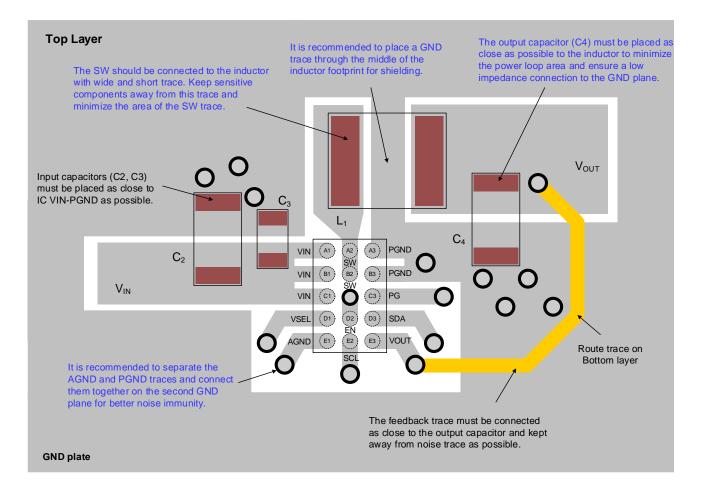

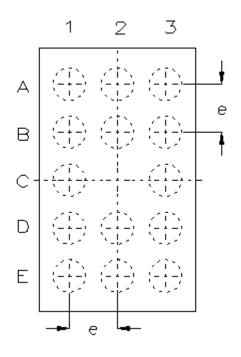

#### 18.10 Layout Considerations

For best performance of the RT5744 and RT5746, the following layout guidelines must be strictly followed.

- Input capacitor must be placed as close as possible to the IC to minimize the power loop area. A typical 0.1µF decouple capacitor is recommended to reduce power loop area and any high-frequency component on VIN.

- The SW node has high-frequency voltage swings and should be kept at a small area. Keep analog components away from the SW node to prevent stray capacitive noise pickup.

- Keep every power trace connected to pin as wide as possible for improving thermal dissipation.

- It is recommended to connect the AGND pin to the 2<sup>nd</sup> ground plane through a via from the top layer to the 2<sup>nd</sup> layer.

- Keep the current protection setting network as close as possible to the IC. The routing of the network should avoid coupling to high-voltage switching node.

- Connections from the drivers to the respective gates of the high-side or the low-side MOSFETs should be as short as possible to reduce stray inductance.

RICHTEK

$Copyright @ 2024 \ Richtek \ Technology \ Corporation. \ All \ rights \ reserved.$

d. RICHTEK

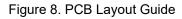

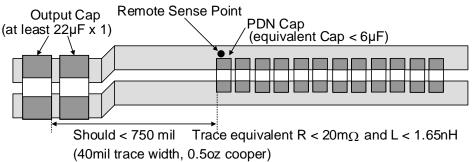

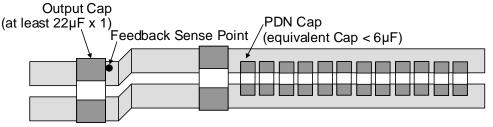

#### 18.11 Layout Constraints for Remote Sense Applications

Case 1:

RICHTEK

- If the remote sense point is located at PDN cap

- , the distance between 1<sup>st</sup> 22µF cap and PDN cap should not exceed 750 mil.

Case 2:

If the remote sense point is located at  $1^{st}\,22\mu F$  cap

, there will be no constraint between  $1^{st}\,22\mu F$  cap and PDN cap yet sacrifice AP transient performance with this configuration.

If the remote sense point is located at PDN cap and there is long trace between  $1^{st} 22\mu F$  cap and inductor, the distance should not exceed 800mil.

Figure 9. Layout Constraints

**Note 12.** The information provided in this section is for reference only. The customer is solely responsible for the designing, validating, and testing your product incorporating Richtek's product and ensure such product meets applicable standards and any safety, security, or other requirements.

### **19 Functional Register Description**

| Table 2. Vour Setting |       |          |       |          |       |          |       |          |       |  |  |

|-----------------------|-------|----------|-------|----------|-------|----------|-------|----------|-------|--|--|

| Vout (V)              | Value | Vout (V) | Value | Vout (V) | Value | Vout (V) | Value | Vout (V) | Value |  |  |

| 0.27                  | 0x00  | 0.50125  | 0x25  | 0.7325   | 0x4A  | 0.96375  | 0x6F  | 1.195    | 0x94  |  |  |

| 0.27625               | 0x01  | 0.5075   | 0x26  | 0.73875  | 0x4B  | 0.97     | 0x70  | 1.20125  | 0x95  |  |  |

| 0.2825                | 0x02  | 0.51375  | 0x27  | 0.745    | 0x4C  | 0.97625  | 0x71  | 1.2075   | 0x96  |  |  |

| 0.28875               | 0x03  | 0.52     | 0x28  | 0.75125  | 0x4D  | 0.9825   | 0x72  | 1.21375  | 0x97  |  |  |

| 0.295                 | 0x04  | 0.52625  | 0x29  | 0.7575   | 0x4E  | 0.98875  | 0x73  | 1.22     | 0x98  |  |  |

| 0.30125               | 0x05  | 0.5325   | 0x2A  | 0.76375  | 0x4F  | 0.995    | 0x74  | 1.22625  | 0x99  |  |  |

| 0.3075                | 0x06  | 0.53875  | 0x2B  | 0.77     | 0x50  | 1.00125  | 0x75  | 1.2325   | 0x9A  |  |  |

| 0.31375               | 0x07  | 0.545    | 0x2C  | 0.77625  | 0x51  | 1.0075   | 0x76  | 1.23875  | 0x9B  |  |  |

| 0.32                  | 0x08  | 0.55125  | 0x2D  | 0.7825   | 0x52  | 1.01375  | 0x77  | 1.245    | 0x9C  |  |  |

| 0.32625               | 0x09  | 0.5575   | 0x2E  | 0.78875  | 0x53  | 1.02     | 0x78  | 1.25125  | 0x9D  |  |  |

| 0.3325                | 0x0A  | 0.56375  | 0x2F  | 0.795    | 0x54  | 1.02625  | 0x79  | 1.2575   | 0x9E  |  |  |

| 0.33875               | 0x0B  | 0.57     | 0x30  | 0.80125  | 0x55  | 1.0325   | 0x7A  | 1.26375  | 0x9F  |  |  |

| 0.345                 | 0x0C  | 0.57625  | 0x31  | 0.8075   | 0x56  | 1.03875  | 0x7B  | 1.27     | 0xA0  |  |  |

| 0.35125               | 0x0D  | 0.5825   | 0x32  | 0.81375  | 0x57  | 1.045    | 0x7C  | 1.27625  | 0xA1  |  |  |

| 0.3575                | 0x0E  | 0.58875  | 0x33  | 0.82     | 0x58  | 1.05125  | 0x7D  | 1.2825   | 0xA2  |  |  |

| 0.36375               | 0x0F  | 0.595    | 0x34  | 0.82625  | 0x59  | 1.0575   | 0x7E  | 1.28875  | 0xA3  |  |  |

| 0.37                  | 0x10  | 0.60125  | 0x35  | 0.8325   | 0x5A  | 1.06375  | 0x7F  | 1.295    | 0xA4  |  |  |

| 0.37625               | 0x11  | 0.6075   | 0x36  | 0.83875  | 0x5B  | 1.07     | 0x80  | 1.30125  | 0xA5  |  |  |

| 0.3825                | 0x12  | 0.61375  | 0x37  | 0.845    | 0x5C  | 1.07625  | 0x81  | 1.3075   | 0xA6  |  |  |

| 0.38875               | 0x13  | 0.62     | 0x38  | 0.85125  | 0x5D  | 1.0825   | 0x82  | 1.31375  | 0xA7  |  |  |

| 0.395                 | 0x14  | 0.62625  | 0x39  | 0.8575   | 0x5E  | 1.08875  | 0x83  | 1.32     | 0xA8  |  |  |

| 0.40125               | 0x15  | 0.6325   | 0x3A  | 0.86375  | 0x5F  | 1.095    | 0x84  | 1.32625  | 0xA9  |  |  |

| 0.4075                | 0x16  | 0.63875  | 0x3B  | 0.87     | 0x60  | 1.10125  | 0x85  | 1.3325   | 0xAA  |  |  |

| 0.41375               | 0x17  | 0.645    | 0x3C  | 0.87625  | 0x61  | 1.1075   | 0x86  | 1.33875  | 0xAB  |  |  |

| 0.42                  | 0x18  | 0.65125  | 0x3D  | 0.8825   | 0x62  | 1.11375  | 0x87  | 1.345    | 0xAC  |  |  |

| 0.42625               | 0x19  | 0.6575   | 0x3E  | 0.88875  | 0x63  | 1.12     | 0x88  | 1.35125  | 0xAD  |  |  |

| 0.4325                | 0x1A  | 0.66375  | 0x3F  | 0.895    | 0x64  | 1.12625  | 0x89  | 1.3575   | 0xAE  |  |  |

| 0.43875               | 0x1B  | 0.67     | 0x40  | 0.90125  | 0x65  | 1.1325   | 0x8A  | 1.36375  | 0xAF  |  |  |

| 0.445                 | 0x1C  | 0.67625  | 0x41  | 0.9075   | 0x66  | 1.13875  | 0x8B  | 1.37     | 0xB0  |  |  |

| 0.45125               | 0x1D  | 0.6825   | 0x42  | 0.91375  | 0x67  | 1.145    | 0x8C  | 1.37625  | 0xB1  |  |  |

| 0.4575                | 0x1E  | 0.68875  | 0x43  | 0.92     | 0x68  | 1.15125  | 0x8D  | 1.3825   | 0xB2  |  |  |

| 0.46375               | 0x1F  | 0.695    | 0x44  | 0.92625  | 0x69  | 1.1575   | 0x8E  | 1.38875  | 0xB3  |  |  |

| 0.47                  | 0x20  | 0.70125  | 0x45  | 0.9325   | 0x6A  | 1.16375  | 0x8F  | 1.395    | 0xB4  |  |  |

| 0.47625               | 0x21  | 0.7075   | 0x46  | 0.93875  | 0x6B  | 1.17     | 0x90  | 1.40125  | 0xB5  |  |  |

| 0.4825                | 0x22  | 0.71375  | 0x47  | 0.945    | 0x6C  | 1.17625  | 0x91  |          |       |  |  |

| 0.48875               | 0x23  | 0.72     | 0x48  | 0.95125  | 0x6D  | 1.1825   | 0x92  |          |       |  |  |

| 0.495                 | 0x24  | 0.72625  | 0x49  | 0.9575   | 0x6E  | 1.18875  | 0x93  |          |       |  |  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

| Table 3. Register List |               |         |      |                  |  |  |  |  |  |  |

|------------------------|---------------|---------|------|------------------|--|--|--|--|--|--|

| Address                | Register Name | Default | Туре | Note             |  |  |  |  |  |  |

|                        |               | 0x55    |      | RT5744A/ RT5744B |  |  |  |  |  |  |

| 0,400                  | NSEL0         | 0x25    | RW   | RT5744C          |  |  |  |  |  |  |

| 0x00                   | INSELU        | 0x4D    | RVV  | RT5744D          |  |  |  |  |  |  |

|                        |               | 0x7D    |      | RT5746A          |  |  |  |  |  |  |

|                        |               | 0x65    |      | RT5744A/ RT5744B |  |  |  |  |  |  |

| 0.401                  |               | 0x35    |      | RT5744C          |  |  |  |  |  |  |

| 0x01                   | NSEL1         | 0x2D    | RW   | RT5744D          |  |  |  |  |  |  |

|                        |               | 0x65    |      | RT5746A          |  |  |  |  |  |  |

| 0x02                   | CONTROL1      | 0x90    | RW   |                  |  |  |  |  |  |  |

| 0x03                   | ID1           | 0x01    | RO   |                  |  |  |  |  |  |  |

| 0x04                   | ID2           | 0x00    | RO   |                  |  |  |  |  |  |  |

| 0x05                   | MONITOR       | 0x00    | RO   |                  |  |  |  |  |  |  |

| 0x06                   | CONTROL2      | 0x63    | RW   | All devices.     |  |  |  |  |  |  |

| 0x07                   | CONTROL3      | 0x00    | RW   |                  |  |  |  |  |  |  |

| 0x08                   | CONTROL4      | 0x00    | RW   |                  |  |  |  |  |  |  |

| 0x0A                   | CONTROL5      | 0x00    | RW   |                  |  |  |  |  |  |  |

#### Table 4. NSEL0

| Address: 0 | x00 |       |   |   |   |   |   |   |  |  |  |  |

|------------|-----|-------|---|---|---|---|---|---|--|--|--|--|

| Bit        | 7   | 6     | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

| Field      |     | VSEL0 |   |   |   |   |   |   |  |  |  |  |

| RT5744A    | 0   | 1     | 0 | 1 | 0 | 1 | 0 | 1 |  |  |  |  |

| RT5744B    | 0   | 1     | 0 | 1 | 0 | 1 | 0 | 1 |  |  |  |  |

| RT5744C    | 0   | 0     | 1 | 0 | 0 | 1 | 0 | 1 |  |  |  |  |

| RT5744D    | 0   | 1     | 0 | 0 | 1 | 1 | 0 | 1 |  |  |  |  |

| RT5746A    | 0   | 1     | 1 | 1 | 1 | 1 | 0 | 1 |  |  |  |  |

| Туре       |     | RW    |   |   |   |   |   |   |  |  |  |  |

| Bit | Name | Description                                                                                                                                                                     |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | VID Table satisfy (activate when the VSEL pin set to logic-low):<br>SEL[7:0] = 10110101: VOUT = 1.40125V<br><br>SEL[7:0] = 0000000:VOUT = 0.27V<br>6.25mV step for 0.27~1.40125 |

### Copyright © 2024 Richtek Technology Corporation. All rights reserved.

Table 5. NSEL1

| Address: 0 | x01 |   |   |     |     |   |   |   |  |

|------------|-----|---|---|-----|-----|---|---|---|--|

| Bit        | 7   | 6 | 5 | 4   | 3   | 2 | 1 | 0 |  |

| Field      |     |   |   | VSI | EL1 |   |   |   |  |

| RT5744A    | 0   | 1 | 1 | 0   | 0   | 1 | 0 | 1 |  |

| RT5744B    | 0   | 1 | 1 | 0   | 0   | 1 | 0 | 1 |  |

| RT5744C    | 0   | 0 | 1 | 1   | 0   | 1 | 0 | 1 |  |

| RT5744D    | 0   | 0 | 1 | 0   | 1   | 1 | 0 | 1 |  |

| RT5746A    | 0   | 1 | 1 | 0   | 0   | 1 | 0 | 1 |  |

| Туре       | RW  |   |   |     |     |   |   |   |  |

| Bit | Name  | Description                                                                                                                                                                                              |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | VSEL1 | VID Table satisfy (activate when the VSEL pin set to logic-high):<br>SEL[7:0] = 10110101: V <sub>OUT</sub> = 1.40125V<br><br>SEL[7:0] = 0000000:V <sub>OUT</sub> = 0.27V<br>6.25mV step for 0.27~1.40125 |

#### Table 6. CONTROL1

| Address: 0 | Address: 0x02 |   |       |   |          |          |                |                |  |  |  |  |

|------------|---------------|---|-------|---|----------|----------|----------------|----------------|--|--|--|--|

| Bit        | 7             | 6 | 5     | 4 | 3        | 2        | 1              | 0              |  |  |  |  |

| Field      | DISCHG        |   | UP_SR |   | Reserved | SW_RESET | MODE_VSEL<br>1 | MODE_VSEL<br>0 |  |  |  |  |

| Default    | 1             | 0 | 0     | 1 | 0        | 0        | 0              | 0              |  |  |  |  |

| Туре       | RW            |   | RW    |   | RV       | RW       | RW             | RW             |  |  |  |  |

| Bit | Name       | Description                                                                                                                                                                                                                      |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DISCHG     | 0: Disable internal output discharge resistor<br>1: Enable internal output discharge resistor                                                                                                                                    |

| 6:4 | UP_SR      | DVS Speed for UP DVS<br>$000 = 25mV/\mu s$<br>$001 = 12.5mV/\mu s$<br>$010 = 6.25mV/\mu s$<br>$011 = 3.125mV/\mu s$<br>$100 = 1.5625mV/\mu s$<br>$101 = 0.78125mV/\mu s$<br>$110 = 0.39065mV/\mu s$<br>$111 = 0.1953125mV/\mu s$ |

| 3   | Reserved   | Reserved bits                                                                                                                                                                                                                    |

| 2   | SW_RESET   | Write 1 to reset, always read 0                                                                                                                                                                                                  |

| 1   | MODE_VSEL1 | Mode control (activate when the VSEL pin set to logic-high):<br>1: Forced PWM mode<br>0: Auto PFM/PWM mode                                                                                                                       |

| 0   | MODE_VSEL0 | Mode control (activate when the VSEL pin set to logic-low):<br>1: Forced PWM mode<br>0: Auto PFM/PWM mode                                                                                                                        |

Copyright © 2024 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

## RT5744/RT5746

Table 7. ID1

| Address: 0 | Address: 0x03 |   |   |          |        |   |   |   |  |  |  |

|------------|---------------|---|---|----------|--------|---|---|---|--|--|--|

| Bit        | 7             | 6 | 5 | 4        | 3      | 2 | 1 | 0 |  |  |  |

| Field      | VENDOR_ID     |   |   | Reserved | DIE_ID |   |   |   |  |  |  |

| Default    | 0             | 0 | 0 | 0        | 0      | 0 | 0 | 1 |  |  |  |

| Туре       | RO            |   |   | RV       |        | R | 0 |   |  |  |  |

| Bit | Name      | Description   |

|-----|-----------|---------------|

| 7:5 | VENDOR_ID | Vendor_ID     |

| 4   | Reserved  | Reserved bits |

| 3:0 | DIE_ID    | DIE_ID        |

#### Table 8. ID2

| Address: 0 | Address: 0x04 |      |       |   |         |   |   |   |  |  |  |  |

|------------|---------------|------|-------|---|---------|---|---|---|--|--|--|--|

| Bit        | 7             | 6    | 5     | 4 | 3       | 2 | 1 | 0 |  |  |  |  |

| Field      |               | Rese | erved |   | DIE_REV |   |   |   |  |  |  |  |

| Default    | 0             | 0    | 0     | 0 | 0       | 0 | 0 | 0 |  |  |  |  |

| Туре       |               | R    | ۲V    |   |         | R | 0 |   |  |  |  |  |

| Bit | Name     | Description   |  |  |  |  |

|-----|----------|---------------|--|--|--|--|

| 7:4 | Reserved | Reserved bits |  |  |  |  |

| 3:0 | DIE_REV  | Revision_ID   |  |  |  |  |

#### Table 9. MONITOR

| Address: 0 | Address: 0x05 |      |    |     |     |                |    |             |  |  |  |  |  |

|------------|---------------|------|----|-----|-----|----------------|----|-------------|--|--|--|--|--|

| Bit        | 7             | 6    | 5  | 4   | 3   | 2              | 1  | 0           |  |  |  |  |  |

| Field      | PG            | UVLO | OV | POS | NEG | RESET_STA<br>T | ОТ | BUCK_STATUS |  |  |  |  |  |

| Default    | 0             | 0    | 0  | 0   | 0   | 0              | 0  | 0           |  |  |  |  |  |

| Туре       | RO            | RO   | RO | RO  | RO  | RO             | RO | RO          |  |  |  |  |  |

| Bit | Name        | Description                                                  |  |  |  |

|-----|-------------|--------------------------------------------------------------|--|--|--|

| 7   | PG          | 1: Buck is enabled and soft-start is completed.              |  |  |  |

| 6   | UVLO        | 1: Signifies the VIN is less than the UVLO threshold.        |  |  |  |

| 5   | OV          | 1: Signifies the VIN is greater than the input OV threshold. |  |  |  |

| 4   | POS         | 1: Signifies a positive voltage transition is in progress    |  |  |  |

| 3   | NEG         | 1: Signifies a negative voltage transition is in progress    |  |  |  |

| 2   | RESET_STAT  | 1: Indicates that a register reset was performed.            |  |  |  |

| 1   | ОТ          | 1: Signifies the thermal shutdown is active.                 |  |  |  |

| 0   | BUCK_STATUS | 1: Buck enabled; 0: buck disabled.                           |  |  |  |

#### Table 10. CONTROL2

| Address: 0x06 |   |       |   |          |       |   |          |          |  |  |  |

|---------------|---|-------|---|----------|-------|---|----------|----------|--|--|--|

| Bit           | 7 | 6     | 5 | 4        | 3     | 2 | 1        | 0        |  |  |  |

| Field         |   | DN_SR |   | Reserved | SS_SR |   | EN_VSEL1 | EN_VSEL0 |  |  |  |

| Default       | 0 | 1     | 1 | 0        | 0     | 0 | 1        | 1        |  |  |  |

| Туре          |   | RW    |   | RV       | R     | W | RW       | RW       |  |  |  |

| Bit | Name     | Description                                                                                                                                                                                                                      |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | DN_SR    | DVS Speed for DN DVS<br>$000 = 25mV/\mu s$<br>$001 = 12.5mV/\mu s$<br>$010 = 6.25mV/\mu s$<br>$011 = 3.125mV/\mu s$<br>$100 = 1.5625mV/\mu s$<br>$101 = 0.78125mV/\mu s$<br>$110 = 0.39065mV/\mu s$<br>$111 = 0.1953125mV/\mu s$ |

| 4   | Reserved | Reserved bits                                                                                                                                                                                                                    |

| 3:2 | SS_SR    | DVS Speed for soft-start DVS<br>$00 = 10 \text{mV}/\mu \text{s}$<br>$01 = 5 \text{mV}/\mu \text{s}$<br>$10 = 2.5 \text{mV}/\mu \text{s}$<br>$11 = 1.25 \text{mV}/\mu \text{s}$                                                   |

| 1   | EN_VSEL1 | Software power-on/off control register (activate when the VSEL pin set to logic-high):<br>0: Disable output<br>1: Enable output                                                                                                  |

| 0   | EN_VSEL0 | Software power-on/off control register (activate when the VSEL pin set to logic-low):<br>0: Disable output<br>1: Enable output                                                                                                   |

#### Table 11. CONTROL3