**RT1988**

### 53V/8A Ideal Diode Protection Switch

### 1 General Description

The RT1988 provides an ideal diode reverse current blocking function with low forward voltage and an enable input for disconnection. The 3.4V to 53V input operating range and 8A continuous current rating make the RT1988 well suited for multi-port USB-C sink current applications. In addition, this part includes a 60V Absolute Maximum Rating (AMR), a 20A peak current rating (up to 10ms), undervoltage-lockout, overvoltage protection, and over-temperature protection.

An adjustable soft-start circuit sets the output voltage slew rate and manages inrush current into high capacitance loads. Short-circuit protection is provided during this period, while the integrated MOSFET provides a low forward voltage drop and high Safe Operating Area (SOA).

The RT1988 is available in a VDFN-20TL 5.2x4 package and can operate over -40°C to 125°C junction temperature.

### 2 Features

- 8A Continuous/20A Peak Current Capability

- Input Supply Voltage: 3.4V to 53V

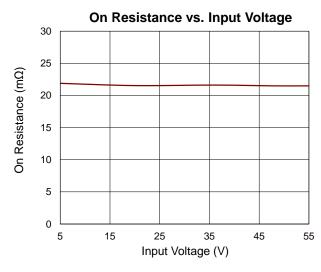

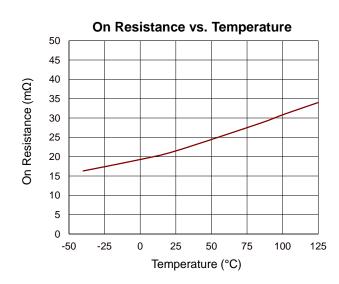

- 20mΩ (Typical) Ron

- Analog Ideal Diode Gate Control

- Blocks Reverse Current

- · Avoids Switch Chatter

- Enables Fast Power Swap

- Programmable Soft-Start

- Programmable Overvoltage Protection

- Over-Temperature Protection

- Start-Up Short-Circuit Protection

- Compliance with IEC61000-4-2 and IEC61000-4-5 Standards

### 3 Applications

- USB-C/Thunderbolt Sink Power Delivery

- Notebooks Computer Barrel Jack

- Docking Stations

- Power ORing Applications

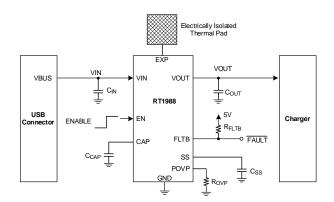

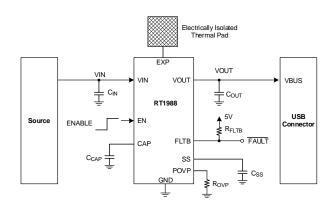

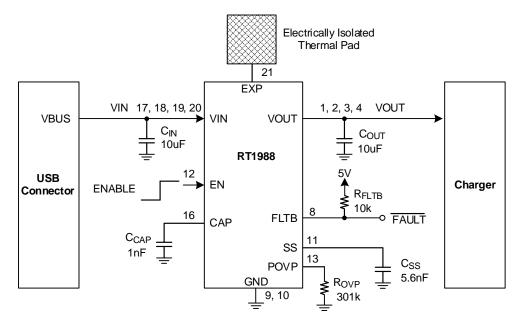

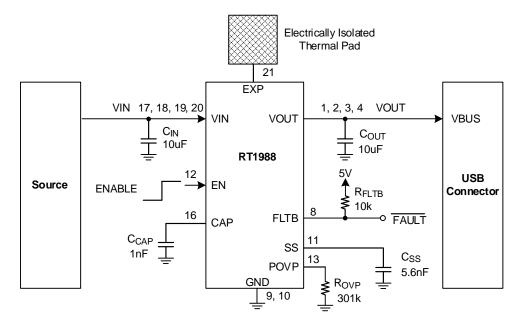

# 4 Simplified Application Circuit

### **Current Sinking Application**

### **Current Sourcing Application**

RICHTEK

### **5 Ordering Information**

# RT1988 □-□ Packing B: Customized Tape and Reel Size Package Type<sup>(1)</sup> N: VDFN-20TL 5.2x4 (V-Type)

## **6 Marking Information**

20=: Product Code YMDAN: Date Code

#### Note 1.

Richtek products are Richtek Green Policy compliant and marked with (1) indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

#### **Ideal Diode Protection Switch Selection Table**

| Р | art Number | Input Supply<br>Voltage | Continuous<br>Current<br>Capability | OVP Threshold | Package         |

|---|------------|-------------------------|-------------------------------------|---------------|-----------------|

|   | RT1985     | 3.4V to 23V             | 8A                                  | Fixed         | VDFN-12TL 3x3   |

|   | RT1986     | 3.4V to 23V             | 5.5A                                | Fixed         | VDFN-12TL 3x3   |

|   | RT1987     | 3.4V to 32V             | 8A                                  | Programmable  | VDFN-12T1L 3x3  |

|   | RT1988     | 3.4V to 53V             | 8A                                  | Programmable  | VDFN-20TL 5.2x4 |

### **Table of Contents**

| 1  | Gene   | rai Description 1                         |

|----|--------|-------------------------------------------|

| 2  |        | res1                                      |

| 3  | Appli  | cations 1                                 |

| 4  |        | ified Application Circuit 1               |

| 5  | Order  | ing Information 2                         |

| 6  | Marki  | ng Information2                           |

| 7  | Pin C  | onfiguration 4                            |

| 8  |        | ional Pin Description 4                   |

| 9  | Funct  | ional Block Diagram 5                     |

| 10 | Abso   | ute Maximum Ratings 6                     |

| 11 | ESD F  | Ratings 6                                 |

| 12 | Reco   | mmended Operating Conditions 6            |

| 13 | Electr | rical Characteristics7                    |

| 14 | Typic  | al Application Circuit9                   |

|    | 14.1   | Current Sinking Application9              |

|    | 14.2   | Current Sourcing Application9             |

| 15 | Timin  | g Diagram10                               |

| 16 | Opera  | ation11                                   |

|    | 16.1   | Enable (EN and UVLO)15                    |

|    | 16.2   | Power Delivery and Soft-Start15           |

|    | 16.3   | Soft-start Slew Rate Control16            |

|    | 16.4   | Fault Protection16                        |

|    | 16.5   | Start-up Short-circuit Protection (SCP)17 |

|    | 16.6   | Ideal Diode True Reverse Current          |

|    |        | Blocking (TRCB)17                         |

|    | 16.7   | Overvoltage Protection (OVP)18            |

|    | 16.8   | Overtemperature Protection (OTP)18        |

| 17 | Appli               | cation information                 | 1  |  |  |  |

|----|---------------------|------------------------------------|----|--|--|--|

|    | 17.1                | Input Capacitor Selection          | 19 |  |  |  |

|    | 17.2                | Output Capacitor Selection         | 19 |  |  |  |

|    | 17.3                | Thermal Considerations             | 19 |  |  |  |

| 18 | Outlin              | ne Dimension                       | 2  |  |  |  |

| 19 | Footp               | rint Information                   | 22 |  |  |  |

| 20 | Packing Information |                                    |    |  |  |  |

|    | 20.1                | Tape and Reel Data                 | 2  |  |  |  |

|    | 20.2                | Tape and Reel Packing              | 2  |  |  |  |

|    | 20.3                | Packing Material Anti-ESD Property | 2  |  |  |  |

| 21 | Datas               | heet Revision History              | 2  |  |  |  |

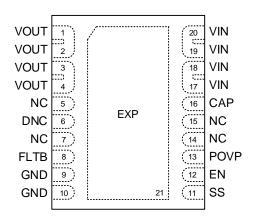

# 7 Pin Configuration

(TOP VIEW)

VDFN-20TL 5.2x4

### **8 Functional Pin Description**

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                      |

|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4       | VOUT     | Output voltage. Connect to the load.                                                                                                                                                                                                                                                                                              |

| 5, 7, 14, 15     | NC       | No Connect.                                                                                                                                                                                                                                                                                                                       |

| 6                | DNC      | Do Not Connect. Internally connected to the Exposed Pad (EXP).                                                                                                                                                                                                                                                                    |

| 8                | FLTB     | Open-drain fault indicator. Connect a pull-up resistor to a low-voltage supply. This pin pulls low if a fault condition is detected.                                                                                                                                                                                              |

| 9, 10            | GND      | Ground.                                                                                                                                                                                                                                                                                                                           |

| 11               | SS       | Soft-start input. Connect a capacitor, Css, from SS to GND to set the soft-start time.                                                                                                                                                                                                                                            |

| 12               | EN       | Enable active high. Pull high to enable the ideal diode function. Pull low to disconnect VIN from VOUT.                                                                                                                                                                                                                           |

| 13               | POVP     | Programmable Overvoltage Protection threshold setting. Connect a resistor between this pin and GND to set the OVP threshold. Do not apply a direct DC voltage to this pin.                                                                                                                                                        |

| 16               | CAP      | Connect a 1nF capacitor to GND.                                                                                                                                                                                                                                                                                                   |

| 17, 18, 19, 20   | VIN      | Input voltage. Connect to a power input and bypass with a $10 \mu F$ capacitor to GND.                                                                                                                                                                                                                                            |

| 21 (Exposed Pad) | EXP      | Exposed pad. The exposed pad is electrically connected to the commondrain node of the internal power MOSFET and must be electrically isolated. For improved thermal performance, this pad should be soldered to a large electrically isolated pad and tied to as much copper (electrically isolated) as possible using many vias. |

RT1988\_DS-00T01

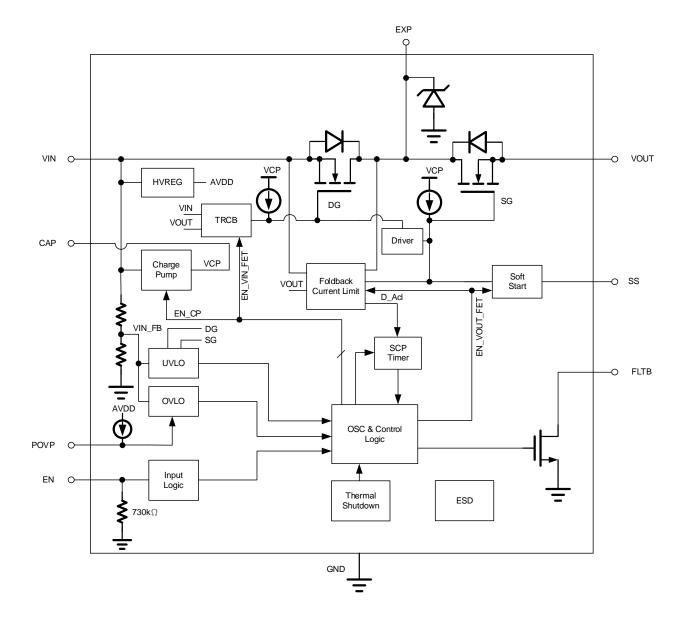

# 9 Functional Block Diagram

VIN\_VOUT to GND

### 10 Absolute Maximum Ratings

(Note 2)

| - | 7111, 1001 100112 |               |

|---|-------------------|---------------|

|   | DC                | -0.3V to +56V |

|   | <800µs            | +60V          |

- Power Dissipation, PD @ TA = 25°C

VDFN-20TL 5.2x4 ------ 3.08W

• Package Thermal Resistance (Note 3)

VDFN-20TL 5.2x4, θJA ------ 32.43°C/W VDFN-20TL 5.2x4, θJC ------ 0.28°C/W

- Lead Temperature (Soldering, 10 sec.) ------ 260°C

- Junction Temperature ------ 150°C

- Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3. θ<sub>JA</sub> is measured under natural convection (still air) at T<sub>A</sub> = 25°C with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

## 11 ESD Ratings

(Note 4)

- HBM (Human Body Model) All Pins -----±2kV

- IEC 61000-4-2 at VIN and VOUT ------ ±8kV

- IEC 61000-4-5 at VIN no CAP------20A (8/20µs)

Note 4. Devices are ESD sensitive. Handling precautions are recommended.

# 12 Recommended Operating Conditions

(Note 5)

- Supply Input Voltage, VIN ----- 3.4V to 53V

- EN, FLTB ------ 0V to 5.5V

- CAP ------ 0V to 65V

- SS, POVP ------ 0V to 3V • IVIN, IVOUT------- 0A to 8A

- Peak IVIN, IVOUT for 10ms at 2% Duty Cycle ----- 20A

Note 5. The device is not guaranteed to function outside its operating conditions.

RT1988 DS-00T01

### 13 Electrical Characteristics

$(V_{IN}=48V,\,V_{EN}=5V,\,C_{IN}=10\mu\text{F},\,C_{OUT}=10\mu\text{F},\,C_{SS}=5.6\text{nF},\,T_{A}=T_{J}=25^{\circ}\text{C},\,\text{unless otherwise noted.})$

| Parameter                                 | Symbol         | Test Conditions                                                  | Min  | Тур | Max  | Unit |

|-------------------------------------------|----------------|------------------------------------------------------------------|------|-----|------|------|

| General                                   |                |                                                                  |      | I   |      |      |

| Input Voltage Range                       | Vin            |                                                                  | 3.4  |     | 53   | V    |

| Transient Clamp Voltage                   | VIN_TVS        |                                                                  |      | 60  |      | V    |

| Input Undervoltage-<br>Lockout            | VIN_UVLO       | VIN rising                                                       | 2.9  |     | 3.35 | V    |

| UVLO Hysteresis                           | Vuvlo_HYS      |                                                                  |      | 250 |      | mV   |

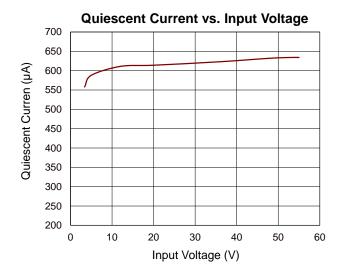

| Input Quiescent Current                   | IQ             | IOUT = 0A, VIN = 48V                                             |      | 550 | 800  | μΑ   |

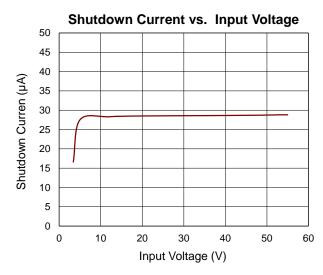

| Input Shutdown Current                    | ISHDN          | IOUT = 0A, VIN = 48V, EN = 0V                                    |      |     | 120  | μΑ   |

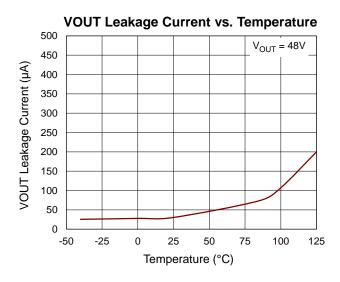

| Output Leakage Current                    | IOUT_LK        | Vout = 48V, Vin = 0V, EN = 0V                                    |      |     | 100  | μΑ   |

| Owitals On Designation                    | RON_48V        | VIN = 48V, IOUT = 1A ( <u>Note 6</u> )                           |      | 20  |      | 0    |

| Switch On Resistance                      | Ron_5V         | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 1A ( <u>Note 6</u> )    |      | 22  |      | mΩ   |

| Enable Input Rising<br>Threshold          | VEN_R          | EN rising                                                        |      |     | 1.4  | ٧    |

| Enable Input Falling<br>Threshold         | VEN_F          | EN falling                                                       | 0.4  |     |      | V    |

| Enable Input Pull-Down Resistance         | REN_PD         | EN rising                                                        | 475  | 730 | 985  | kΩ   |

| FLTB Pull-Down Voltage                    | VFLTB_PD       | IFLTB = -3mA                                                     |      |     | 0.3  | V    |

| Input Overvoltage Protect                 | ction          |                                                                  |      | l   |      |      |

|                                           |                | POVP > 1.3V (ROVP > 260k $\Omega$ ), V <sub>IN</sub> rising      | 56   | 58  | 60   |      |

| Overvoltage Protection<br>Threshold       | Vovp_r         | 0.85V < POVP < 1.1V (170kΩ < ROVP < 220kΩ), VIN rising 41.7 43.5 |      |     |      | V    |

|                                           |                | POVP < 0.6V (ROVP < $120k\Omega$ ), VIN rising                   | 32.3 | 34  | 35.7 |      |

| POVP Current                              | IPOVP          |                                                                  |      | 5   |      | μΑ   |

| Overvoltage Protection Blanking Time      | tBLK_OVP       |                                                                  |      | 512 |      | μS   |

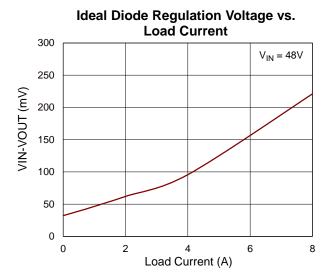

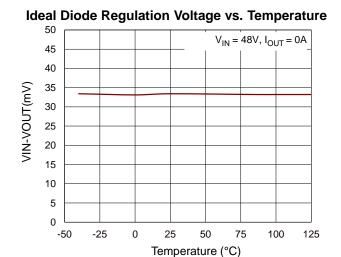

| Ideal Diode (Reverse Cur                  | rrent Blocking | 1)                                                               |      |     |      |      |

| Ideal Diode Forward<br>Regulation Voltage | VFWD           | VIN – VOUT, IOUT < 1A                                            |      | 35  |      | mV   |

| Fast Reverse Current<br>Threshold         | VFRC           | VIN - VOUT fast turn off                                         |      | -50 |      | mV   |

| Fast Reverse Current<br>Delay Time        | tFRC           |                                                                  |      | 0.6 |      | μS   |

| <b>Dynamic Timing Charact</b>             | eristics       |                                                                  |      |     |      |      |

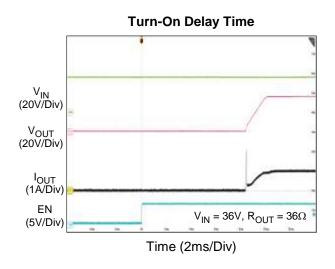

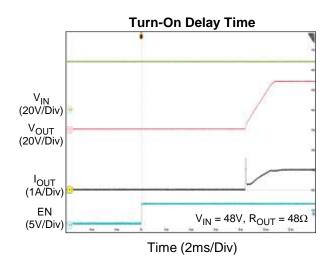

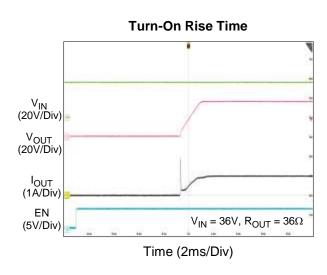

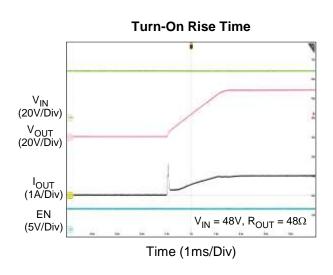

| Turn-On Delay Time                        | td_on          | From EN rising edge to VOUT reaching 10% of VIN                  |      | 8   |      | ms   |

| Turn-On Rise Time                         | ton            | VOUT from 10% to 90%                                             |      | 2   |      | ms   |

| Short-Circuit Protection<br>Restart Time  | tscp_rst       | During soft-start.                                               |      | 64  |      | ms   |

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

RT1988\_DS-00T01 August 2025

# **RT1988**

| Parameter                                 | Symbol | Test Conditions                                                 | Min | Тур  | Max | Unit |

|-------------------------------------------|--------|-----------------------------------------------------------------|-----|------|-----|------|

| Over-Temperature Protection               |        |                                                                 |     |      |     |      |

| Over-Temperature<br>Protection Threshold  | Тотр   | Non-latch off                                                   |     | 150  | -   | °C   |

| Start-Up Short-Circuit Protection         |        |                                                                 |     |      |     |      |

|                                           |        | VIN = 48V, VOUT = 0V, during start-up.                          |     | 2    |     |      |

| Short-Circuit Protection<br>Current Limit | ISCP   | V <sub>IN</sub> = 48V, V <sub>OUT</sub> = 20V, during start-up. |     | 10.5 | 1   | Α    |

|                                           |        | VIN = 48V, VOUT = 47V, during start-up.                         |     | 15   | 1   |      |

| Short-Circuit Protection Timeout          | tSCP   |                                                                 |     | 256  | ı   | μS   |

Note 6. R<sub>ON</sub> is tested at 1A in test mode to bypass ideal diode regulation.

## 14 Typical Application Circuit

### 14.1 Current Sinking Application

#### 14.2 Current Sourcing Application

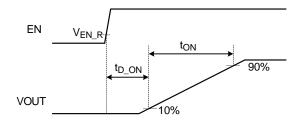

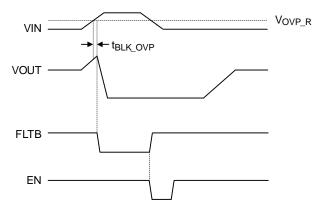

# 15 Timing Diagram

Figure 1. Turn-On Delay Time and Turn-On Rise Time

Figure 2. Overvoltage Protection

## 16 Typical Operating Characteristics

RICHTEK is a registered trademark of Richtek Technology Corporation.

RT1988 DS-00T01

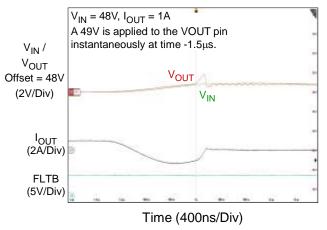

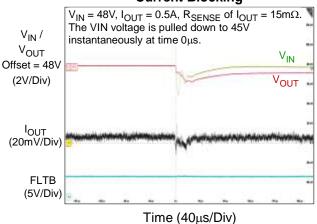

#### **Fast Reverse Current Blocking**

#### **Ideal Diode True Reverse Current Blocking**

#### Recovery of Ideal Diode True Reverse Current Blocking

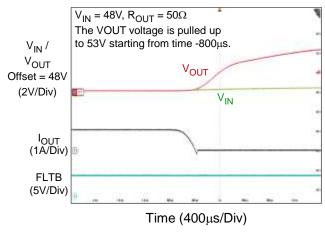

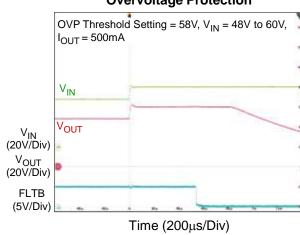

#### **Overvoltage Protection**

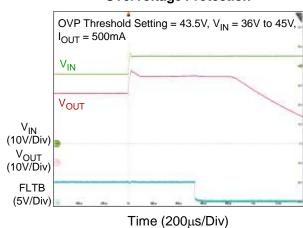

#### Overvoltage Protection

RICHTEK is a registered trademark of Richtek Technology Corporation.

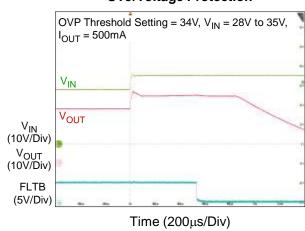

#### **Overvoltage Protection**

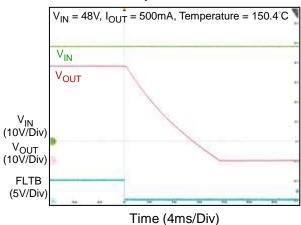

#### **Over-Temperature Protection**

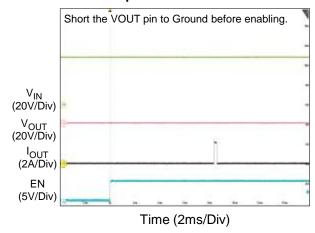

#### **Start-Up Short-Circuit Protection**

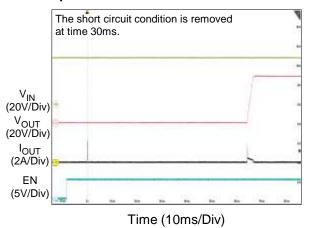

#### Start-Up Short-Circuit Protection Restart Time

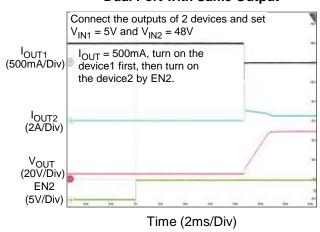

### **Dual Port with Same Output**

### 17 Operation

The RT1988 is a high-side protection device which is particularly well suited for USB-C sink applications. Its ideal diode functionality and back-to-back integrated  $20m\Omega$  MOSFETs provide reverse current blocking and diode-OR power source sharing while programmable soft-start, overvoltage, over-temperature, and short-circuit protection features protect the system from faults. The 3.4V to 53V operating range aligns with USB-C voltage levels as well as other common power supplies. Unlike single MOSFET devices, the RT1988 completely isolates VIN and VOUT when disabled using the EN input.

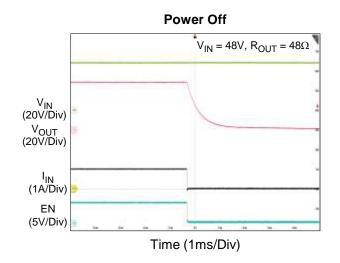

#### 17.1 Enable (EN and UVLO)

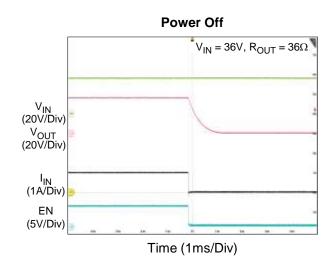

The active high EN pin provides on/off control for the power path while the input undervoltage-lockout (UVLO) circuit monitors the input voltage (VIN). When VIN > VIN\_UVLO (typically 3.175V), driving EN above VEN\_R (1.4V max) turns on the power path. The timing diagram is shown in <u>Figure 1</u>. Assuming no other faults – such as OVP or OTP – VOUT will start to ramp after tD\_ON (typically 8ms). VOUT ramps up to VIN with a 10% to 90% rise time of approximately ton as set by Css. See the <u>Soft-Start Slew Rate Control</u> section for more information.

Driving EN below VEN\_F (0.4Vmin) disables the power path and puts the RT1988 in a low quiescent current state, drawing just ISHDN (120 $\mu$ A maximum). A low input voltage (VIN < VIN\_UVLO - VUVLO\_HYS, typically 2.925V) also disables the power path.

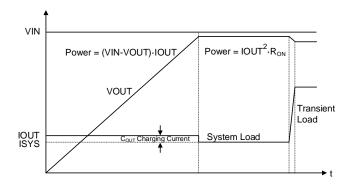

#### 17.2 Power Delivery and Soft-Start

When an input voltage is first applied to the RT1988, the voltage at VOUT ramps up linearly with a slope determined by the SS pin capacitance. During this time, which is typically a few milliseconds, the RT1988 has high internal MOSFET stress with a power dissipation equal to (VIN – VOUT) x IOUT, where IOUT is the sum of the system load current and the current required to charge the output capacitance. The internal power dissipation is calculated as follows:

Power =

$$(VIN - VOUT) \times IOUT = (VIN - VOUT) \times (ISYS + \frac{dVOUT}{dt} \times COUT)$$

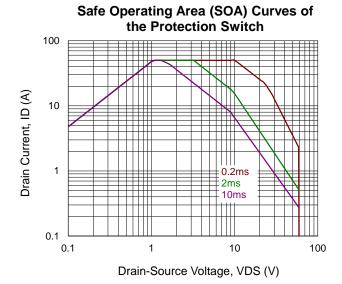

where ISYS is the system load current and Cout is the output capacitance. The internal MOSFET ability to survive this high-power scenario depends on the MOSFET's safe operating area (SOA), as illustrated in <u>Figure 4</u>, and the thermal performance of the package – with a soft-start time of just a few milliseconds, the thermal performance of the PCB does not play a significant role.

Figure 3. Soft-Start Power Dissipation

RICHTEK

Figure 4. Safe Operating Area (SOA) Curves of the Protection Switch

When the soft-start ramp is complete, the internal power device switches completely on (provided ISYS x Ron >  $V_{FWD}$ ) and acts like a resistor with resistance Ron. Because of the low differential voltage between VIN and VOUT, the power dissipation during this mode is considerably lower than during soft-start. Careful PCB layout consideration of thermal performance, combined with the low on-resistance of the internal power device, will ensure maximum system efficiency and minimal heat generation.

#### 17.3 Soft-Start Slew Rate Control

When the RT1988 is first enabled, the soft-start function limits the rate of rise on the internal gate of the power device to control the VOUT ramp and limit inrush current. An external capacitor, Css, on the SS pin programs the 10% to 90% ramp time, ton, as follows:

$ton = 7.44 \times Css \times Vin$

With Css in nF and ton in µs. To calculate Css:

$$C_{SS} = 0.134 \times \frac{t_{ON}}{V_{IN}}$$

#### 17.4 Fault Protection

The RT1988 provides protection against reverse current (TRCB), overvoltage (OVP), overtemperature (OTP), and short-circuit (OCP) faults. When the device is first enabled, if any of the following conditions exist, the internal power MOSFET will not turn on:

- 1. VIN VOUT < VFRC (typically -50mV)

- 2.  $VIN > VOVP_R$  (58V when POVP > 1.3V; 43.5V when 0.85V < POVP < 1.1V; 34V when POVP < 0.6V)

- 3. TDIE > TOTP (typically 150°C)

In addition, for conditions #2 (OVP) and #3 (OTP), the FLTB pin will be pulled low to indicate the fault status of the device. Note that a TRCB condition prevents the power device from turning on but does not result in a fault indication. The RT1988 continuously monitors these conditions to determine when to allow the power path to be enabled. See Table 1 for more information.

| Protection                              | Fault Response                                   | FLTB Status    |

|-----------------------------------------|--------------------------------------------------|----------------|

| Reverse Current (TRCB)                  | Auto-restart without soft-start at fault removal | High Impedance |

| Overvoltage Protection (OVP)            | Auto-restart with soft-start at fault removal    | Low            |

| Over-Temperature Protection (OTP)       | Auto-restart with soft-start at fault removal    | Low            |

| Start-Up Short-circuit Protection (SCP) | Auto-restart after tscp_Rst (typically 64 ms)    | Low            |

#### 17.5 Start-Up Short-Circuit Protection (SCP)

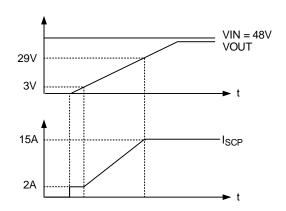

During the soft-start ramp (ton), the RT1988 monitors for short-circuit faults. If the output current, IOUT, exceeds ISCP during the soft-start ramp, the internal MOSFET will turn off. To maximize the power handling capability of the internal MOSFET within SOA, ISCP varies with VIN – VOUT. When the output voltage begins to start up, the initial value of the current limit is 2A. As the output voltage rises above 3V, the current limit starts to increase, with its value inversely proportional to VIN-VOUT, as shown in <a href="Figure 5">Figure 5</a>. A fixed timer is set to disable the power path if in-rush current is continuously clamped by the short-circuit current limit for 256µs. The timer resets if the in-rush current drops below the current limit. In the case of an output short-circuit, the RT1988 will disable the power path by turning off the internal MOSFET when the 256µs timer elapses. After tscP\_RsT (typically 64ms), the auto-retry mode will enable the power path and try to start up again. Both the SCP current limit and shutdown functions are disabled after ton (when the soft-start completes and the internal MOSFET is fully enhanced). Large output capacitors may require a longer soft-start time.

Figure 5. Short-Circuit Protection

#### 17.6 Ideal Diode True Reverse Current Blocking (TRCB)

When the power path is enabled, the ideal diode control circuitry attempts to regulate  $V_{IN} - V_{OUT} = V_{FWD}$  (typically 35 mV). Provided that  $I_{OUT} \times R_{ON} < V_{FWD}$ , the drive circuitry servos the internal gate drive to maintain this differential voltage. If the load current increases such that  $I_{OUT} \times R_{ON} > V_{FWD}$ , then the internal MOSFET is fully enhanced, and the VIN to VOUT voltage is determined by the load current and Ron. If VIN decreases (or VOUT increases) such that VIN – VOUT falls to less than  $V_{FWD}$ , the ideal diode gate drive will force the internal MOSFET off. The ideal diode control circuitry is designed to accommodate relatively slow changes in load conditions. In the case of a fast transient, the RT1988 includes a fast reverse current comparator that trips within tFRC (typically about  $0.6\mu s$ ) if VIN – VOUT falls below VFRC (typically –50mV).

RT1988 DS-00T01

#### 17.7 Overvoltage Protection (OVP)

The OVP circuit monitors the input voltage (VIN) for an overvoltage event to protect downstream loads. The OVP threshold can be set by connecting a resistor between the POVP pin and GND. When EN goes high and prior to the soft-start process, the POVP threshold setting will be latched. The POVP threshold remains unaffected by any subsequent changes. See <u>Table 2</u> for the POVP threshold setting.

When RT1988 detects an overvoltage event, the resulting behavior depends on the current state of the power path. If the power path is on, the internal power device will be switched off after the OVP blanking time (tblk\_ovp – typically 512µs). If the power path is off, OVP will prevent the internal power device from being turned on. In both cases the FLTB pin is pulled low indicating a fault condition. The RT1988 can be re-enabled by toggling the EN pin or when VIN falls below the OVP falling threshold (typically 1V lower than the OVP rising threshold).

**Table 2. Overvoltage Protection Threshold Setting**

| POVP Voltage        | OVP Threshold (Typical) |

|---------------------|-------------------------|

| POVP > 1.3V         | 58V                     |

| 0.85V < POVP < 1.1V | 43.5V                   |

| POVP < 0.6V         | 34V                     |

#### 17.8 Overtemperature Protection (OTP)

If the RT1988 die temperature reaches 150°C, the power path is disabled. The RT1988 can be re-enabled by toggling the EN pin or when the temperature falls below the OTP falling threshold (typically 110°C).

### 18 Application Information

(Note 7)

#### 18.1 Input Capacitor Selection

A quality input capacitor provides a low impedance at high frequency to reduce input voltage transients, supply fast load transients, and reduce high frequency noise. A  $10\mu F$  ceramic input capacitor is recommended and should be placed as close to the VIN and GND pins as possible.

#### 18.2 Output Capacitor Selection

While the RT1988 does not require a specific amount of output capacitance, the user should choose enough low ESR output capacitance to minimize high frequency output voltage transients due to dynamic loads.

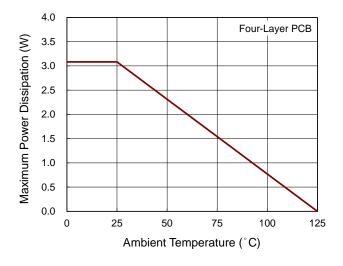

#### 18.3 Thermal Considerations

The junction temperature should never exceed the absolute maximum junction temperature T<sub>J(MAX)</sub>, listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_{A})/\theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a VDFN-20TL 5.2x4 package, the thermal resistance,  $\theta_{JA}$ , is 32.43°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated as below:

$PD(MAX) = (125^{\circ}C - 25^{\circ}C)/(32.43^{\circ}C/W) = 3.08W$  for a VDFN-20TL 5.2x4 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curve in <u>Figure 6</u> allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 6. Derating Curve of Maximum Power Dissipation

RICHTEK

Note 7. The information provided in this section is for reference only. The customer is solely responsible for the designing, validating, and testing your product incorporating Richtek's product and ensure such product meets applicable standards and any safety, security, or other requirements.

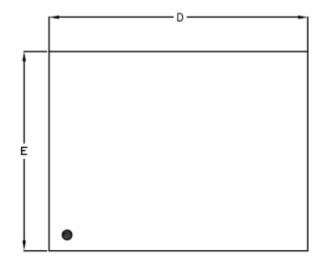

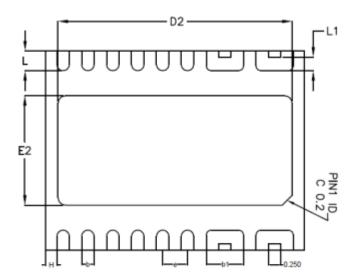

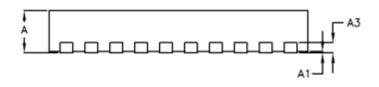

### 19 Outline Dimension

| Cumbal | Dimensions  | In Millimeters | Dimensions In Inches |       |  |  |

|--------|-------------|----------------|----------------------|-------|--|--|

| Symbol | Min         | Max            | Min                  | Max   |  |  |

| А      | 0.800       | 1.000          | 0.031                | 0.039 |  |  |

| A1     | 0.000       | 0.050          | 0.000                | 0.002 |  |  |

| A3     | 0.175       | 0.250          | 0.007                | 0.010 |  |  |

| b      | 0.200 0.300 |                | 0.008                | 0.012 |  |  |

| b1     | 0.700       | 0.700 0.800    |                      | 0.031 |  |  |

| D      | 5.150       | 5.250          | 0.203                | 0.207 |  |  |

| D2     | 4.650       | 4.750          | 0.183                | 0.187 |  |  |

| Е      | 3.950       | 4.050          | 0.156                | 0.159 |  |  |

| E2     | 2.150       | 2.250          | 0.085                | 0.089 |  |  |

| е      | 0.5         | 500            | 0.0                  | )20   |  |  |

| L      | 0.350       | 0.450          | 0.014                | 0.018 |  |  |

| L1     | 0.225       | 0.325          | 0.009                | 0.013 |  |  |

| Н      | 0.2         | 225            | 0.0                  | 009   |  |  |

V-Type 20TL DFN 5.2x4 Package

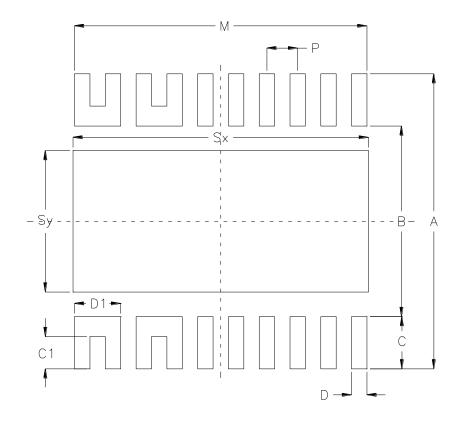

# 20 Footprint Information

|                     | Number  |       | Footprint Dimension (mm) |       |       |       |       |       |       |       |       | Tolerance |

|---------------------|---------|-------|--------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|

| Package             | of Pins | Р     | Α                        | В     | С     | C1    | D     | D1    | Sx    | Sy    | М     |           |

| V/W/U/XDFN5.2x4-20T | 20      | 0.500 | 4.800                    | 3.100 | 0.850 | 0.525 | 0.250 | 0.750 | 4.800 | 2.300 | 4.750 | ±0.05     |

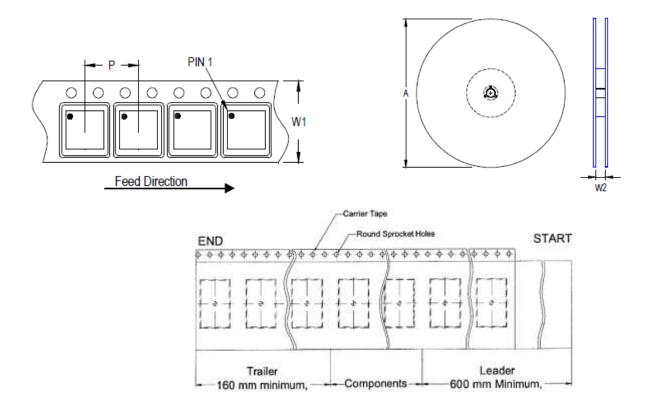

# 21 Packing Information

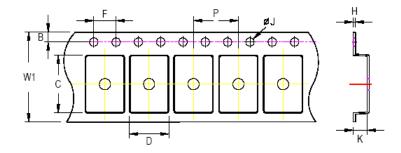

### 21.1 Tape and Reel Data

| Package Type               | Tape Size<br>(W1) (mm) | Pocket Pitch<br>(P) (mm) | Reel Si<br>(mm) | ze (A) | Units<br>per Reel | Trailer<br>(mm) | Leader<br>(mm) | Reel Width (W2)<br>Min/Max (mm) |

|----------------------------|------------------------|--------------------------|-----------------|--------|-------------------|-----------------|----------------|---------------------------------|

| (V, W)<br>QFN/DFN<br>5.2x4 | 12                     | 8                        | 330             | 13     | 2,500             | 160             | 600            | 12.4/14.4                       |

- C, D, and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tono Cizo | W1     | Р     |       | В      |        | F     |       | Ø٦    |       | K     |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max    | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.3mm | 0.6mm |

served. RICHTEK

is a registered trademark of Richtek Technology Corporation.

### 21.2 Tape and Reel Packing

| Step | Photo/Description                      | Step | Photo/Description                 |

|------|----------------------------------------|------|-----------------------------------|

| 1    | Reel 13"                               | 4    | 1 reel per inner box <b>Box G</b> |

| 2    | HIC & Desiccant (2 Unit) inside        | 5    | 6 inner boxes per outer box       |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                |

| Container          | Reel |       | Вох   |       |       | Carton   |       |        |

|--------------------|------|-------|-------|-------|-------|----------|-------|--------|

| Package            | Size | Units | Item  | Reels | Units | Item     | Boxes | Units  |

| (V, W) QFN and DFN | 13"  | 2,500 | Box G | 1     | 2,500 | Carton A | 6     | 15,000 |

| 5.2x4              | 13   | 2,500 | DOX G | '     | 2,500 | Carton A | 0     | 15,000 |

#### 21.3 Packing Material Anti-ESD Property

| Surface<br>Resistance     | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|---------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega$ /cm <sup>2</sup> | 10 <sup>4</sup> to 10 <sup>11</sup> |

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

RT1988 DS-00T01 August 2025 www.richtek.com

**RT1988**

22 Datasheet Revision History

| Version | Date      | Description   |

|---------|-----------|---------------|

| 00      | 2025/8/14 | First Edition |